英伟达GPU计算光刻技术使芯片制造性能大幅提升60倍,成功规避2nm及更小制程晶体管限制!

2024-03-19 12:23:06 EETOP英伟达去年发布了 cuLitho,现在又将生成式人工智能集成到了工作流程中,从而在已经取得的显著成果基础上再提升了 2 倍。总体而言,英伟达 声称 cuLitho 大大减少了各种繁重的计算光刻工作负载所需的时间,并且随着 Synopsys 将该技术集成到其软件工具中,它也可能会渗透到其他芯片制造商。

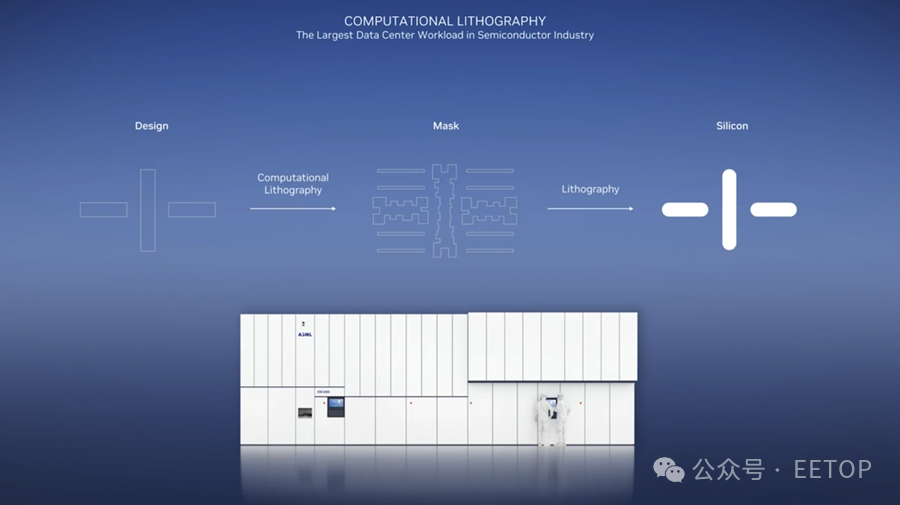

在芯片上打印纳米级特征需要一大块透明石英,称为光掩膜。石英上印有芯片设计的图案,其工作原理类似于模板。通过紫外线照射掩膜(称为曝光),可以将芯片设计蚀刻到晶圆上,从而形成构成现代芯片的数十亿个三维晶体管和导线结构。

早期的芯片制造工具使用单个光掩膜来曝光整个晶片,但新型芯片需要极高的分辨率,因此需要使用光掩膜和网罩来单独曝光芯片上的每颗芯片。每个芯片都需要多次曝光来分层构建芯片设计,芯片制造过程中使用的光掩膜数量因芯片而异,甚至可能超过 100 个掩膜。然而,由于该工具的刻录特征比曝光所用紫外线的波长更精细,新的问题又出现了。

特征的持续缩小导致了衍射问题,这基本上使打印到硅上的设计“模糊”。这些光学缺陷问题是由多种因素造成的,例如镜面曲率、化学特性和定位偏移等,需要采取缓解措施以确保设计打印时没有缺陷。

分辨率增强技术(RET)与计算光刻技术相结合,通过进行复杂的数学运算来优化掩模布局,使光线弯曲,从而使芯片制造商获得比以前更高的分辨率,从而解决清晰度问题。然而,这项任务的计算密集度越来越高,因为特征会进一步缩小,而且每种设计都会增加数十亿个晶体管,因此计算工作量会随着新一代芯片的推出而不断增加。

解决这一问题的关键在于创建更复杂的掩膜,但它们的复杂程度令人难以置信--例如,英特尔表示,其每个掩膜保存的数据量相当于 5 PB,即一部 IMAX 电影数据量的十倍。预计在未来几年内,高能超紫外和新技术(如采用曲线光罩的反向光刻技术(ILT))将使光罩的数据处理量增加 10 倍。

多光束写入器(一种新型掩模创建工具)的出现,可以更好地控制掩模制作过程,并实现更复杂的设计,例如曲线掩模中的设计。然而,这需要更密集的计算。英伟达 的 cuLitho 旨在将计算光刻工作负载转移到 GPU,并通过该公司的软件库减少完成任何给定工作负载所需的时间。

cuLitho 库可以集成到计算光刻软件中,该软件使用 ILT(曲线形状)、光学邻近校正(OCP,使用“曼哈顿”形状)和源掩模优化 (SMO) 来设计掩模。

现在 cuLitho 已采用生成式 AI 并已投入生产,英伟达已分享其测试结果,Manhattan 工作负载提升了 58 倍,曲线掩模设计速度提升了 45 倍,Nvopc 工作负载提升了 40 倍。

台积电目前在光罩制程中采用cuLitho,效果极佳;台积电首席执行官 CC Wei 博士表示:“我们与 英伟达合作,将 GPU 加速计算集成到台积电工作流程中,从而实现了性能的巨大飞跃、吞吐量的显着提高、周期时间的缩短以及功耗要求的降低。 我们正在将英伟达 cuLitho 投入台积电的生产,利用这种计算光刻技术来驱动半导体微缩的关键组件。”

Synopsys 总裁兼首席执行官 Sassine Ghazi 表示:“通过利用 AI 和加速计算的力量,将技术提升到新的水平。”

Synopsys和台积电是最先采用 cuLitho 的公司,但其他 EDA 和芯片制造公司也可以在掩模制造中使用该软件。从而缩短制造新掩模所需的时间,同时节省能耗并降低成本。

关键词: 计算光刻