现在半导体工艺制程已经来到了2纳米,但这主要是对于逻辑芯片而言。如果说有一种技术产品的微缩效果不太好的话,那就是 DRAM。造成这种情况的原因有很多,其中最重要的是 DRAM 单元的实际设计及其与制造的关系。但根据 泛林(Lam Research) 的说法,这些微缩困难的最终结果意味着 DRAM 领域的研究人员最早可能在五年后就无法提高 DRAM 的密度扩展。

正是在这种背景下,专门从事半导体电路设计的 Lam Research 发布了一份关于未来 DRAM 产品如何发展的提案。未来很可能是 3D 的,所以存储立方体的可能性似乎并不遥远。据该公司称,我们大约需要五到八年的时间才能设计出可制造的 3D DRAM 设备,这使得世界在 2D DRAM 微缩结束和 3D DRAM 微缩加速之间可能存在三年的差距。

使用他们专有的SEMulator3D通过软件,泛林研究公司迭代了可能的 3D DRAM 设计。他们的重点是解决缩放和层堆叠挑战、电容器和晶体管缩小、单元间连接和过孔阵列(例如台积电的 TSV [硅通孔],我们已经在其他 3D 半导体设计中看到过)。最后,该公司制定了实现其拟议设计的工艺要求。

由于 DRAM 单元的设计方式,不可能简单地将 2D DRAM 组件侧放,然后将它们堆叠在一起。发生这种情况是因为 DRAM 单元具有高纵横比(它们的高度大于厚度)。将它们侧放需要横向蚀刻(和填充)能力,这超出了我们目前的能力。

但是,当您了解架构本身时,您可以更改它并调整它,同时尝试绕过设计约束。然而,说起来容易做起来难,这就是我们还没有 3D DRAM 的原因。

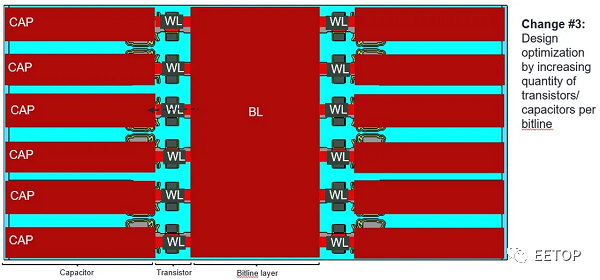

当前的 DRAM 电路设计本质上需要三个组件:位线(注入电流的导电结构);接收位线电流输出并充当控制电流是否流入(并填充)电路的栅极的晶体管;和一个电容器,流经位线和晶体管的电流最终以位(0或1)的形式存储。

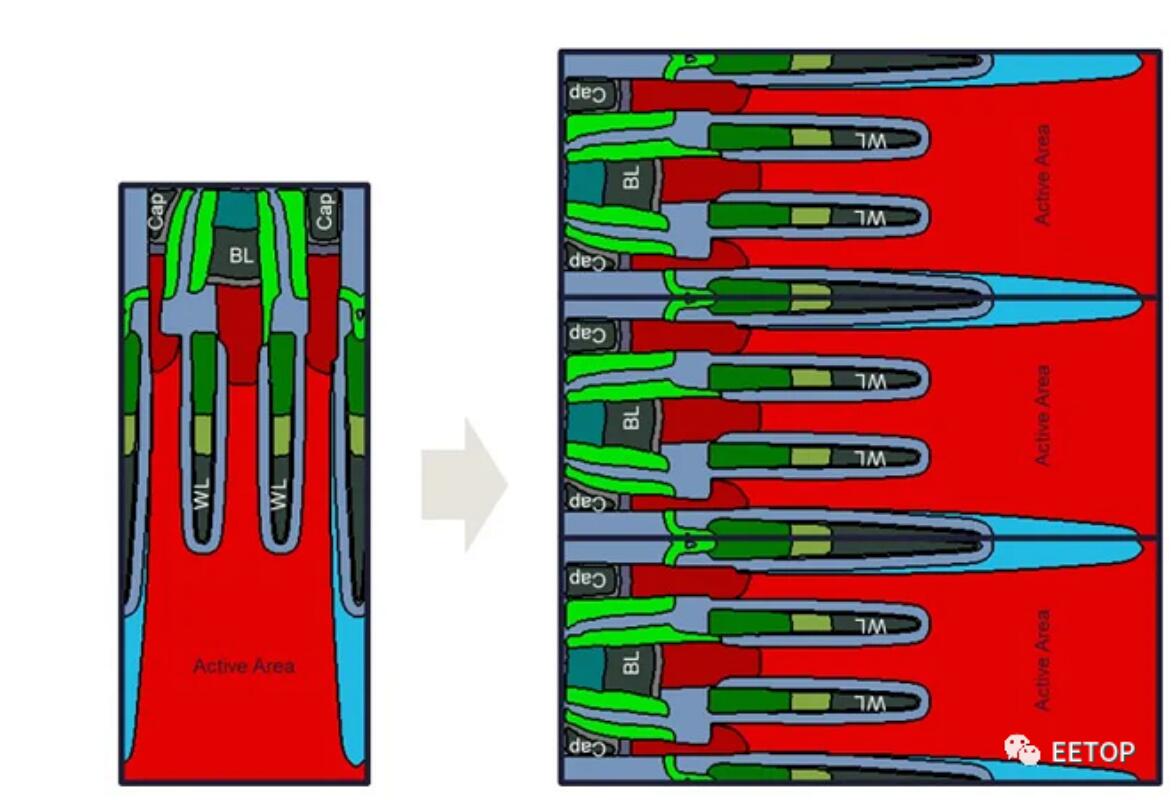

Lam Research 使用了一些芯片设计“技巧”来实现工作架构。首先,他们将位线移至晶体管的另一侧;因为位线不再被电容器包围,这意味着更多的晶体管可以连接到位线本身,从而提高芯片密度。

为了最大限度地提高面积密度,泛林研究还应用了一些最先进的晶体管制造技术。其中包括 Gate-All-Around (GAA) forksheet 设计,英特尔似乎正在探索下一代门控技术。Lam 研究提出的重新设计的 DRAM 架构可以进行堆叠,新的 DRAM 单元设计层层叠加,其流程与 NAND 类似。

但是,虽然 NAND 规模已突破了232 层大关,Lam Research 估计,第一代 3D DRAM 设计(例如其自己的设计)最多只能利用 28 个堆叠层。通过架构改进和额外的分层,泛林研究公司估计 DRAM 密度可以实现两节点跳跃式改进,并且可以通过向 DRAM 摩天大楼添加额外的层来实现进一步的改进。正如我们在其他制造技术中看到的那样,使用通孔阵列(台积电 TSV 的基础技术)来互连各个层。

然而,泛林研究公司提出的设计存在一个直接问题:当前没有能够可靠地制造所需功能的制造工具。该公司很快指出 DRAM 设计本身处于当今的前沿。改进和重新设计工具和流程是一项常见要求。正如该公司所说,在遇到 DRAM 扩展壁垒之前我们还有时间。希望所需的工具和专业知识能够在该时间范围内到达。