为了使半导体工艺继续缩小,硅必须掺杂越来越高的磷浓度,以促进准确和稳定的电流传输。就目前而言,随着业界开始大规模生产 3nm芯片,传统的退火方法仍然有效。然而,随着业界达到 3nm 以上,需要确保高于其在硅中的平衡溶解度的磷浓度。除了实现更高的浓度水平外,一致性对于制造功能性半导体材料至关重要。

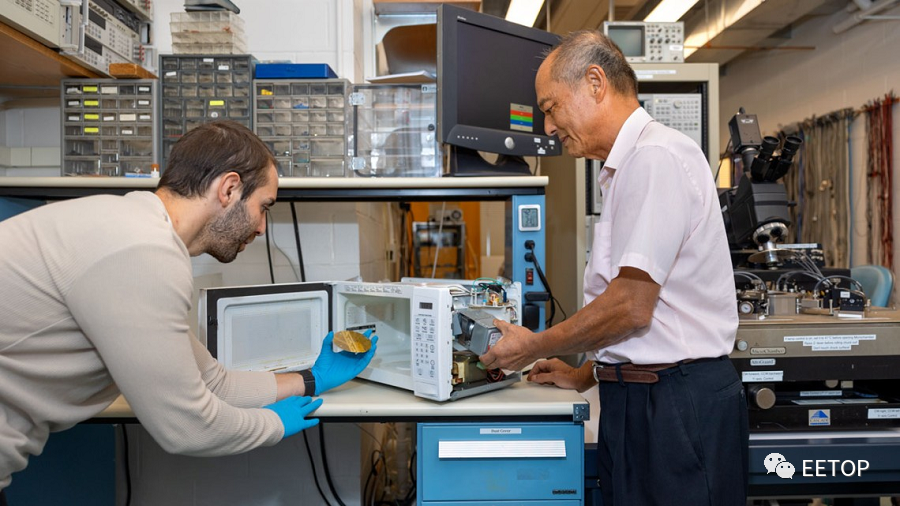

美国康奈尔大学的科学家们一直在使用改进的家用微波炉来帮助克服实际2nm 半导体生产的重大障碍。由此产生的微波退火炉借鉴了台积电关于微波和硅掺杂磷的理论。因此,半导体制造商可以使用新设计的设备和技术突破以前的磷浓度限制。

据康奈尔大学官网报道,该大学工程学教授改装的家用微波炉正在帮助“烹饪”下一代手机、计算机和其他电子产品,因为这项发明被证明可以克服半导体行业面临的重大挑战。

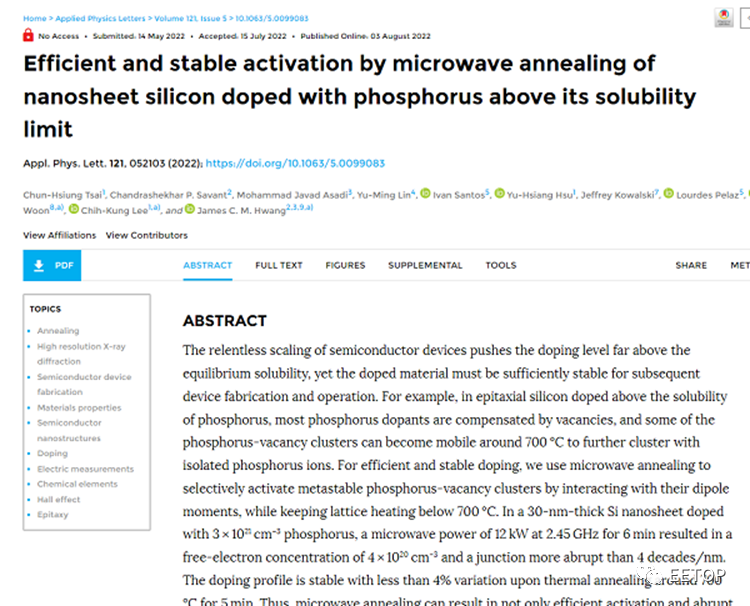

不久前发表在 Applied Physics Letters上的一篇论文详细介绍了这项研究。第一作者为康奈尔大学材料科学与工程系研究教授James Hwang ;康奈尔大学的其他贡献者是博士生 Chandrasekhar Savant 和前博士后研究员 Mohammed Javad Asadi。

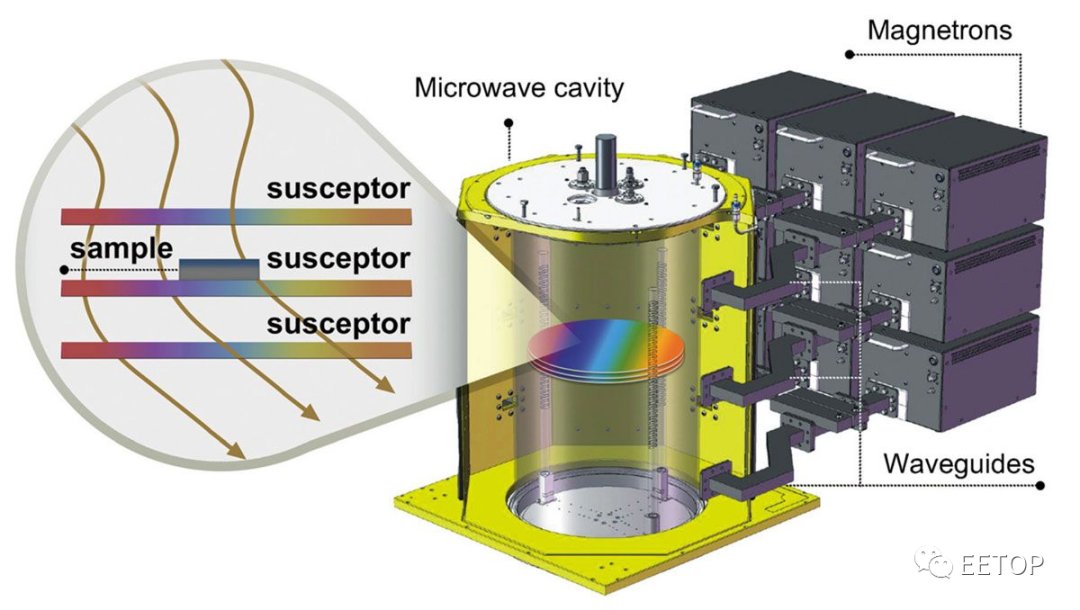

台积电此前曾推测,微波可用于退火(加热)过程,以促进增加磷的掺杂浓度。然而,以前的微波加热源往往会产生驻波,这不利于加热的一致性。简单来说,以前的微波退火设备加热其内容物不均匀。

康奈尔大学的科学家得到台积电的支持,开展微波退火研究。在本周早些时候由康奈尔大学分享的由此产生的科学论文中,科学家们得出结论,由于他们先进的微波退火方法,他们已经“克服了高于溶解度的高而稳定掺杂的基本挑战”。

Hwang 说,这一发现可用于生产 2025 年左右出现的半导体材料和电子产品,他已与博士后研究员 Gianluca Fabi 为原型微波退火器申请了两项专利。

“一些制造商目前正在生产 3 纳米的半导体材料”Hwang 说。“这种新的微波方法有可能使台积电和三星等领先制造商的尺寸缩小到仅 2 纳米。”

这一突破可能会改变微芯片中使用的晶体管的几何形状。20 多年来,晶体管被制成像背鳍一样竖立起来,以便在每个微芯片上封装更多,但制造商最近开始试验一种新架构,其中晶体管作为纳米片水平堆叠,可以进一步增加晶体管的密度和控制。通过微波退火实现的过度掺杂材料将是新架构的关键。

第一作者简介:

James Hwang 毕业于康奈尔大学材料科学与工程系,获得博士学位。在 IBM、贝尔实验室、通用电气和 GAIN 拥有多年的行业经验后,他的大部分学术生涯都在利哈伊大学度过。他共同创立了 GAIN 和 QED;后者成为上市公司 IQE。他曾是美国空军GHz-THz电子科学研究办公室的项目官员。他曾在美国康奈尔大学、意大利马尔凯理工大学、新加坡南洋理工大学、台湾国立交通大学和中国上海交通大学担任客座教授。他是 IEEE Life Fellow 和杰出的微波讲师。他发表了大约 400 篇参考技术论文,并获得了 8 项美国专利。他研究电子、光学和微机电设备和电路。他目前的研究兴趣包括扫描微波显微镜、二维原子层材料和器件,以及用于单个生物细胞的电磁传感器。