英特尔关键技术新突破:互连密度提升10倍、晶体管微缩提升50%!台积电、三星将面临新挑战!

2021-12-22 09:48:21 EETOP业内人士分析,从此次英特尔凭借高调宣布的多项新技术突破,有望在未来几年在先进工艺上领先于台积电和三星。

日前,英特尔制造、供应链和营运集团副总裁、战略规划部联席总经理卢东晖对媒体详细解读了此次的多项技术突破。他在会上感言,研究中最难的就是探路,就好比爬山的人一眼能够看到山顶在哪里,但是不清楚路该怎么走,要带多少补给。

卢东晖表示这些全新技术是有英特尔的组件研究团队所研制,众多突破摩尔定律昔日壁垒并出现在当前产品中的创新技术,都源自于该组件研究团队的研究工作,比如:应变硅、高K-金属栅极技术、FinFET晶体管、RibbonFET,以及包括EMIB和FoverosDirect在内的封装技术创新。

卢东晖强调,这次英特尔在IEDM上发的文章都有一个主要的基体,就是大部分的技术都是基于300毫米硅晶圆的传统CMOS技术,这是非常关键的。因为产生一个新的想法很简单,很多大学都在做,而工业界最大的问题就是能不能大批量生产,不能说重新起炉灶弄一个第四代半导体,最好的办法就是用现有已经投入的固定资产,能够尽快地把这些资产优化,不然成本太高,成本太高还是没人买。摩尔定律是一个经济定律,任何一个新技术如果不能达到让你的用户能够负担得起,那最后的应用只能是一些非常有限的应用。全世界现在大概有上万亿美元的投资都是在12寸晶圆设备、生态系统,需要把这些利用起来,这样制造成本才能下降。

在本次的IEDM 2021上英特尔重点介绍了这三个关键研究领域的最新突破及探索,披露的突破性进展表明,英特尔正通过对这三个领域的探索,持续推进摩尔定律,并将其延续至2025年及更远的未来。

据卢东晖介绍,微缩技术,传统叫transistor scaling,就是把晶体管面积变小。微缩技术是很简单的,有很多办法可以采用,比如全新的晶体管设计,或者是光刻技术的突破,或者用先进封装。以前二维的平面微缩,现在二维不能再缩,再缩就会有很多量子效应出现,所以现在就往上堆,早年3D NAND就是一直往上堆,这也是比较直观的理解。此次IEDM 2021,英特尔介绍了微缩技术的三个主要突破:

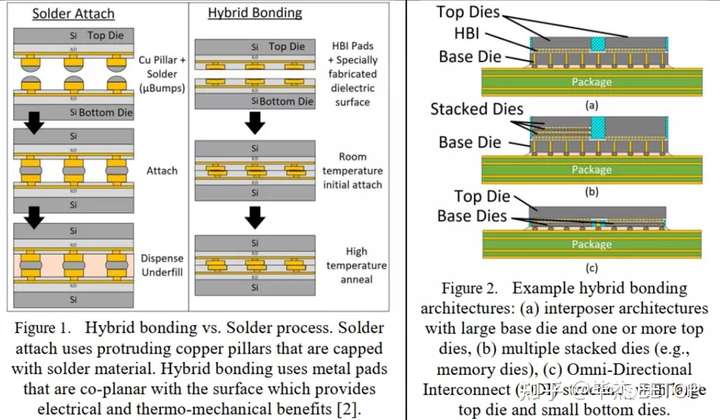

英特尔的研究人员提出了混合键合互连中的设计、制程工艺和组装难题的解决方案,期望能在封装中将互连密度提升10倍以上。在今年7月的英特尔加速创新:制程工艺和封装技术线上发布会中,英特尔宣布计划推出Foveros Direct,以实现10微米以下的凸点间距,使3D堆叠的互连密度提高一个数量级。为了使生态系统能从先进封装中获益,英特尔还呼吁建立新的行业标准和测试程序,让混合键合芯粒(hybrid bonding chiplet)生态系统成为可能。

卢东晖解释说,传统技术(SolderAttach)是通过焊锡将两个芯片进行连接,英特尔在研究的混合键成技术是让金属垫直接接触,这样会产生分子键合。“它最大的好处是连接的密度会急剧提升,至少是10倍的。这会让每平方毫米达到有10000个连接,这是非常紧密的。以后的芯片上会有几十亿的晶体管,或者几百亿的晶体管,最后都要连起来,所以这是非常关键的突破。”卢东晖说道。

卢东晖指出,这项技术的制程非常敏感,需要用机械抛光磨平表面,因此化学机械抛光(SNP)和沉积的优化是非常关键的。此外,也需要行业统一的标准和测试程序。

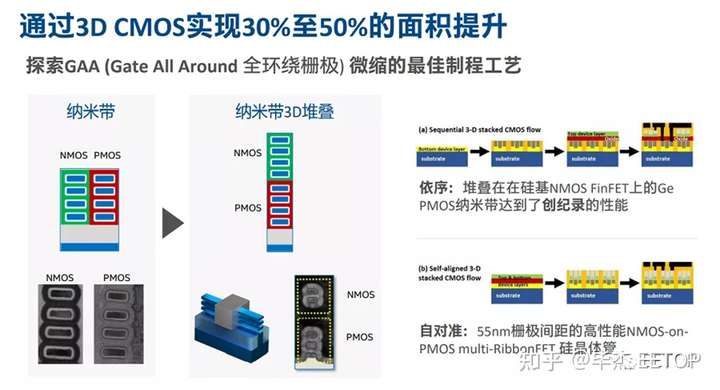

晶体管刚开始是二维的形式,后来变成FinFET,就是变成三维封装,再后来变成GAA,就是把NMOS叠在左边,PMOS叠在右边,往上叠了几层,而3D就是直接把NMOS和PMOS直接叠在一起,这样相当于面积减少了一半,面积利用率提高,微缩技术达到了面积减少一半的要求。

展望其GAA RibbonFET(Gate-All-Around RibbonFET)技术,英特尔正引领着即将到来的后FinFET时代,通过堆叠多个(CMOS)晶体管,实现高达30%至50%的逻辑微缩提升,通过在每平方毫米上容纳更多晶体管,以继续推进摩尔定律的发展。

英特尔在论文中宣布了这项技术在3D CMOS堆叠上的新突破,共有两种方法。方法一是依序,具体的工艺流程是将下面一层晶圆先做好,再将上面一层翻过来再做另外一层晶圆,这样能够有效提高性能;方法二是自对准,一种是通过光刻机对准,另一种叫做自我对准,要通过干蚀或者是沉积手段让晶圆自动对准。英特尔的自对准实现了55纳米的栅极间距,卢东晖称“这是非常了不起的突破”。

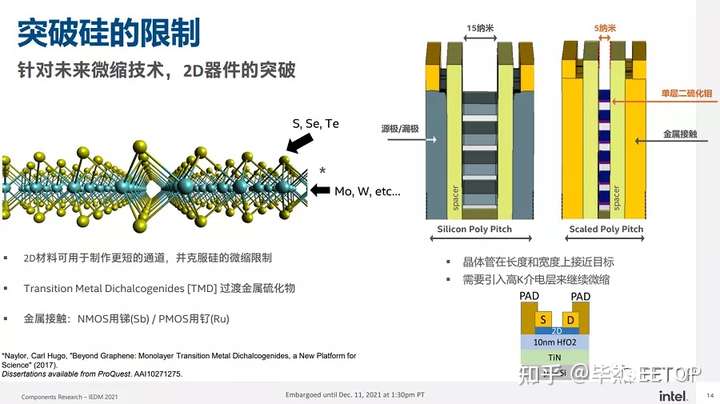

英特尔引入了金属锑和钌来突破硅的限制。因为现在电流的通道是用硅的基础,而这个是用二维材料TMD(过渡金属硫化物),它有一个非常好的特点是在Gate下面有一层非常薄的,单层的二硫化物原子层,可以作为更短的通道。因为硅的问题是无法继续往下缩,因为再往下缩很多量子效应出现,但二维材料有自己本身的特质,所以可以做得非常小。最大的突破不光是这个做出来了,而是用两种不同的金属去做金属接触,在源极和漏极,NMOS用的是锑,PMOS用的是钌,这样能让电容比较小一点。

这些背后都是大量的研究,过渡金属有几十种,如何知道这两种是比较好的,这是需要花很多时间、材料、精力去做,而把GAA一下子缩小3倍,从15纳米变成5纳米,这是非常了不起的。

英特尔同时也在为摩尔定律进入埃米时代铺平道路,其前瞻性的研究展示了英特尔是如何克服传统硅通道限制,用仅有数个原子厚度的新型材料制造晶体管,从而实现在每个芯片上增加数百万晶体管数量。在接下来的十年,实现更强大的计算。

卢东晖告诉媒体,因为硅做功率器件是不太合适的,尤其是要硅基CMOS要应用到汽车或者需要的高压器件电子设备,这就得想办法为硅注入一些新的功能。另外就是更最大的内存资源,因为当下需要的数据量、产生的数据量越来越大,比如手机上拍个照片,现在文件的大小与十年前相比超过很多倍了,所以结果需要的存储量越来越大,存储量越来越大需要的处理能力越来越高,而新材料的突破是迫在眉睫的。

在该领域,英特尔本次披露了两大技术突破

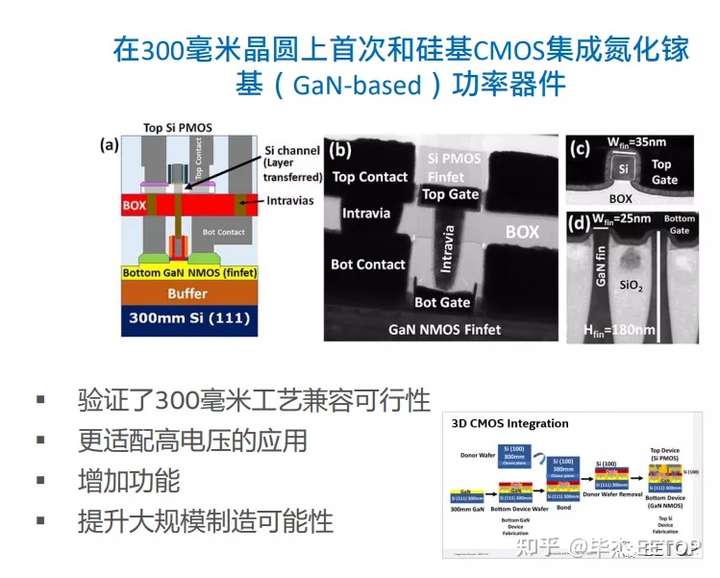

通过在300毫米的晶圆上首次集成氮化镓基(GaN-based)功率器件与硅基CMOS,实现了更高效的电源技术。这为CPU提供低损耗、高速电能传输创造了条件,同时也减少了主板组件和空间。

现在的功率器件GaN在国内也比较热,它可以直接做出70伏的晶体管,这是硅做不到的。英特尔这次也是首次集成,因为以前没有人在硅晶圆做过,很多人可能直接用GaN wafer,但这个成本很高。英特尔这次的GaN直接跟传统的硅晶圆集成在一起,这在以前是没有出现过的。

硅基CMOS集成有两个突破:一个是用硅晶圆上面放一个buffer,buffer更外面就是用的氧化硅的。在这样的情况下,它其实不需要硅晶圆,只要有载体就行。在硅片上,所有的基材不需要特制的基材。另外一个是验证了300毫米工艺兼容可行性。卢东晖特别强调半导体一定要从这个方面着手,因为工业界在300毫米投入资金和生态链已经太强大了,最好不要突破它,突破它成本会很高。

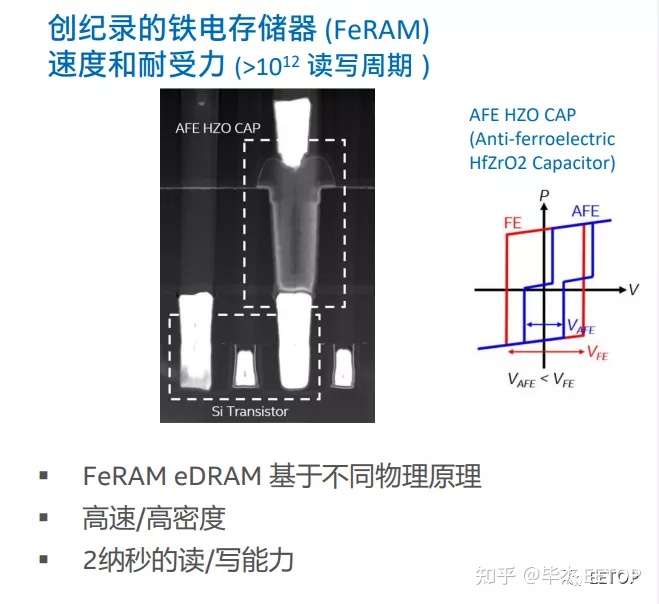

另一项进展是利用新型铁电体材料作为下一代嵌入式DRAM技术的可行方案。该项业界领先技术可提供更大内存资源和低时延读写能力,用于解决从游戏到人工智能等计算应用所面临的日益复杂的问题。

铁电存储它是用了一个新的存储器,用了一个新的技术实现了2纳秒的读写速度和超过1012次方的读写周期,这个是非常了不起的技术成就。

铁电存储器国内也有很多公司在关注,这完全是跟传统的CMOS工艺结合的。英特尔做这个东西有非常大的优势,因为英特尔有自己的X86架构,由于具有2纳秒的高速读/写能力,铁电存储器可以用来作为从L1 Cache到DRMA之间的中间层。

英特尔正致力于大幅提升硅基半导体的量子计算性能,同时也在开发能在室温下进行高效、低功耗计算的新型器件。未来,基于全新物理学概念衍生出的技术将逐步取代传统的MOSFET晶体管: