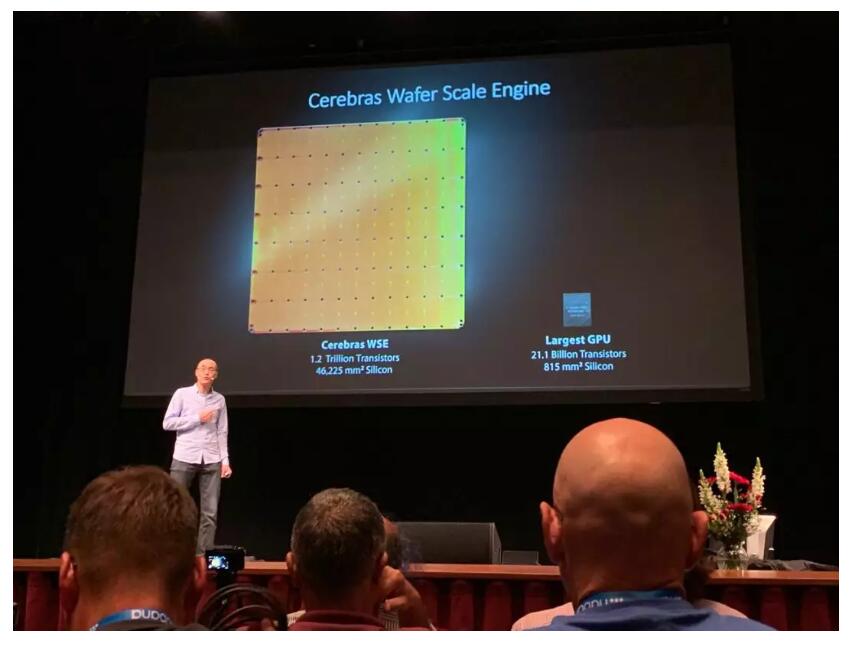

本届Hot Chips最大的亮点,毫无疑问是Cerebras的wafer-scale engine (WSE)。我们通常的芯片,一片wafer可以切出几十到上万片不等的芯片,而为了追求极致的性能、最大的片上存储,Cerebras选择了一条极端的路线,让整片wafer就是一片芯片。当Cerebras的联合创始人Sean Lie拿出样品实物的时候,会场里响起了掌声,这也是本次大会唯一一次不是在报告开始与结束时候礼节性的掌声。

WSE芯片,由12x7=84个die组成,共有40万个为深度学习优化的计算核,片上存储达到了惊人的18GB,超过了很多电脑的内存大小。这样一颗芯片,在我眼里是有特殊的美感的:如同看到长城和金字塔,这样在技术水平极其低下时,似乎人类无法实现的杰作;也如同看到了蒸汽朋克电影中的庞然大物,复古而雄伟;又如同最为精密和复杂的机械表,无数精巧的结构让人感叹。这是在大的范式没有改变的情况,当前工程技术可以做到的极限了。

Cerebras的报告是极少数全篇没有任何性能数字的报告,只有一句话“It’s working”。这样一篇论文能够被Hot Chips录用来进行报告,足见其受到的关注和重视。而我个人有一个习惯,除了认真听别人说做了什么,更会去想他们没说什么。而在这次,他们只说了“It’s working”,而并没有说“It’s working well”,也许就是在暗示些什么。

Cerebras的WSE芯片仍然是有非常多待解决的问题的:

(1)这样一片芯片,尽管做了很多的容错设计,其良品率怎样,仍然是一个疑问;

(2)传说中15kw甚至50kw的功耗,怎样去实现良好的散热;

(3)整个芯片由12x7个die组成,die之间的通信是与台积电联合研发的新型工艺,其效果如何。

这样许许多多的问题,都值得追问下去,而在报告现场,尽管PPT上有相关的页来阐述是用怎样的思路来解决,但是Sean基本上是一带而过,没有介绍任何细节,这也不由得不让人猜测,在这些地方,可能仍然存在着非常多的技术问题需要解决。

对于我个人来说,我非常佩服Cerebras的CEO Andrew Feldman这样一位有魄力、有远见的成功的连续创业者:他曾经做过四个公司,都以上市或者并购成功退出。我也非常佩服包括Sean Lie在内的Cerebras的工程师,勇于挑战最极致的技术路线。任何一条技术路线走通都非常不容易,希望Cerebras能够一个一个解决路上的技术难题,这不仅仅是Cerebras一家公司的事情,也是所有有技术信仰的芯片行业工程师与研究者的共同心声——大家没有机会和财力去做这样一件激动人心的事情,希望你们能做好!