美国应用材料公司用于下一代3nm和GAA的半导体设备简介

2022-05-13 10:55:45 EETOPEETOP编译自anandtech

上个月,三星代工厂悄悄宣布,将在第二季度开始使用其 3GAE(3 纳米级、全栅极晶体管)的早期工艺技术生产芯片。虽然业界首个采用 GAA 晶体管的 3 nm 级节点本身就是一项值得注意的成就,但特别重要的是,要高效地制造 GAA 晶体管,晶圆厂必须配备新的生产设备。正好,应用材料公司最近刚刚介绍了他们的下一代设备,这些设备将用于使三星(和其他晶圆厂)能够构建他们的第一个 GAA 芯片。

环栅晶体管:一次解决许多问题

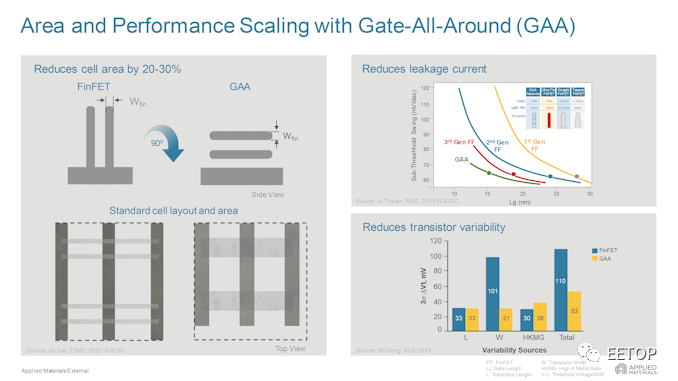

新的工艺技术应该能够实现更高的性能、更低的功耗和更高的晶体管密度,以满足芯片设计人员的要求。但近年来,这种组合特别难以实现,因为缩小晶体管尺寸会导致漏电流等负面影响。为了在最小化晶体管尺寸的同时保持缩放性能和电压,该行业在 2012 年开始从平面晶体管过渡到 FinFET 晶体管(通过使栅极更高来增加晶体管沟道和栅极之间的接触面积),并且这种类型的晶体管将继续存在很长一段时间。但随着晶体管缩小的负面影响开始显现,基于 FinFET 的节点创新步伐正在放缓。

虽然所有芯片制造商都在各种学术行业活动中谈论 GAAFET 及其相对于 FinFET 的优势,但三星是第一家宣布过渡到 4 纳米节点的新型晶体管的公司, 2019 年 ,它推出了基于 GAAFET 的 3GAE 和 3GAP 节点,并分别于 2022 年和 2023 年实现大批量生产。去年,该公司 再次强调 了在 2022 年使用其 3GAE 开始生产的计划,本季度它表示将在第二季度开始量产。

制造业面临挑战

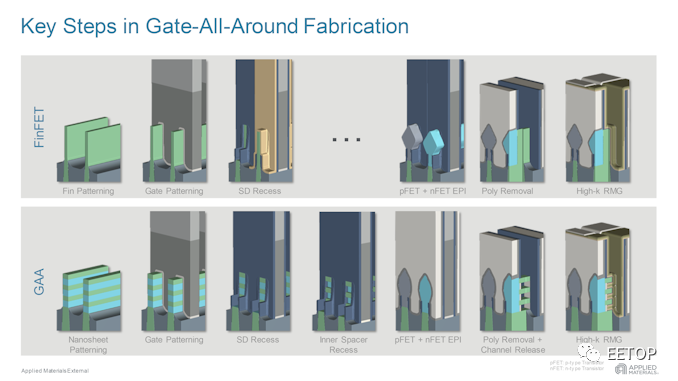

但是使用任何领先的工艺技术生产芯片都是具有挑战性的,使用三星基于 MBCFET 的 3GAE 节点制造产品肯定会带来一些风险,不仅因为我们谈论的是 3 纳米级制造工艺,而且因为 GAA 晶体管的制造是不同的而不是制造 FinFET。

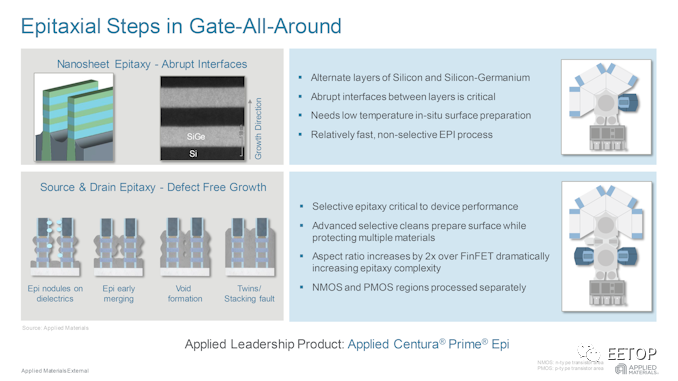

GAA 晶体管的通道采用光刻、外延和选择性材料去除等工艺成型,这些工艺使芯片制造商能够微调宽度和均匀性以获得最佳功率和性能。与 FinFET 相比,这些外延步骤要复杂得多,因为制造商需要在微小的 10 nm 通道周围沉积多层栅极氧化物和金属栅极叠层,这是 GAAFET 面临的关键挑战。这就是应用材料公司的高真空集成材料解决方案 (IMS) 系统发挥作用的地方。

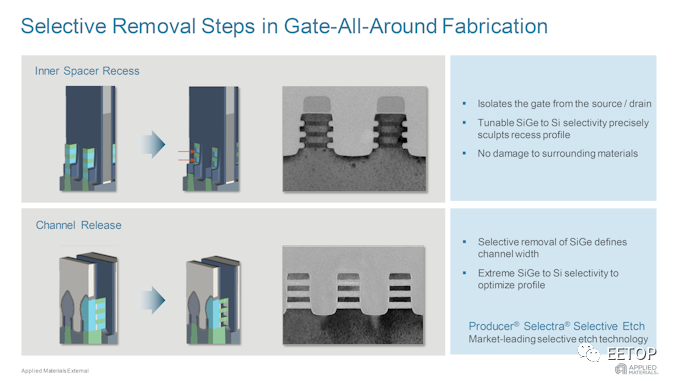

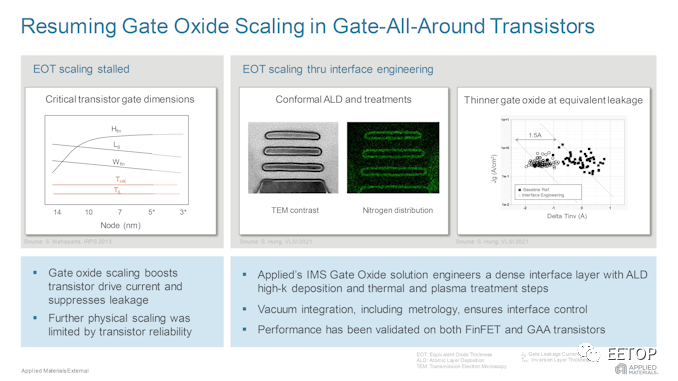

首先,应用材料公司的 Producer Selectra Selective Etch 腔体去除了不必要的 SiGe,以将栅极与源极/漏极隔离,并在不损坏周围材料的情况下定义沟道宽度。其次,AppliedCentura Prime Epi IMS可以使用集成原子层沉积 (ALD)、热处理、等离子体处理和计量步骤来沉积超薄栅极氧化层。与竞争解决方案相比,Applied 的 IMS 可以将栅极氧化层厚度减少 1.5 埃,这可以使栅极更厚并实现更高的驱动电流,从而提高晶体管性能,而不会增加电流泄漏,这是薄栅极的结果。

Applied 于 2016 年推出了其第一款 Selectra 蚀刻系统,从那时起已交付了 1,000 多个目前由其客户使用的腔体,因此业界非常了解如何使用它们。虽然蚀刻是一种广泛使用的工艺,但随着行业开始转向更新的工艺技术,包括基于 GAA 晶体管的工艺技术,它的使用和重要性将会增加。

需要注意的是,Applied Materials 共享的数据来自多家公司(包括台积电和高通),不应仅适用于三星代工的 3GAE 和 3GAP 节点。同时,GAA/MBC/纳米带/纳米片晶体管的一般优势,以及其制造面临的挑战,对于整个行业来说都是相似的。

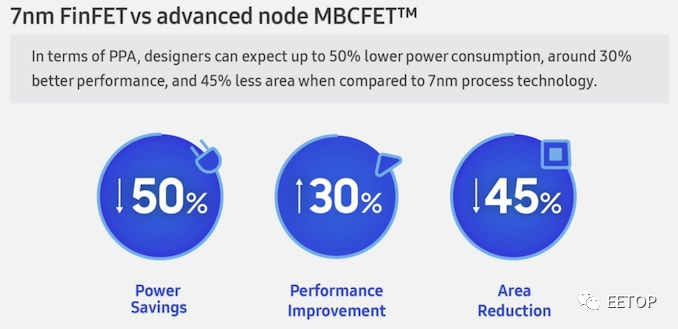

三星的 3GAE:+30% 性能,-45% 面积

说到优势,三星预计其 3GAE 工艺与 7LPP 相比,性能提升 30% 或功耗降低 50%,面积减少 45%。这种有形的好处可能足以证明短期内与这种转变相关的挑战是合理的。

目前,使用依赖全新晶体管结构的 3GAE 制造技术总体上具有挑战性,因为除了新的电子设计自动化 (EDA) 工具外,三星还需要发明新的 IP,并采用全新的设计规则. 所有这些,再加上新的光刻、新的蚀刻和新的沉积步骤,都将使三星的转型变得困难。

但作为交换,它将比英特尔和台积电提前数年开始获得 GAA 晶体管的经验,这可能会在长期的未来带来一定的收益。此外,使用 GAAFET 的经验将有利于三星的 DRAM 制造,因为内存大大受益于更小的单元尺寸和更高的晶体管密度。

原文:

https://www.anandtech.com/show/17385/applied-materials-new-tools-needed-for-3-nm-and-gaa-transistors