AMD申请3D堆叠散热专利:妙用热电效应

2019-07-02 10:32:53 太平洋电脑网但随着堆叠元器件的增多,集中的热量如何有效散出去也成了大问题,AMD就悄然申请了一项非常巧妙的专利设计。

Intel Foveros立体封装

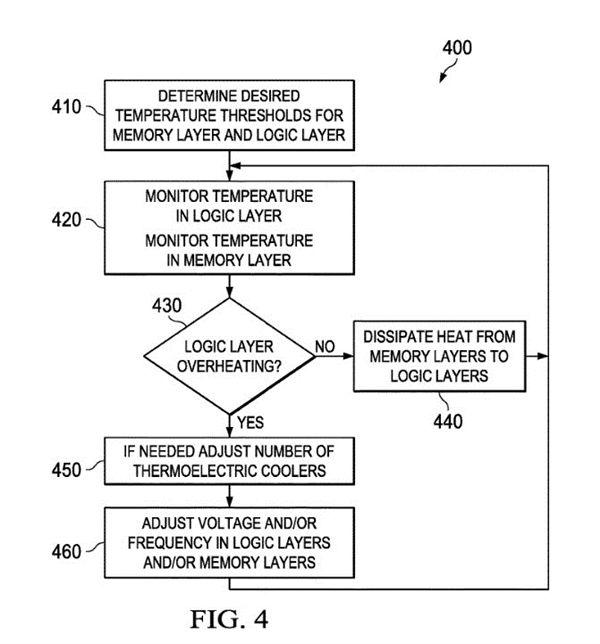

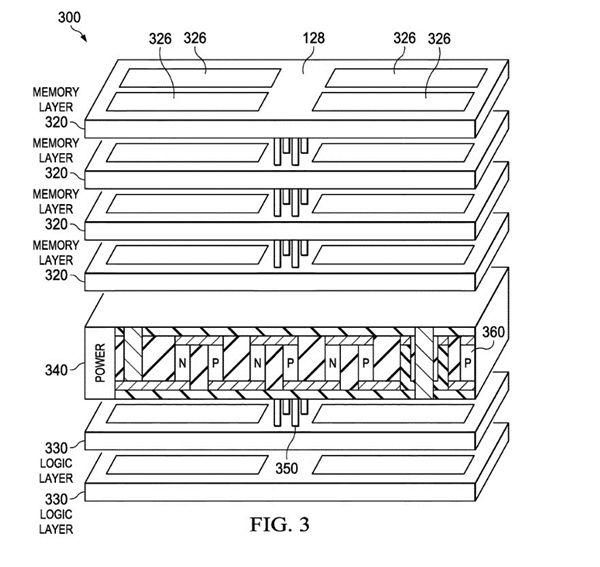

根据专利描述, AMD计划在3D堆栈的内存或逻辑芯片中间插入一个热电效应散热模块(TEC),原理是利用帕尔贴效应(Peltier Effect)。

它也被称作热电第二效应、温差电效应。由N型、P型半导体材料组成一对热电偶,通入直流电流后,因电流方向不同,电偶结点处将产生吸热和放热现象。

按照AMD的描述, 利用帕尔贴效应,位于热电偶上方和下方的上下内存/逻辑芯片,不管哪一个温度更高,都可以利用热电偶将热量吸走,转向温度更低的一侧,进而排走。

不过也有不少问题AMD没有解释清楚,比如会不会导致上下的元器件温度都比较高?热电偶本身也会耗电发热又如何处理?

但总的来说,AMD的这个思路非常新奇巧妙,未来或许会有很光明的前景。