指甲盖大小塞了500亿晶体管!IBM打造世界首款2纳米芯片

2021-05-07 12:52:16 EETOP但这几年来,尽管IBM退出了代工业务,不过好像IBM在半导体先进工艺研发上一直没有放弃,时不时会传出IBM推出领先世界一两代的最先进的技术。

据IBM官网5月6日消息,IBM宣称自己打造了世界首个2纳米的芯片,大幅推进了当前芯片生产技术的前沿,在半导体设计及制程上取得突破。

在IBM Research的Albany工厂制造的2 nm晶圆的特写,肉眼可见单个芯片

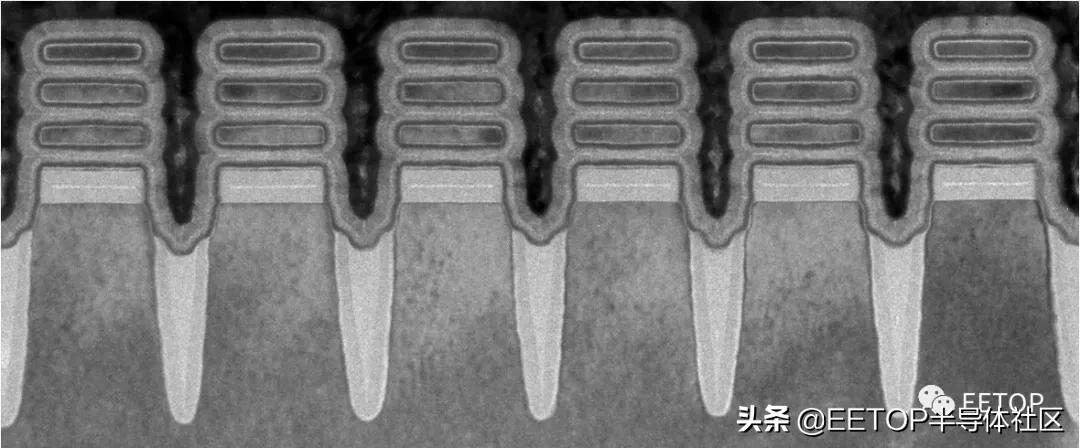

使用透射电子显微镜观察到的2nm芯片,2nm小于人类DNA单链的宽度

IBM官网发布的2纳米芯片宣传片:

性能获飞跃进展

在这里IBM的2nm制程号称在150mm²(指甲盖大小)的面积中塞入了500亿个晶体管,平均每平方毫米为3.3亿个。做为对比,台积电和三星的7nm制程大约在每平方毫米是9,000万个晶体管左右,三星的5LPE为1.3亿个晶体管,而台积电的5nm则是1.7亿个晶体管。

据IBM 的说法,其2nm 架构可以在与现有的7nm 相同的性能下,仅是7纳米的1/4的功耗,也就是说放到现代手机中的话,可能四天才需要充一次电。又或者,它也能在与现有的7nm 相同的能耗下,增加45%的性能,在笔电、自驾车等较不在意功耗的场景下,可能带来更高的运算力。其他包括资料中心、太空探索、人工智能、5G、6G,乃至于量子运算都可能在受惠之列。

2纳米的研发路线及技术细节

据悉,目前担任IBM混合云研究副总裁的Mukesh Khare带领其完成了2纳米技术的突破。

资料显示,Khare在1999年到2003年间,从事90纳米SOI工艺的开发,该工艺将Power4和Power4+推向市场,他随后又负责了65纳米和45纳米SOI的推进,这些技术被Power5和Power6采用;之后他对对用于Power7的32纳米技术进行了研究,然后研究了在Power8上使用的22纳米工艺中使用的高k /金属栅极技术。然后Khare继续担任奥尔巴尼纳米技术中心的半导体研究总监,

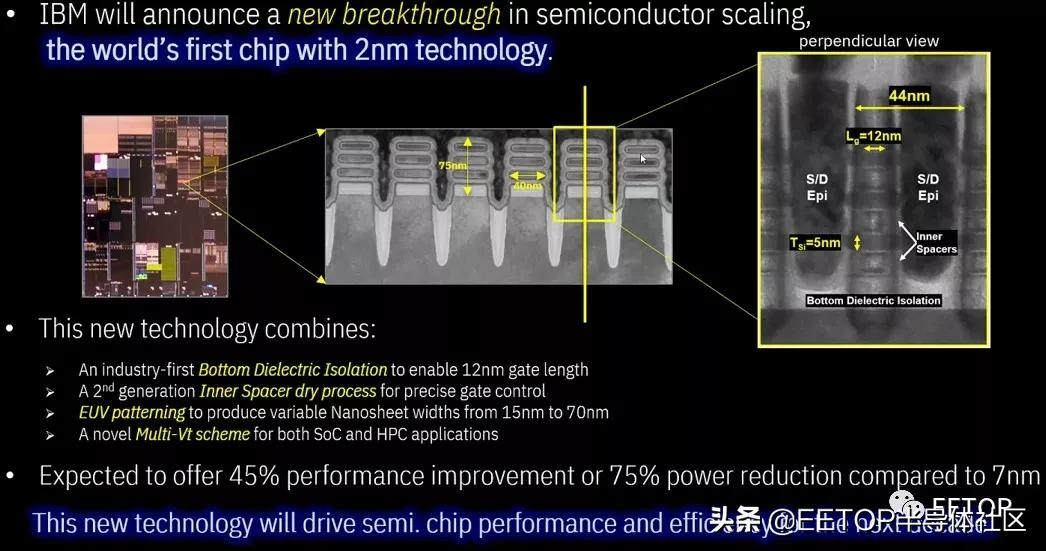

如下图所示,这是IBM掌握的2纳米芯片制造技术的要点。里面有很多东西,让我们把它拆开一点。

首先,在这个芯片上,IBM用上了一个被称为纳米片堆叠的晶体管,它将NMOS晶体管堆叠在PMOS晶体管的顶部,而不是让它们并排放置以获取电压信号并将位从1翻转为零或从0翻转为1。这些晶体管有时也称为gate all around或GAA晶体管,这是当前在各大晶圆厂被广泛采用的3D晶体管技术FinFET的接班人。从以往的介绍我们可以看到,FinFET晶体管将晶体管的源极和漏极通道拉入栅极,而纳米片将多个源极和漏极通道嵌入单个栅极以提高密度。

IBM表示,其采用2纳米工艺制造的测试芯片可以在一块指甲大小的芯片中容纳500亿个晶体管。

在IBM的这个实现方案下,纳米片有三层,每片的宽度为40纳米,高度为5纳米。如果您在上表的右侧看,那是一张纳米片的侧视图,显示出它的侧视图,其间距为44纳米,栅极长度为12纳米,Khare认为这是其他大多数晶圆代工厂在2纳米工艺所使用的尺寸。

2纳米芯片的制造还包括首次使用所谓的底部电介质隔离(bottom dielectric isolation),它可以减少电流泄漏,因此有助于减少芯片上的功耗。在上图中,那是浅灰色的条,位于中部横截面中的三个堆叠的晶体管板的下面。

IBM为2纳米工艺创建的另一项新技术称为内部空间干燥工艺(inner space dry process),从表面上看,这听起来不舒服,但实际上这个技术使IBM能够进行精确的门控制。

在实施过程中,IBM还广泛地使用EUV技术,并包括在芯片过程的前端进行EUV图案化,而不仅是在中间和后端,后者目前已被广泛应用于7纳米工艺。重要的是,IBM这个芯片上的所有关键功能都将使用EUV光刻技术进行蚀刻,IBM也已经弄清楚了如何使用单次曝光EUV来减少用于蚀刻芯片的光学掩模的数量。

这样的改善带来的最终结果是,制造2纳米芯片所需的步骤要比7纳米芯片少得多,这将促进整个晶圆厂的发展,并可能也降低某些成品晶圆的成本。这是我们能看到的。

最后,2纳米晶体管的阈值电压(上表中的Vt)可以根据需要增大和减小,例如,用于手持设备的电压较低,而用于百亿超级计算机的CPU的电压较高。

IBM并未透露这种2纳米技术是否会采用硅锗通道,但是显然有可能。

能否量产是关键

当然,公布制程试制成功,和能量产依然是两码事,IBM自己2015年就宣布试制7nm制程成功,但一直到去年八月才有第一个商用化产品出现。因此IBM这里宣示的意味是比较浓厚,何时能有产品推出又是另一回事了。

目前量产的制程技术中,领先的是台积电的5nm,由苹果的M1、A14芯片及华为的Kirin 9000所用,次之为三星的5LPE,用在Snapdragon 888芯片上,再来就是两间公司应用广泛的7nm制程技术了。自然,所有人也都努力向着更高密度的芯片推进中,其中台积电的4nm与3nm预计明年量产,而2nm也已经取得了关键性的突破,离IBM并不远。反倒是Intel的7nm制程芯片(Intel的制程技术晶体管密度较高,因此约略介于台积电的5nm与4nm之间)要等到2023年才投产,还是慢了一步了。