超高速SerDes在芯片设计中的挑战

2019-06-26 13:00:58 EETOP串行器/解串器用于将并行数据转换为串行数据,使设计人员无需增加引脚数即可加速数据通信。但随着数据量的增加,以及随着越来越多的设备连接到Internet并最终连接到云,越来越需要更快地移动更多数据。这反过来又使SerDes设计变得越来越复杂。

对高速SerDes的大部分需求来自大型数据中心,目前最先进的吞吐量为100 Gbps。最近开始想400Gbps进发。甚至人们已经开始探路800 Gbps的支持。

因此,IEEE和光互联网论坛的标准在单个通道上定义越来越高的数据速率,这允许将数据聚合到更大的系统。然后,为了将SerDes技术提升到更高的性能水平,其中一项重大进步是采用了高于28Gbps的PAM4信令。

Rambus业务运营高级主管Sunil Bhardwaj说:“随着串行数据速率达到每通道100多Gbps,带宽增加引起的信号损伤促使采用PAM4或4级脉冲幅度调制。” “与NRZ(不归零)相比,PAM4通过在每个符号中传输两位来将给定数据速率的带宽减半。这允许在通道中加倍比特率而不会使所需带宽加倍。例如,使用PAM4信令,56-Gbps比特率以28 GBauds传输,并具有14 GHz的奈奎斯特频率。利用NRZ信令,56 Gbps比特率以56 GBauds传输,奈奎斯特频率为28 GHz。

但有一个权衡。“多个符号级别使PAM4对振幅噪声比NRZ更敏感,”他解释说。“与NRZ相比,PAM4引入了9.6dB的损耗,工作在相同的奈奎斯特频率。然而,在这些高频率下,以NRZ奈奎斯特频率的一半运行的能力使PAM4成为低损耗替代方案。与NRZ一样,PAM4信号受抖动,信道损耗和符号间干扰的影响。此外,三个眼图的测量因新的接收器行为而变得更加复杂,例如三个限幅器阈值,单个限幅器时序偏移,均衡以及时钟和数据恢复。不出所料,PAM4信号分析从为分析NRZ的抖动和噪声而开发的技术中借鉴了很多。此外,许多NRZ技术适用于PAM4。

另一个复杂因素是高速设计越来越容易受到电磁串扰问题的影响,ANSYS半导体业务部产品营销经理Annapoorna Krishnaswamy指出。

电磁交叉耦合问题变得越来越重要的一些关键因素包括:

随着时钟速度的提高,先进的封装类型以及减小面积的压力,设计和验证高速IC设计的传统方法已不再足够。

设计的所有方面 - 高速信号/时钟线,详细的电源和接地布线,无源器件,甚至封装层都需要进行详细建模和验证。需要对片内寄生效应进行精确建模,包括自感和互感(RLCk),以完全捕获从DC到毫米波频率的电气行为(适用于5G应用)。这对于分析由于通过电源/接地,基板或封装层的耦合而影响多个邻近区域的一个信号的不需要的电磁干扰是至关重要的。“

这就是为什么准确捕获电磁(EM)现象(包括电流分布,皮肤和邻近效应)对于降低EM串扰引起的性能降低和高速和低功耗片上系统故障的风险至关重要的原因。EM感知设计流程有助于减少过度设计,面积和成本,同时确保设计的卓越性能,质量和可靠性。

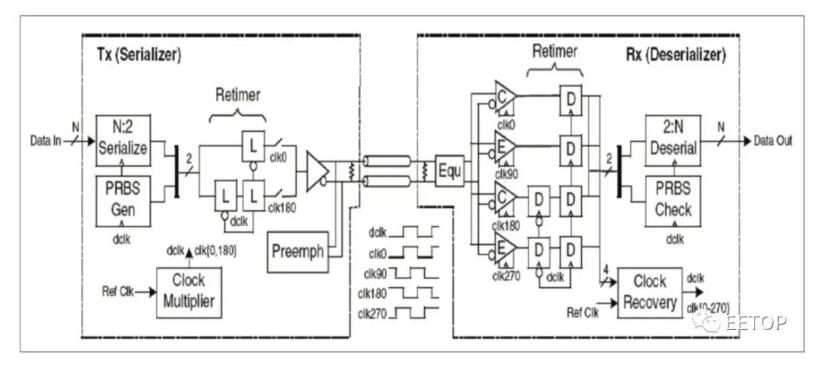

图1:典型的高速I/O架构

设计挑战

Adesto的工程师Martin Hujer表示,对于高速SerDes,挑战通常围绕功耗,时钟分配(模拟时钟树),所用封装类型以及寄生效应。“然后,PCB上有布线,支持测试模式和测试模式,以及快速数字逻辑。此外,还需要一种符合更高级别串行协议的数字控制器。在集成到定制芯片中时,必须考虑所有这些挑战。根据应用和客户要求,可能存在替代解决方案的潜力,您可以在一个或多个高速串行通道和速度较慢但仍然很快的并行总线之间进行权衡。“

Rambus的Bhardwaj说,与此同时,随着频率的增加,每种类型的抖动,ISI,振铃,串扰,接地反弹,电源噪声的损失都会更加严重。“因此,信号完整性(SI)现在是系统架构无可否认的关键方面。专业SI工程师在整个设计周期中定期与系统架构师,电路设计师和系统工程师进行交互。为了满足当今高性能系统的需求,必须制作整个链路的SI模型,包括发射器,接收器,时钟和通道。反过来,全面的链路分析会影响一系列设计架构,包括均衡,时钟,时序校准,以及编码和/或纠错。“

此外,他还必须仔细实施封装设计,以满足高频率和严格的电气性能要求。“必须特别注意封装中的高速I / O和模拟电源,使用电磁(EM)模拟器设计封装基板,以验证封装设计是否满足各种要求,包括所有交叉通话隔离,阻抗和S参数,以及电源电感。“

与此同时,工程团队希望他们的IP具有已知的故障率和寿命,以便在汽车和其他安全关键应用中提供可靠的服务。“随着CMOS和finFET技术稳步发展到更小的特征尺寸,随机元件的变化和布局中的系统偏移变得更加重要,” Silicon Creations业务开发副总裁Andrew Cole说。“我们必须仔细检查电路可靠性故障模式和网表的蒙特卡罗模拟,通过包括更精细的布局寄生效应来实现更大的响应。因此,即使智能网表减少,我们也看到设计验证CPU时间从28nm增加到5nm,增加了两个数量级。“

换句话说,高性能SerDes的设计挑战类似于转移到finFET的设计挑战,尤其是在成品率、可靠性、大型网表和长仿真时间方面。除了我们之前讨论过的finFET挑战,SerDes对高速信号也有ESD要求。对于静电放电,FinFET器件的鲁棒性不如平面晶体管。因为它们的三面被氧化物包围,所以它们也不会散热。这为在高级节点中实现非常高的数据速率带来了另一个困难的设计挑战。

今天的finFET工艺并未显着提升晶体管性能。真正的改进是在芯片上的可用空间中。但是,持续的功能缩减确实使设计这些设备变得更加困难,并且必须创建新的电路架构来应对这些挑战,Analog Bits执行副总裁Mahesh Tirupattur指出。

“另一个重大挑战是为EM设计,”Tirupattur说。“这些导线的电阻更大。因此,导线的载流能力大大降低。为高性能设计提供电源仍然是布局布线拓扑中的一个挑战。”

汽车应用中的SerDes

由于如此多的关注转向汽车应用,环境压力也在SerDes功能中发挥作用。不同的操作条件可能会不同地影响设

人们将在数据中心使用的技术节点(7nm到5nm),与他们可能用于汽车应用的技术节点不同。” Mentor的Tegethoff说。“在汽车应用中,首先要取决于它是否是一个安全项目,然后开发人员将对它做各种额外的事情。但如果一个人只是在做IP,他们必须确保把所有这些都考虑进去,因为他们不一定能控制它的发展方向。他们希望能够将IP推广到不同的地方。”

他指出,由于对设计的可靠性和鲁棒性有如此多的附加要求,不同的设计团队将根据安全标准或客户的要求遵循不同的协议。“例如,(电路)老化将用于任何通常用于汽车功能安全类型应用的任何东西。像意法半导体(STMicroelectronics)或安森美半导体(ON Semiconductor)这样的公司希望确保如果事情恶化,它们会优雅地降级并且不会引起问题。也就是说,没有一个简单的答案。根据应用的不同,它会有所不同。“

先进节点下的SerDes

当涉及到将SerDes移动到更先进的技术节点时,会发生很大的变化。

“对于7nm的SerDes,设计工程师遇到的最头疼的问题之一就是工艺复杂性。自180nm以来,层数增加了5倍,“Tegethoff说。“设计规则也成为一项挑战。在模拟设计方面,模拟电路是否与数字电路一样可扩展?你能依靠你对模拟数字化的经验法则吗?并不是的。如果你看一下从180nm到7nm的数字缩放,它大概是660比1,相同技术比较的模拟缩放大约是10比1,所以它的扩展几乎没有那么多。“

同样困扰SerDes设计人员的是先进节点中的互连,它影响电路中的信号传输和模拟时间。“你需要对所有电容和电阻进行完整的模拟提取,”他说。“然后你必须仿真模拟设备噪音,确保它在所有工艺角运行,还要进行蒙特卡罗仿真等待。总之设计人员最终会运行大量仿真,并且耗费大量的时间。“

并不是所有这些都可以通过工具来完成。与许多工程挑战一样,对高性能SerDes最真实的优化是结合使用自动化工具的设计人员的专业知识。