KWIK电路常见问题解答 15Msps 18位ADC的驱动器设计考虑因素

2023-09-12 09:09:49 EETOP常见问题解答:为15Msps 18位ADC设计输入驱动器时应该考虑哪些因素

ADC驱动器是数据采集信号链设计的关键构建模块。ADC驱动器用于执行许多关键功能,如输入信号幅度调整、单端至差分转换、消除共模偏移,并经常用于实现滤波。本技术诀窍与综合知识(KWIK)电路常见问题解答(FAQ)笔记讨论如何从单端输入信号产生经调整的差分输出信号,并对信号进行电平转换以确保其满足ADC满量程的性能需求。

为了帮助回答这个常见问题,我们将使用LTC6228(一款低噪声、低失真、高速轨到轨输出运算放大器)和LTC2387-18 SAR ADC。我们将利用噪声计算显示设计对信号链解决方案的整体SNR性能的影响。

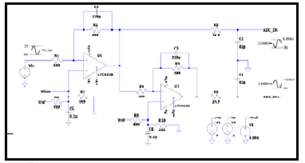

图1.– 通过调整和电平转换实现单端至差分转换

对于本例,设计要求规格如表1所示,输入信号为0V至5V正弦波。此设计自始至终将使用图1所示的ADC驱动器电路。该电路的功能是将单端输入信号转换、调整、移位为适当的差分输出信号,以便它能轻松地与信号链中的下一级(即ADC)连接。

为了分析图1所示电路的性能,我们将使用信噪比(SNR),获取每一级的噪声贡献并将其用于整体计算。计算中使用的LTC2387-18 ADC的SNR和LTC6228的频谱噪声密度均来自相应数据手册中的规格。

规格 | 设计要求 |

输入单端 | 0至5V |

输出共模 | 2.048V |

差分输出 | 8.192Vp-p |

电源+Vs/-Vs | +7V/-3V |

ADC 全差分 | 18位 |

Vref | 4.096V |

SNR | 93dB |

请注意,对于本例,可以忽略1/f噪声的影响,因为目标频率远高于1/f区域,并且选定的元器件(如图1所示)经过优化可以最大限度地减少噪声贡献。

1.在单电源和双电源之间进行选择时,应考虑如下一些因素:由于信号链的裕量要求,单电源可能意味着信号摆幅降低,这可能导致SNR降低;双电源供电必须产生负电源轨,增加了复杂性,但由于可用裕量增加,信号摆幅可以更高,因此SNR性能高于单电源情况。从表1可以看出,我们使用了+7V/-3V的不对称电源,这种电源电压配置可提供足够的裕量以确保输入和输出范围得以保持。

2.VBias如图1所示,此信号用于将第一级的输出信号电平转换为与ADC输入匹配所需要的共模电压电平。从图1可以看出,这是通过使用电阻分压器来简单实现的,其中基准电压Vref用作源。

电容C5用于消除分压器产生的噪声。

注意:

• 驱动器网络的阻抗应等于反馈网络的阻抗。这一点在无法使用内部偏置电流抵消功能时很重要。这种配置将确保由偏置电流引入的额外失调电压会被降低。

• 如果使用内部偏置抵消功能,则应使用高电阻值,以降低该分压器网络的功耗。

3.为减少失真误差,RC滤波器应使用高质量电容(如C0G (NP0))和电阻。

4.使用大于计算值的标准电阻值。

5.如果不关心功耗问题,则两级的反馈电阻和增益电阻值可降至301Ω,以提高ADC和驱动器信号链的SNR性能。

(讨论参考图1)

• 信号调整和电平转换

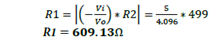

• 使用转换函数求解R1

应该注意的是,对于低电阻值,LTC6228的电压噪声占主导地位。随着电阻增加,电阻噪声开始占主导地位。随着电阻继续增加,电流噪声占主导地位。

如果选择R2的电阻值为499Ω,则设计的噪声和功耗可以取得良好的平衡。

求解R1

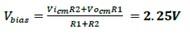

• 计算VBias电压值。这是利用Vi和Vo的共模电压来完成的。目标是将第一级放大器的输出电平转换为2.048V。

Vocm = 2.048V且Vicm = 2.5V

然后计算Vbias,如下所示:

• 计算比率  ,确保达到所需的偏置电压(Vbias)。假设R8 = 499Ω可在输入引脚处实现平衡阻抗,然后计算R7。分压器网络的噪声由C5滤除

,确保达到所需的偏置电压(Vbias)。假设R8 = 499Ω可在输入引脚处实现平衡阻抗,然后计算R7。分压器网络的噪声由C5滤除

• 电路噪声分析:

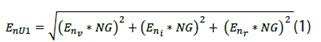

• 第一级输出 - 电压噪声计算

第一 级输出端的总电压噪声( )可使用下式计算:

)可使用下式计算:

其中:

– 运算放大器的电压噪声,LTC6228为

– 电流噪声 * 源阻抗引起的噪声

– 电阻噪声

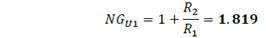

计算第一 级的噪声增益:

求解电流噪声引起的电压噪声贡献 。根据LTC6228数据手册,电流噪声密度为

。根据LTC6228数据手册,电流噪声密度为 。

。

• 第二 级输出 - 电压噪声计算

使用相同的步骤计算第二 级的总电压噪声 。

。

利用公式1和上面计算的值,第二 级的 为:

为:

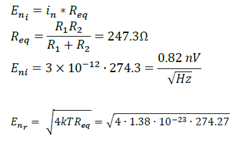

• 噪声带宽计算

计算每一级的有效噪声带宽,以将电压噪声转换为有效值噪声。

使用二阶滤波器的第一 级有效噪声带宽

使用以下公式求解有效噪声带宽BWn。这里,k为参考砖墙LPF的校正因子,在本例中它是1.22,n为滤波器的阶数。

第二 级有效噪声带宽:三阶 滤波器

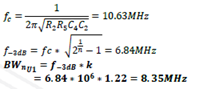

• 噪声谱密度至有效值噪声的转换

将各级的频谱密度转换为等效有效值噪声。

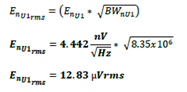

求解

求解

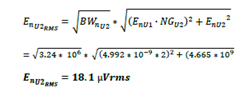

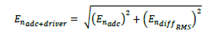

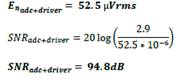

• 计算ADC驱动器总噪声

计算ADC驱动器的总差分电压噪声。

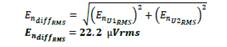

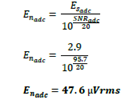

• ADC噪声计算

求解满量程输入信号的ADC电压噪声。使用4.096Vp或2.9Vrms,SNRadc = 95.7dB。

• 信号链SNR计算

根据计算出的ADC驱动器和ADC噪声计算预期的SNR性能。

a. 满量程输入信号

b. -1.7dBFS输入信号:

其中 -1.7dBFS = 2.38VRMS

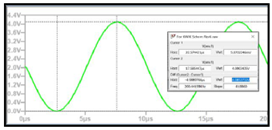

图1中电路的性能是使用LTSpice仿真工具进行仿真的,以确定是否符合主要目标规格。

从仿真试验台得到的结果如图2-图6所示

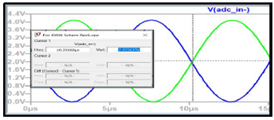

图2.– 输入信号调整

图3.输出共模电压VOCM

图4:差分输出

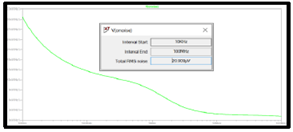

图5 RMS差分噪声

图6.总噪声,ADC + 驱动器

参数 | 设计目标 | 仿真 |

输出单端 | 4.096 Vp | 4.085 Vp |

输出共模电压 | 2.048 V | 2.054 V |

差分输出 | 8.192 Vp-p | 8.189 Vp-p |

ADC驱动器噪声(RMS) | <38.46 µV | 22.2 µV |

驱动器 + ADC噪声(RMS) | < 61.3 µV | 52.5 µV |

使用LTC6228评估演示板和LTC2387-18评估演示板获取测量结果。对于本例,输入信号设置为-1.7dBFS。此信号链的实测SNR为92.13 dB。该结果比计算出的SNR (93.1 dB)低大约1 dB。1 dB的差异很可能是由于电路板的寄生效应和所用元器件的容差导致的非理想效应。为实现预期的满量程SNR,将测量值增加1.7dB,结果将达到93.83dB,高于电路设计的目标SNR性能。

参数 | 设计目标 | 测量值 |

SNR | 93.5 dB | 93.8 dB |

参数 | 规格 |

Vos最大值 | 95µV |

IBias最大值 | -44µA |

GBP典型值 | 0.88nV/√Hz |

Iq | 16mA |

Vs范围 | ±5V |

参数 | 规格 |

分辨率 | 18位 |

FSample | 15Msps |

输入类型 | 单端,差分 |

Vin范围 | ±Vref |

SNR | 95.7 dB |

图7 – 测量的总SNR,ADC + 驱动器