Hot Chips 2023 :世界首颗面向数据中心的RISC-V 处理器,每周期可解码8条指令

2023-09-12 12:34:39 EETOPHot chips的全称是A Symposium on High Performance Chips,于每年八月份在斯坦福大学举行。不同于其他行业会议以学术研究为主,HotChips是一场产业界的盛会,各大处理器公司会在每年的会上展现他们最新的产品以及在研的产品。

我们不但看到了来自英特尔、AMD、Arm这些传统处理器巨头的展示,还看到了存储双雄三星和SK海力士的分享。此外,RISC-V服务器芯片新贵Ventana也在本届大会上分享了公司Veyron V1的细节。

Ventana Veyron V1 被认为是首款面向数据中心的RISC-V处理器。接下来让我们看看该款处理器有何过人之处。

以下内容来源于中国台湾媒体科技新报,作者:痴汉水球

处理器业界一直有一种观点:Arm 是下个RISC / Unix 服务器,而RISC-V 是下个Arm(Arm Is The New RISC / Unix,RISC-V Is The New Arm)。

云端巨头纷纷自行打造处理器,继Calxeda、Applied Micro、AMD、Marvell、Nvidia和三星等制造Arm服务器芯片的第一波尝试,博通(Broadcom)、高通(Qualcomm)和Nuvia第二波努力,Arm指令集兼容处理器由AWS自研Graviton和Arm推出Neoverse引领第三波浪潮, 终于冲破数据中心大门。

对崭新工作覆载,云端巨头也没有「非 x86 不可」需求,同等性能的云端实例(Cloud Instance),相较 x86,Arm 也有 30%~40% 性价比优势,注定 Arm 成为超大规模云服务的首选。

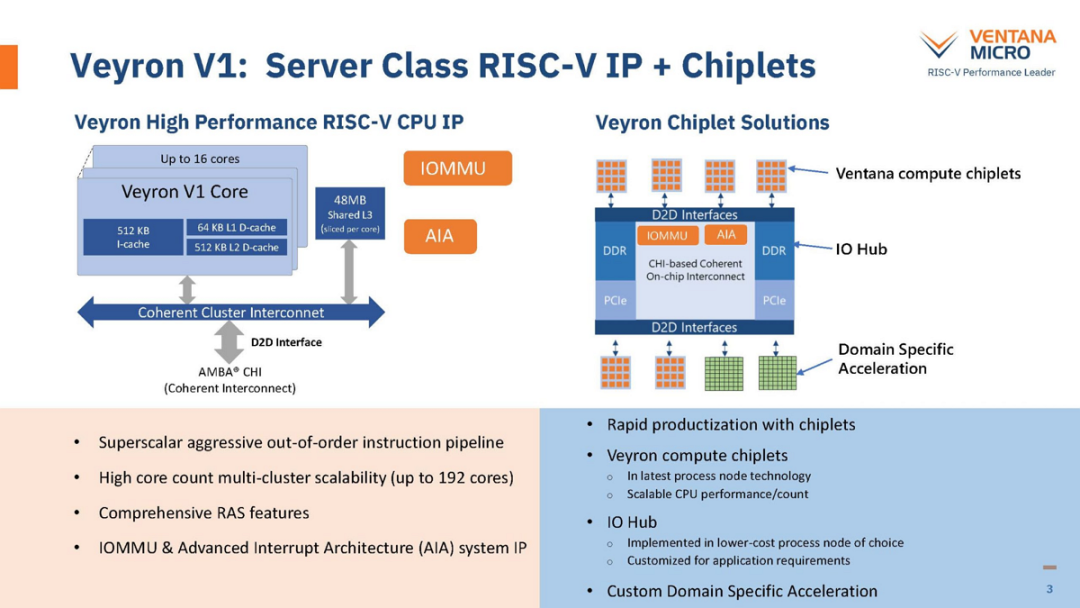

▲ 兼容 RISC-V 指令集的 Veyron V1 是首款「数据中心等级」RISC-V 处理器。 分别掌握移动平台和高效能运算市场的Arm与x86,近来因自由度极高崛起的RISC-V多半用于低功耗嵌入式平台,但也不乏企图将RISC-V推入数据中心的公司。新创Ventana Microsystems 2022年12月发布兼容64位RISC-V指令集的Veyron V1处理器,采用类AMD EPYC的Chiplet设计,允许客户购买CPU模组和I/O Hub(含存储器控制器和PCIe),最多可扩展到192个核心(12个CPU模组),然后整合自己的加速器,实作出一颗完整芯片。

▲ 对还不知道客户在哪里的新创公司,目标不外乎有讲跟没讲一样的「只要我们能找到需求」。

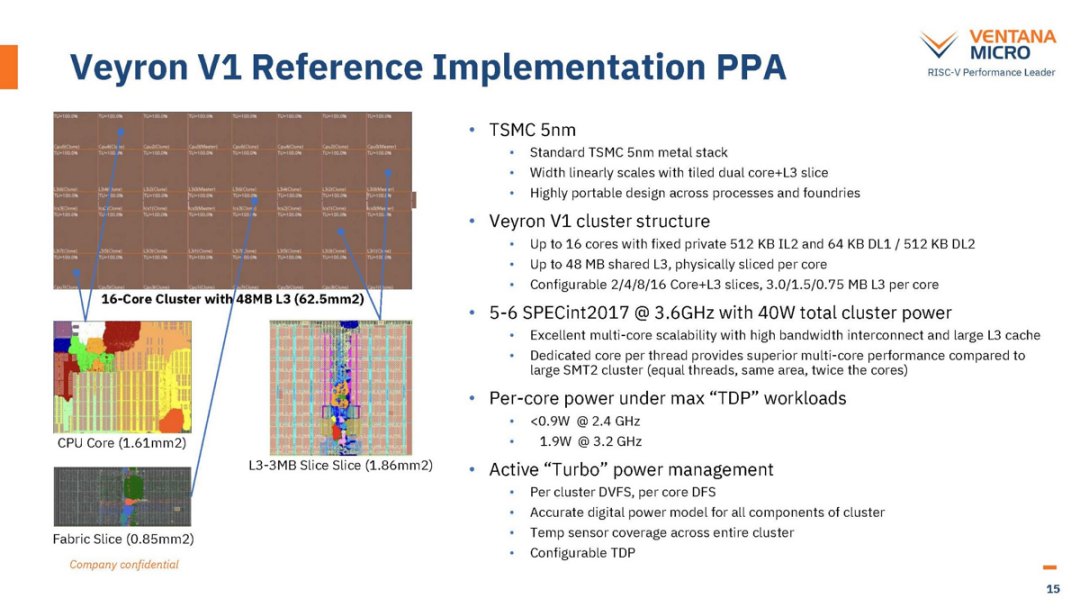

▲ 一个Veyron V1处理器CPU Chiplet含16个核心(台积电5纳米),接着跟有DDR内存控制器和PCIe等功能的I/O Hub(推测是台积电6纳米)结合,最多可延展至192个核心,并整合特定领域加速器。

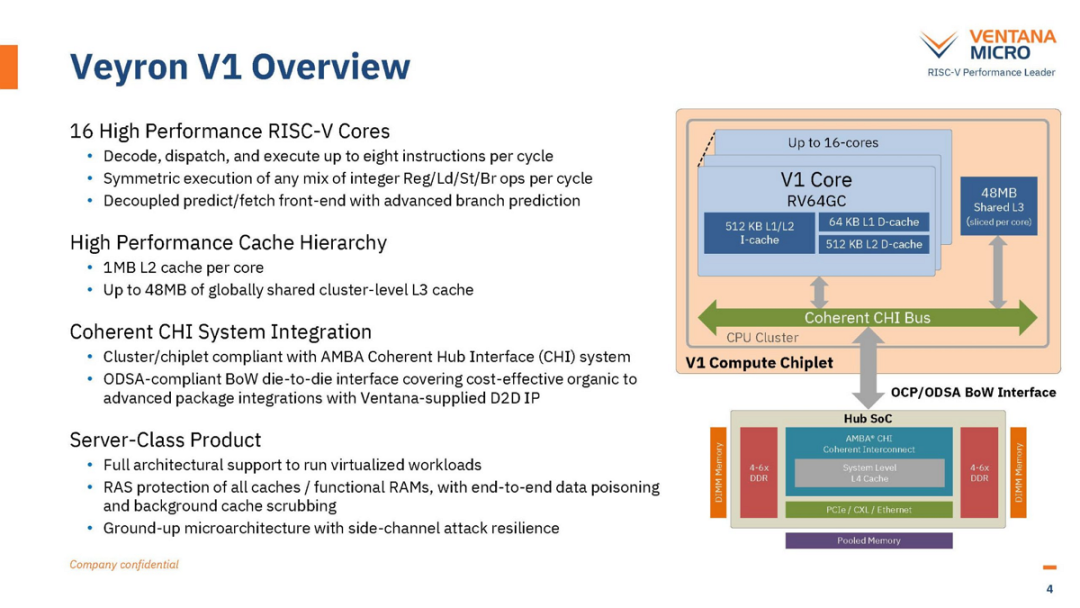

▲ 更多Veyron V1处理器关键规格:每个时钟周期最多可解码8个指令、每个核心有1MB L2快取,全部核心共享的L3快取最高容量48MB,服务器该有的特性如虚拟化、内存数据保护、和防御旁路攻击(Side-band Attack)等。

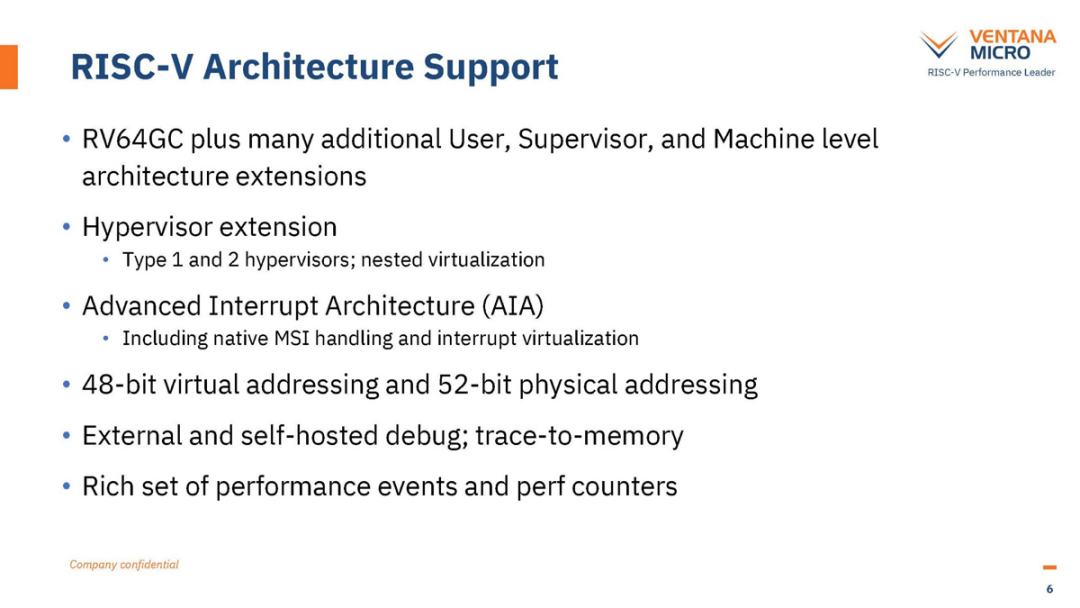

▲ 对应指令集以 RV64GC(意指 RISC-V 64-bit, extensions G and C) 为基础再延伸。让人讶异的是,Veyron V1 支持「可在虚拟机架设虚拟机器」的巢状虚拟化(Nested Virtualization),这个连 Arm Neoverse N1 都做不到。

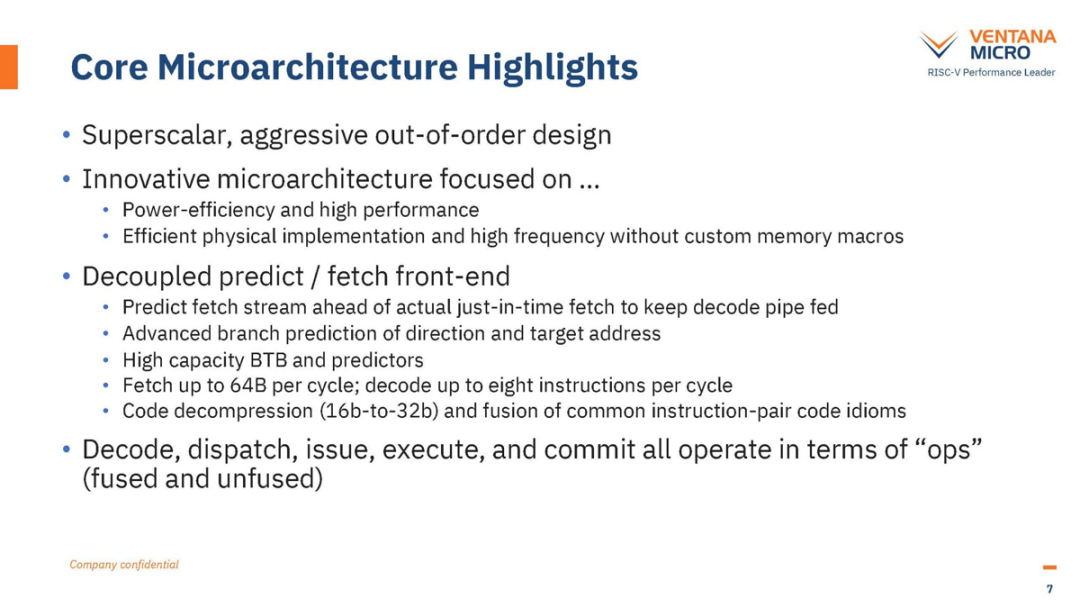

▲ Veyron V1 核心微架构的相关细节,但说穿了跟其他高效能处理器如出一辙,像追求能效、与指令管线解耦的分支预测与指令撷取、执行单元将部份相连指令融合为单一运算等。

RFQZnpKAJ5eztOrzTCHa7OvwgjA/640?wx_fmt=png" data-w="1080" data-index="8" src="https://www.eetop.cn/uploadfile/2023/0912/20230912123539468.jpg" _width="100%" crossorigin="anonymous" alt="图片" data-fail="0" style="margin: 0px; padding: 0px; outline: 0px; max-width: 100%; box-sizing: border-box; overflow-wrap: break-word !important; vertical-align: middle; height: auto !important; width: 677px; visibility: visible !important;"/>

▲ Veyron V1 指令快取颇具特色:充当 L1 / L2 大型化 512kB 指令快取,搭配一块当指令循环缓冲区(Loop Buffer)的超小型 L0 快取。

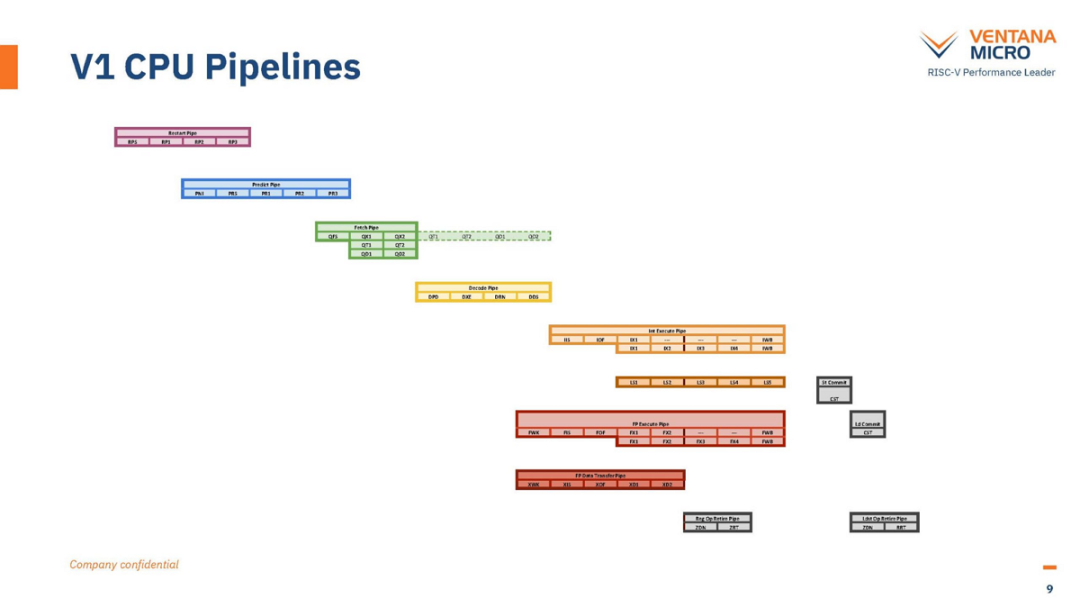

▲ Veyron V1 指令流水线全貌,坦白讲,画成这样的确很难理解。

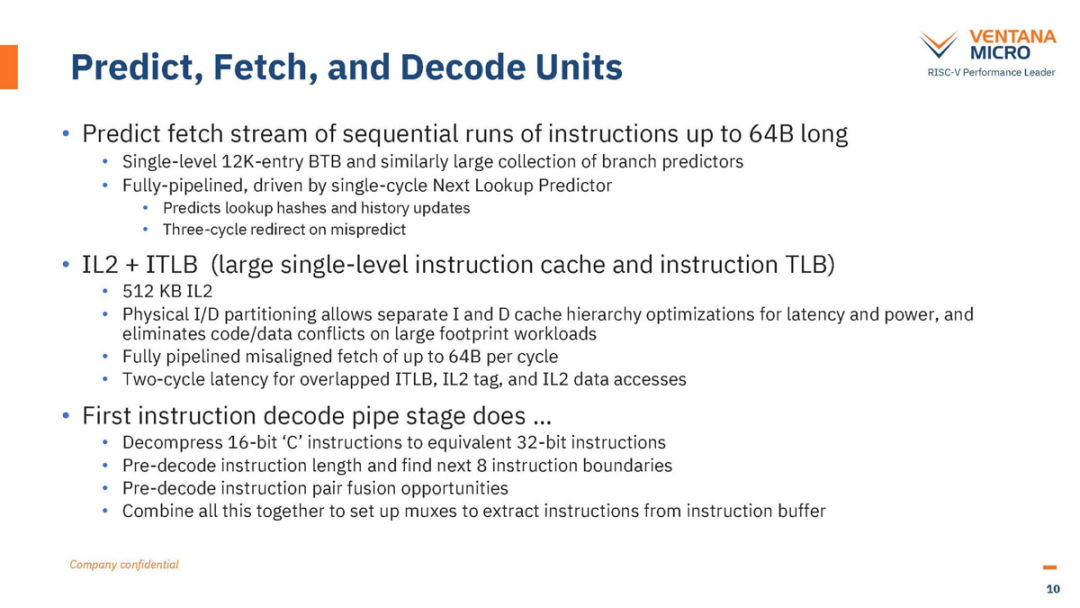

▲ Veyron V1 为了确保每时钟周期可撷取并解码 8 个指令,从分支预测、指令快取、指令 TLB、指令撷取到指令预先解码,都要有因应配套措施。

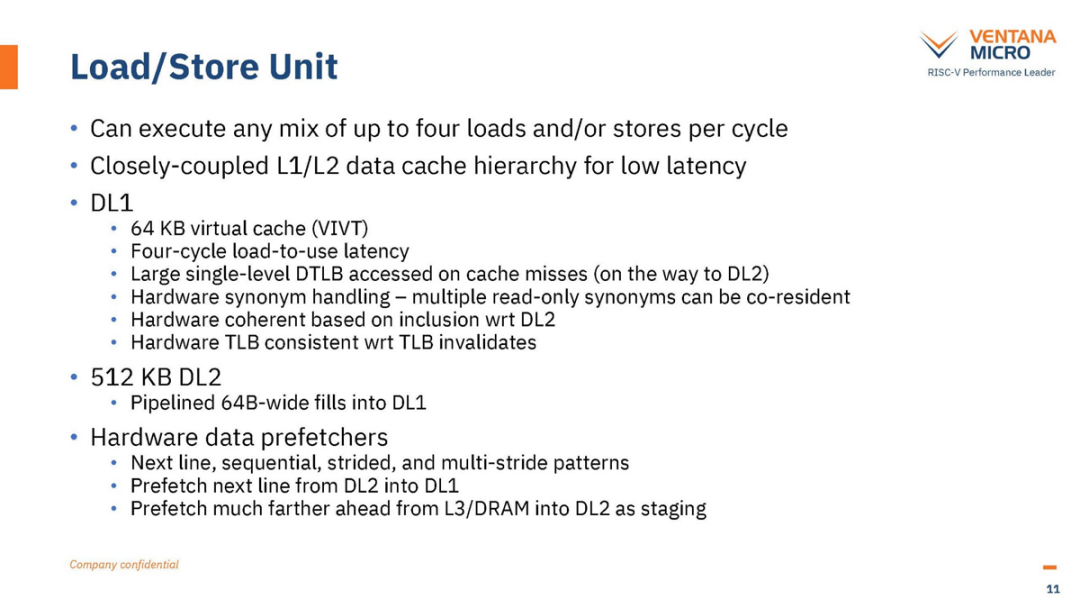

▲ Veyron V1 内存加载和回存单元,每时钟周期可同时执行总计四个加载/回存。

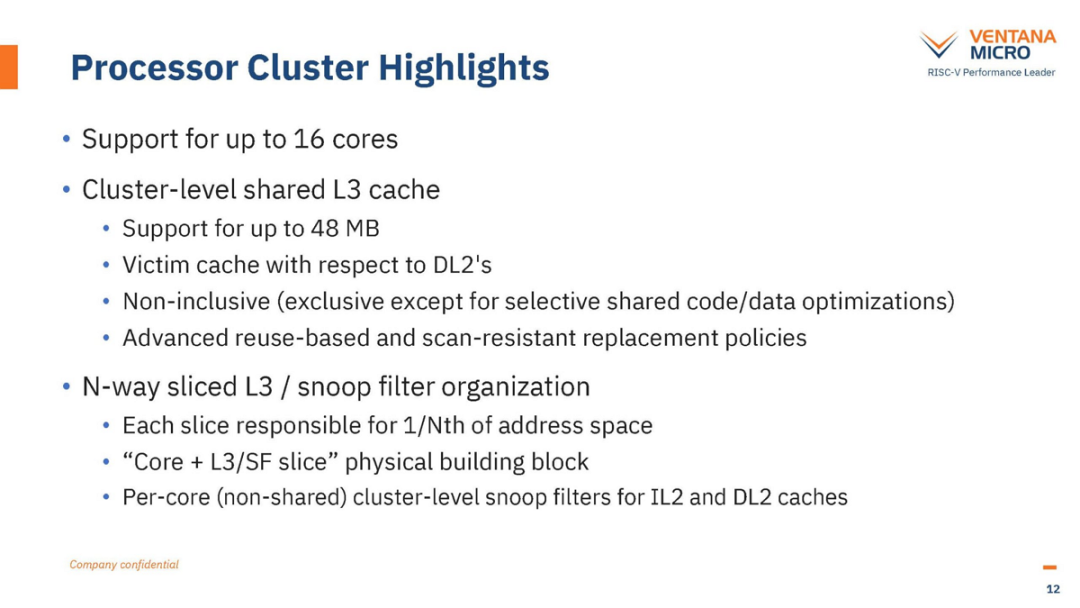

▲ Veyron V1 单一 CPU 模组最多 16 核,L3 快取最高容量是48MB,并兼具快取数据一致性协议的窥探过滤器(Snoop Filter)角色。

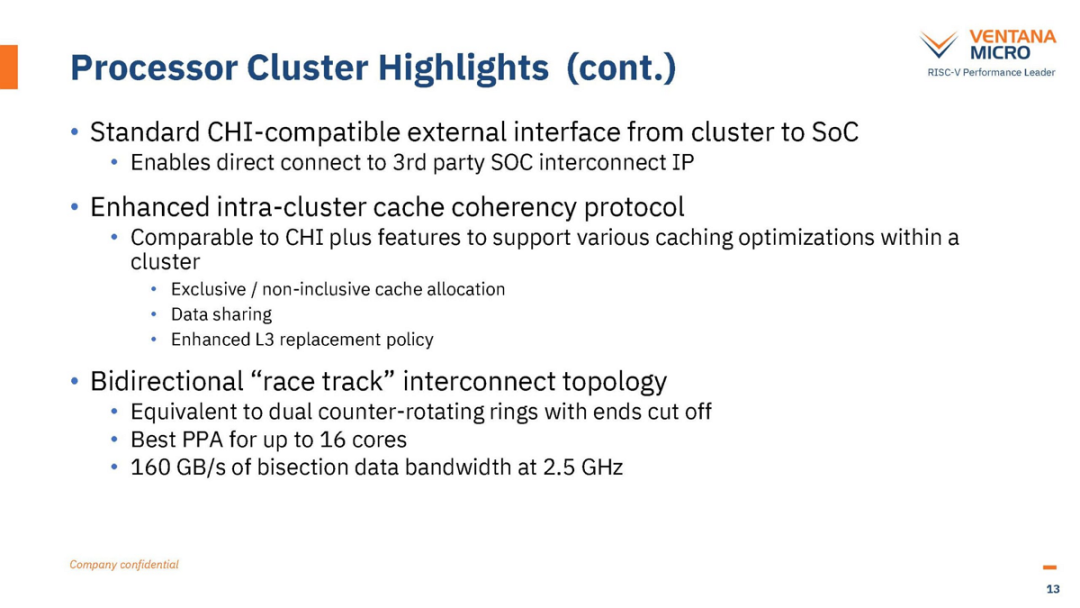

▲ Veyron V1 打从一开始就走 Chiplet 路线,兼容 Arm 制定的 AMBA CHI(Coherent Hub Interface)接口。

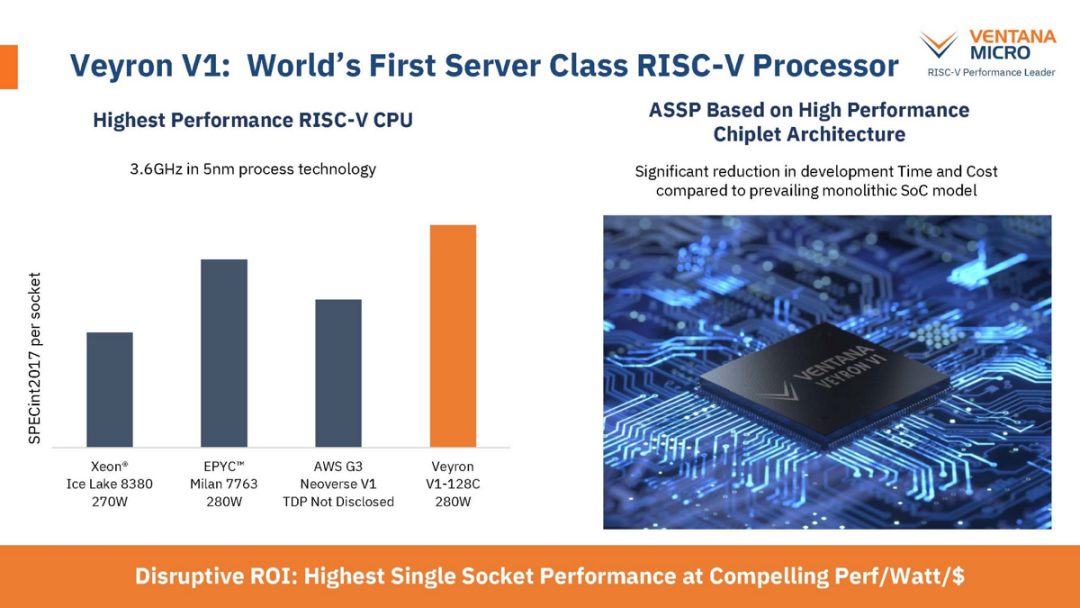

▲ 128核Veyron V1,主频为3.6GHz、功耗280W时,性能可超越40核英特尔Xeon8380、64核AMD EPYC7763和64核AWS Graviton3,但能否抗衡英特尔第四代Xeon-SP和AMD第四代EPYC就有点存疑。

▲ Veyron V1的CPU模组使用台积电5纳米制程参考实作:16核心结合48MB L3快取内存(每核心3MB),耗电量约 40W。 但有件事不得不提:Veyron V1 看来并没有 SIMD 或向量执行单元,这对上有 AVX-512 的 AMD Zen 4c 会非常吃亏。 至于「RISC-V进军数据中心」,Ventana Microsystems 的Veyron V1处理器可谓开了第一枪,但缺乏矢量运算能力的Veyron V1,追求吞吐量应用(如视讯编码器和绘图相关)会非常吃亏,即便下一版Veyron V2补回,RISC-V生态系统依然远不如Arm和x86成熟,必须另外编写软件支持向量扩展。以前Arm试图将自己塑照成x86替代品的过程,就多次面临软件支援难题,RISC-V只会面对更艰巨的挑战。 Ventana Microsystems计划是,客户应能在第二季或第三季收到Veyron V1处理器样品,届时就能知道世界首颗数据中心等级RISC-V处理器,究竟有多大能耐。