更小、更耐用!硅电容器后势可期,可望取代MLCC 部分应用市场

2023-09-19 11:28:01 technews(台) 作者:Evan单 MIM 或多 MIM+3D 纳米结构=更高静电电容值

当前硅电容器在结构上多半采用三层式「金属/绝缘体/金属」(Metal-Insulator-Metal,MIM)形式,另外也有多 MIM 结构的硅电容器,其每一个 MIM 结构都负责蓄存一部分的静电电容,多个 MIM 堆叠可以增加总静电电容值。

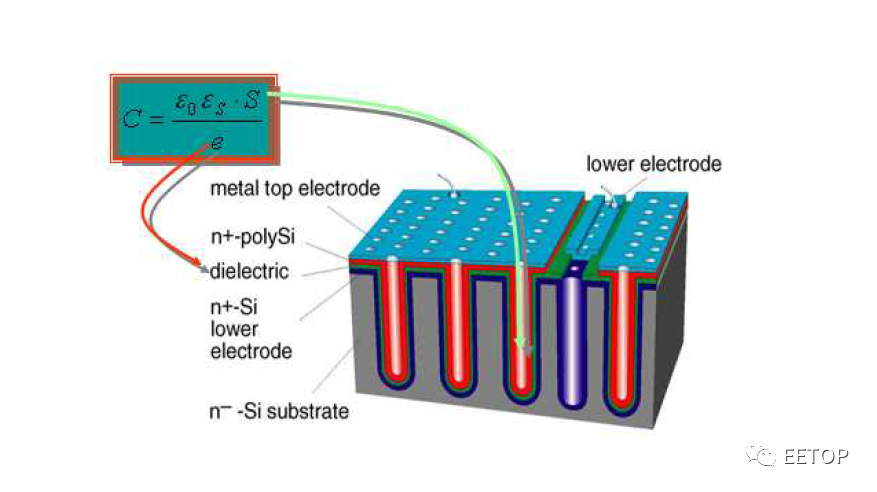

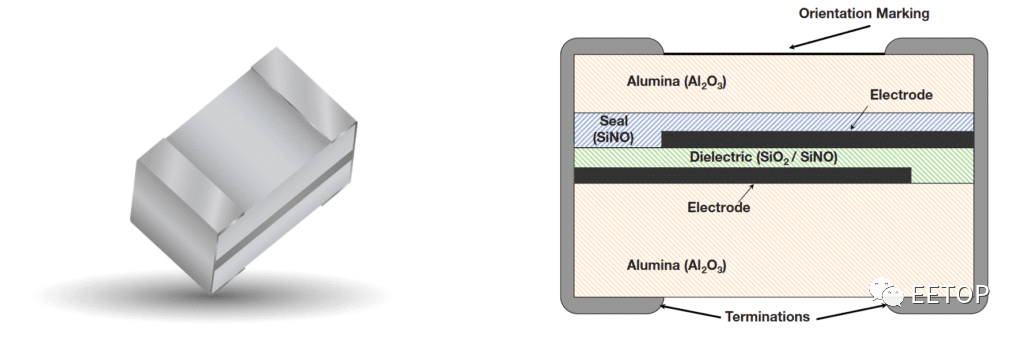

在绝缘体部分,当前硅电容器多半采用二氧化硅(Silicon Dioxide,SiO2)或氮化硅(silicon nitride,Si₃N₄)等绝缘硅介电质(Silicon dielectrics)材料,进而形成「金属/绝缘层/半导体」(Metal-Insulator-Semiconductor,MIS)或金属/氧化物/半导体」 (Meta-Oxide-Semiconductor,MOS)等三层式结构。两者皆为当前高密度电容器的主要绝缘材料,已然成为业界追求高稳定性、高可用性及耐高温等恶劣环境应用的最佳选择。

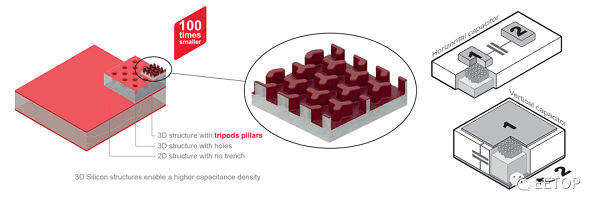

日厂村田制作所(Murata Manufacturing)旗下子公司MIPS(Murata Integrated Passive Solutions,前身为法国硅被动元件厂商IPDiA,2016年村田收购,2017年更名)的高密度硅电容器技术便是采用内埋在非晶基板的单MIM或多MIM结构。高密度硅电容器是采用半导体MOS制程开发,并使用3D奈米结构增加更高的电极表面积,进而获得更高的静电电容值。

▲ 3D 结构提升电容值示意图。(Source:Murata)

当前硅电容器所采用的主流半导体技术莫过于深沟式(Deep Trench)技术,例如美商予力半导体(Empower Semiconductor)推出E-Cap品牌硅电容器便采用深沟技术。不过,爱普科技(AP Memory)新推IPD硅电容器产品线以自家擅长的3D DRAM堆叠技术开发。

随着高度整合、高性能与微型化等需求的不断增长,高密度超深沟硅电容器开始受到市场青睐,实现被动元件主流技术莫过于被动整合连接基板(Passive integration connective substrate,PICS)制程技术,制程能结合多芯片模组(multi-chip module,mcm)和芯片直接封装(Chip onBoard, COB)等技术,开发出体积更小的超低功耗组件。制程技术不但能将许多基本功能整合到单一产品,降低制造成本,同时有助硅电容器容积效率持续提升。

▲ PICS 技术高密度深沟电容器剖面图。(Source:Murata)

相对于传统电容器,硅电容器具备许多显著的优势,首先是高稳定度,即使在高温下依旧稳定如常,目前最大耐受高温可达250°C,这使它成为适用航空、车用、军用乃至石油勘探等恶劣环境应用的最佳选择。虽然组件仍有最大电容值的限制,但基本上不受电容老化的影响(MIPS硅电容器使用寿命至少10年),即使面对会让MLCC电容器大受影响的直流偏压,可靠性和电容值都不会因此下降。

其次,高密度硅电容器有助于带动高性能零组件的微型化发展,进而有效降低电子元件的功耗与成本。以MIPS新推的硅电容器而言,厚度仅40μm,比起MLCC电容器薄得多。再者是极佳的漏电流(Leakage current)稳定性表现,对于传统电容器而言,高温、应力、充电电压乃至介电质厚度都会对漏电流造成影响。由于硅电容器具备良好的绝缘性能及绝缘电阻值,因而成为耦合、阻隔及时序电路的最佳选择。

此外,由于高温硅电容器具备更低失效率(FIT Rate),因此比起故障率极高的传统电容器,能提供更佳的可靠度与可用性。就村田制造作所网站指出,当前硅电容器可靠性可达MLCC电容器的10倍。

▲ IPDiA 硅电容器。(Source:DigiKey)

▲ IPDiA 硅电容器。(Source:DigiKey)

爱普科技说法,传统电容通常放在电路板上,随着高效能 SoC 的功耗愈高、电压愈低,电容器因此被迫移至引脚侧(land side),以便更靠近 SoC。但传统MLCC电容器受限于体积与密度并无法满足这样的需求,这样的重责大任便落到高密度、超薄的硅电容器身上。

不可讳言的,硅电容器当然也有一些值得改进的缺点,包括有限的最大电容值以及漏电荷问题。由于电容值会与二氧化硅介电质材料面积成正比,而与二氧化硅介电质的厚度成反比,因此电子元件制造商一直在缩减二氧化硅介电质的厚度,来满足小型化和高密度微电子元件的需求。但偏偏二氧化硅介电质薄膜缩得愈薄,漏电荷的状况反而会更严重,如此一来,电容器便难以储存电荷。目前针对这两个主要问题的解决之道,除改进制程外,重点会放在寻找替代性介电质。

拜硅电容器优势所赐,硅电容器完全兼容支持MIS / MOS后端技术,所以能做为被动整合平台的一部分。再者元件也适合以异质集成的方式结合CMOS、MEMS、多芯片模组或覆晶接合(flip-chip)等各种技术,应用于系统级封装(system in chip,SiP)或系统单芯片(system on chip,SoC)。组件且适用单颗芯片的表面黏着(SMD)电容器的开发。

▲ 射频薄膜硅电容器架构图。(Source :AVX)

目前市场主要硅电容器供应商大致包括AVX、MACOM Technology Solutions、Microchip Technology、Murata Manufacturing、Skyworks Solutions、台积电、TDK及Viking Tech等公司。市调公司Transparency Market Research指出,2021年全球硅电容市场规模约15.8亿美元,预估2022~2031年年均复合成长率(CAGR)为5.4%。相信不久的未来,硅电容器将会在网络、通讯、光通讯、医疗、车用及高可靠性用途等市场发光发热。