AI芯片市场:先进封装能力是关键差异化因素

2023-07-25 12:23:15 EETOP来源:EETOP编译自counterpointresearch

先进封装提供了一个很好的杠杆,可以提高整体芯片性能,超越传统的晶体管几何缩放,并在未来十年扩展摩尔定律。先进封装分为垂直堆叠芯片或晶圆的前端 3D 和通过 RDL(再分配层)或中介层水平互连芯片的后端 2.5D CoWoS。

随着人工智能应用的需求,HBM 成为主流

先进封装和晶圆制造技术的结合可以满足计算能力、延迟和更高带宽的要求,特别是对于高性能计算芯片。用于在数据中心训练人工智能模型的人工智能加速器需要最高的可用内存带宽。与内存受限的早期系统不同,当前的数据中心架构使用多种技术来克服内存瓶颈。高带宽内存 (HBM) 是广泛实施的用于提高带宽和内存容量的解决方案之一。尽管传统上人工智能一直是一项小众技术,但它一直是GPU中 HBM 的重要驱动力。

HBM 技术的工作原理是将 DRAM 芯片垂直堆叠在一起,并通过 TSV(硅通孔)和微凸块互连。因为 DRAM 是堆叠的,对于人工智能训练和高性能应用程序,HBM 每秒可以提供 TB 级的处理能力,这是人工智能和高性能计算应用程序所需的重要处理能力。虽然 HBM 为数据中心 AI 加速器所需的片外存储器提供极高的带宽,但需要权衡 HBM 的成本和热限制。随着 DRAM 堆栈和SoC被放置在单个封装基板中,随着每次迭代的领域进步、性能改进和功耗降低,HBM 正变得越来越主流,推动了其在人工智能应用中的采用。

CoWoS 使用 HBM 封装高级逻辑的主要驱动力

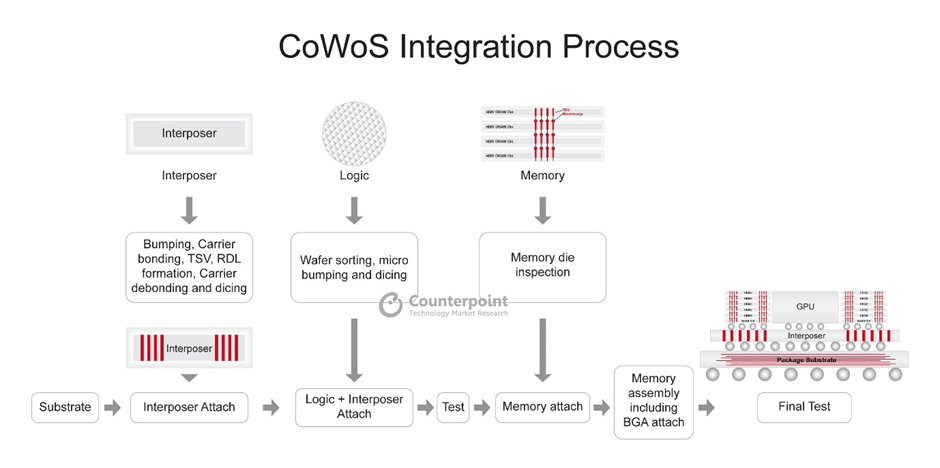

广泛使用的集成技术之一是CoWoS(基板上晶圆芯片),这是一种2.5D IC集成技术,通过将逻辑计算和HBM芯片安装在硅中介层上,然后直接放置在封装基板上来集成逻辑计算和HBM芯片。TSV/RDL 中介层适用于极细间距、高 I/O、高性能和高密度半导体 IC 应用。

逻辑电路和 HBM 首先并排键合在硅中介层上,形成晶圆上芯片(CoW),在器件之间具有细间距和高密度互连布线。每个 HBM 均由带有微凸块的 DRAM 和带有直通 TSV 的逻辑基座组成。硅通孔 (TSV) 是支持 2.5D 和 3D 高级封装的功能。TSV 是电气连接路径,是穿过硅晶圆或芯片的短垂直柱,可实现更小的封装尺寸和更密集的互连,通过缩短电气传输距离来提高电气性能,并实现 HBM 等产品中使用的多个芯片的堆叠。最后,在封装基板上完成具有较大凸块的 TSV 中介层的组装。

CoWoS 也是行业发展的瓶颈

多年来,CoWoS 技术开发的重点是支持不断增加的硅中介层尺寸,以支持整个封装中的处理器和 HBM 堆栈。如今,通过 TCB 方法采用 C2 凸块的 CoW 是硅对硅倒装芯片接合最常用的组装方法。CoW 倒装芯片采用一种称为混合键合方法的无凸块技术,目前正在研发中,多年来将获得关注。

CoWoS最近成为AI出货量的主要瓶颈。在NVIDIA、AMD、Broadcom和Amazon的推动下,提高 CoWoS 容量以满足不断增长的需求一直是焦点。

应对 CoWoS 增长的挑战

为了应对这些挑战,现有参与者需要通过提高产能以及与价值链参与者(OSAT、中介层制造商和封装设备供应商)的合作来实现供应链多元化。

纯晶圆代工厂应该做什么?

台积电在 CoWoS 方面存在产能限制,为 NVIDIA 和其他客户造成了一些瓶颈。原因之一是来自设备供应商和制造中介商的瓶颈。因此,台积电应该寻求合作,并可能外包给合作伙伴,这将有助于稳定中短期销量,并满足人工智能和高性能计算应用中对先进封装不断增长的需求。因此,从长远来看,台积电应该与设备制造商合作,优化TCB(热压接合)和混合接合等CoWoS加工技术。

设备厂商应该做什么?

设备制造商应与代工厂密切合作,共同开发优化工艺来扩展 CoWoS 封装。例如,应用材料公司正在积极开发混合键合和 TSV 新技术,以推进异构芯片集成,帮助芯片制造商将小芯片集成到先进的 2.5D 和 3D 封装中。预计 KLA Tencor、Lam Research、ASMPT 和 BESI 等其他参与者也将开展类似的合作,以推动 CoWoS 封装或其他竞争技术(例如混合键合技术)的进步,从而改善细间距、I/O 密度和功耗。研究合作将为半导体和系统公司提供一整套工具和技术,用于开发和原型设计各种封装设计,并实现功耗、性能、面积、成本和上市时间的持续进步。

IDM 应该做什么?

三星和其他IDM厂商也积极寻求在先进封装市场分一杯羹,并增强其设计和制造能力,为高端解决方案建立足够的客户群。例如,三星电子的 HBM-PIM 技术将处理芯片和 HBM 等先进存储芯片与其专有的 2.5D 或 3D 封装技术集成在一起。三星开发了 HBM-PIM 作为其现有 HBM2 产品的潜在替代品,其中八个内存芯片的底部四个被包含 DRAM 和计算核心的芯片取代。通过在 DRAM 中进行一些计算,需要传送到处理器的数据量会减少,从而有效地加速神经网络并节省传输数据所需的功耗。随着这项技术的发展,

对于拥有成熟节点能力的 IDM 来说,先进封装也是一个机会,可以增强其现有产品组合的性能并占领重要的市场份额。

OSAT 应该做什么?

日月光 (ASE) 和 Amkor 等 OSAT 正在积极投资以扩大先进封装产品,但需要时间才能从上升趋势中受益。产量和产量是代工厂发展其先进封装平台的关键。这也对大多数传统OSAT公司进入该领域构成了障碍。然而,他们可以与领先企业合作并提高后端流程的能力。另一种选择可能是增加对成熟节点先进封装应用的研发投资,这将有助于为下一次经济好转做好准备,例如摆脱倒装芯片和引线键合。

如果 OSAT 不加入先进封装浪潮以在成熟节点中实现 PPA 优势,那么它们将面临严峻的考验。但如果他们现在开始投资,特别是在物联网、汽车和网络领域的人工智能应用方面,他们可以获得先发优势。

无晶圆厂供应商应该做什么?

NVIDIA 占据了当前 CoWoS 容量的大部分。由于 CoWoS 封装带来的好处,获得 AI 工作负载所需的高性能是可能的。该技术在各种中介层尺寸、封装尺寸和 HBM 立方体数量方面提供了灵活性,并以高性能计算应用所需的最高集成密度提供最佳性能。

随着人工智能在设备和行业中变得越来越普遍,苹果、特斯拉、谷歌和 Meta 等垂直行业参与者正在其产品中添加大量人工智能功能,并且还需要为其产品组合提供集成的人工智能计算。CoWoS 似乎是目前最好的选择。随着包括英特尔在内的其他竞争对手扩大其产品范围来满足人工智能需求,他们必须与同类最佳产品相匹配,而目前这些产品是通过 CoWoS 提供的。

从客户端计算的角度来看,随着行业开发能够在智能手机上运行的缩小版人工智能模型,并且用户需要智能手机上的人工智能模型,它可能会尝试 CoWoS。然而,目前在智能手机应用中实施 CoWoS 封装并不具有成本效益,替代封装技术将是一个更好的选择。