台积电美国工厂或将迈进1 纳米

2022-11-30 13:01:03 EETOP台积电 (TSMC) 计划进一步缩减其工艺节点技术。据国外科技媒体allaboutcircuits报道,台积电将在其亚利桑那州芯片工厂生产 3 纳米芯片,并可能计划生产 1 纳米芯片。

在半导体制造中,3nm 工艺是继 5nm 技术节点之后的下一个 die shrink,几大行业参与者都在争先恐后。较小的节点允许在给定区域放置更多晶体管,从而提高电源效率。

第一代 3 纳米芯片将能够将功耗降低近一半,同时大幅提高性能。

韩国科技巨头三星电子于 6 月在其华城和平泽半导体工厂开始大规模生产 3 纳米芯片,这是全球首家这样做的公司。

该公司的目标是到 2030 年在其逻辑芯片和晶圆代工业务上投资 1320 亿美元,并计划在德克萨斯州建设一家半导体工厂。该公司目前正在生产第一代 3nm 芯片,并计划在 2023 年开始生产第二代 3nm 工艺。

台积电作为全球最大的晶圆代工企业紧追三星,前几天张忠谋透漏,台积电计划在其亚利桑那州工厂生产 3 纳米芯片,第二家工厂正在规划中。

该公司在 4 月份表示,计划在未来三年内投资 1000 亿美元扩大其芯片制造能力,并计划在 2025 年生产 2nm芯片。

同时,在 2022 年 4 月,英特尔宣布了其制造工艺计划,从 Intel 7 转移到 Intel 18A;每一步都提供了相对于功耗的性能改进。虽然这家科技公司目前落后于台积电和三星,但它希望到 2025 年赶上并超越它们。

台积电将其名为 N3 的 3nm 技术描述为其现有 5nm 产品的全节点跨步。N3 芯片采用FinFlex技术,允许工程师在一个块内混合和匹配不同种类的标准单元,以优化性能、功耗和面积 (PPA)。

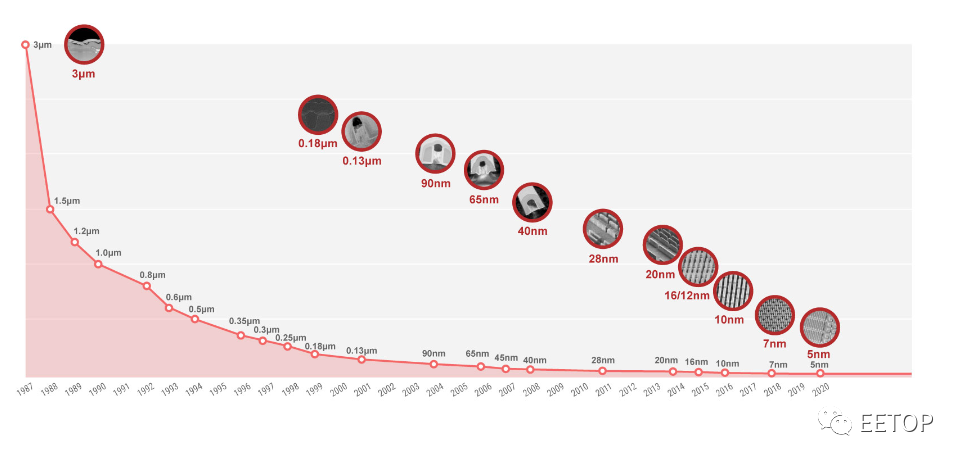

台积电专用代工工艺技术进步的图

该芯片的特性特别有利于制造具有大量内核的复杂设计,例如 CPU 和 GPU。该公司声称新技术将提供高达 70% 的逻辑密度增益,在相同功率下速度提高 15%,在相同速度下功率降低 30%。

推出时,台积电希望在 PPA 和晶体管技术方面提供最先进的代工技术,而 N3 技术可为移动和 HPC应用程序提供完整的平台支持。

台积电正在亚利桑那州建造一座耗资 120 亿美元的工厂。第一阶段是 5 纳米芯片,该公司已确认它仍有望在 2024 年开始生产。下一阶段虽然尚未最终确定,但将开始生产 3 纳米芯片。该公司表示,计划最初使用 5 纳米工艺每月生产约 20,000 片芯片。

尽管由于劳动力成本和与相关的供应链问题,建造该工厂的成本高于预期,但它仍在按计划进行,并且迫切需要满足该地区台积电客户的需求。

虽然 美国工厂的5 纳米芯片的生产尚未开始,但台积电与台湾大学 (NTU) 和麻省理工学院 (MIT) 一起在 1 纳米芯片的开发中稳步前进。

1纳米芯片技术首先由麻省理工学院的团队做出,然后由台积电进行优化,并由南洋理工大学的电机工程与光学系改进。关键研究成果是使用半金属铋作为接触电极可以降低电阻并增加电流,这将把能源效率提高到半导体的最高水平。去年5月积电发布了在 1nm 芯片上取得突破的联合声明,业界认为这一声明胜过了IBM先前关于开发 2 纳米芯片的声明。

据报道,台积电计划在桃园市龙潭区的工业园区建设一座 1 纳米晶圆厂。该基地由新竹科学园区 (HSP) 运营,台积电已在该园区运营两家半导体封装和测试工厂。尽管台积电尚未证实或否认该报道,但可以肯定的是,它已确认将继续投资台湾地区的先进芯片制造。

虽然 1 nm 芯片可能还没有准备好量产,但当它真的到来时,它将为电动汽车、人工智能和其他技术带来进一步的节能和更高的速度。