Rambus推出最新CXL 2.0控制器,内置业界领先零延迟IDE安全模块

2021-10-26 10:42:39 EETOP北京2021年10月26日 /美通社/ -- 作为业界领先的芯片和IP核供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布推出内置完整性和数据加密(IDE)模块的Compute Express Link™(CXL)2.0和PCI Express®(PCIe)5.0控制器。在CXL协议上实现超高速数据传输中的安全性,对于解决数据中心基础设施中的带宽瓶颈至关重要。IDE模块可监控并防止对CXL和PCIe链路的物理攻击。CXL需要极低的延迟,才能为目标用例实现load-store内存架构和缓存一致性链路。这款突破性的控制器由Rambus最近收购的PLDA工程团队研发,凭借内置的零延迟IDE模块,可支持在32 GT/s的最高速率下实现最先进的安全性和性能。

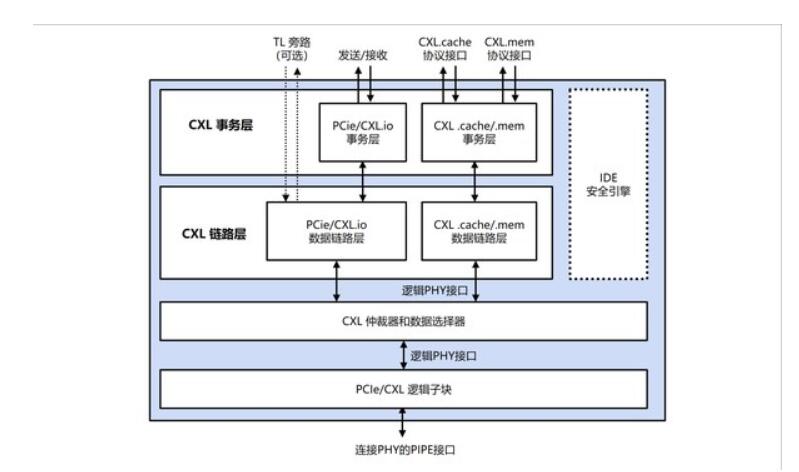

内置IDE安全模块的Rambus CXL 2.0控制器

Rambus首席运营官范贤志(Sean Fan)表示:“要在数据密集型应用中成功启用CXL使用模式,例如在处理器和附加的AI加速器之间共享内存,需要在超低延迟的前提下实现数据传输的安全性。此次零延迟安全控制器的推出,证明我们在最近收购PLDA之后,具备了加速开发CXL解决方案的能力,同时彰显了我们在提供集成式接口和安全IP解决方案方面独一无二的优势地位。”

此次发布的Rambus CXL 2.0和PCIe 5.0控制器均内置IDE模块,采用256位AES-GCM(高级加密标准,伽罗瓦/计数器模式)对称密钥分组密码算法,可确保通过CXL和PCIe链路传输的数据流的机密性、完整性和重放攻击保护,并简化芯片设计人员和安全架构师的工作。此类安全功能对于各种数据中心计算应用尤为必要,如AI/ML和高性能计算(HPC)等等。

主要功能包括:

更多信息:

关于内置IDE模块的Rambus CXL 2.0控制器和PCIe 5.0控制器,如需了解更多信息,请访问我们的网站:

CXL 2.0子系统:

PCIe 5.0子系统:

关注Rambus:

公司网址:rambus.com

Rambus 博客: rambus.com/blog

Twitter: @rambusinc

LinkedIn: www.linkedin.com/company/rambus

Facebook: www.facebook.com/RambusInc

微信:Rambus_China

关于Rambus

Rambus是一家业界领先的Silicon IP和芯片提供商, 致力于使数据传输更快、更安全。凭借30多年先进的半导体研发经验,作为高性能内存子系统研发先驱,解决了数据密集型系统所面临的内存与数据处理之间的瓶颈。无论是云端,边缘,或手中的互联设备,这些实时且沉浸式的应用均依赖于数据的吞吐率和完整性。Rambus的产品和创新提供更大的带宽和容量以及更高的安全性,以满足全球的数据需求并驱动着前所未有的用户体验。更多相关信息,请访问rambus.com网站.