如何解决复杂 SoC 集成挑战?

2025-05-27 09:22:17 EETOP随着半导体工艺节点不断微缩、多芯片集成需求增长,以及对高性能低功耗芯片的要求日益严苛,SoC(系统级芯片)的设计和集成变得前所未有的复杂。

真正的挑战不仅在于硬件集成,更在于如何高效管理海量设计数据,并确保所有团队(架构、验证、物理设计、软件等)基于一致、准确的信息协同工作。任何信息不一致或遗漏都可能导致严重的项目延误甚至流片失败。

当结合 Arteris 的技术背景来看这一挑战时,人们自然会想到硬件集成以及 NoC 技术的优势。传统上,人们可能认为 Arteris 的核心技术仅在于 NoC,但实际上,Arteris 提供的解决方案远不止于此。

本文将深入探讨 Arteris 如何通过其全面的EDA工具链来应对 SoC 集成挑战,并介绍其 Magillem解决方案如何提升设计效率与可靠性。 SoC 集成的主要挑战 现代 SoC 设计可能包含:500~1000 个 IP 模块、20 万~500万个寄存器、多种来源的IP(软核 IP、第三方 IP、内部遗留设计等)、频繁的设计变更(衍生设计、分区调整、重组优化)。 传统的设计方法(如手动管理电子表格、文档或分散的IP-XACT/SystemRDL 数据)已无法满足需求,这就可能导致: 团队协作低效:不同团队(RTL、验证、物理设计、软件)依赖不同数据源,易出现不一致; 错误难以早期发现:规格不匹配等问题可能直到后期才暴露,导致高昂的修复成本; 设计迭代缓慢:手动调整 RTL 层次结构或寄存器映射耗时数周,影响项目进度。 Arteris 的解决方案: 统一数据管理与自动化

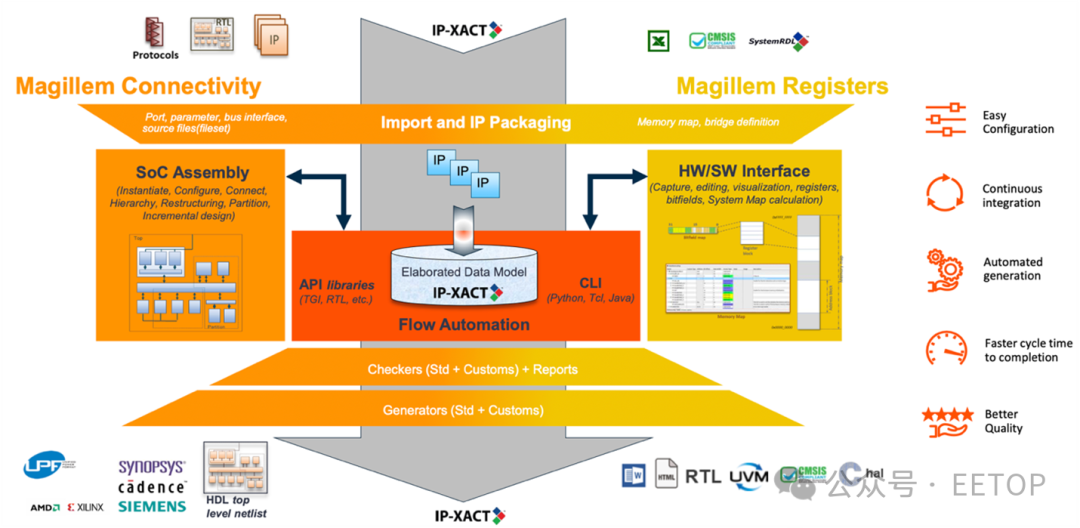

面对 SoC 集成中的海量 IP 管理、跨团队协作和数据一致性问题,传统方法已显得力不从心。 Arteris 的 Magillem 提供了一套标准化、自动化的解决方案,其核心理念是 “单一可信数据源”,确保所有团队基于同一套准确信息协同工作,同时大幅减少人工干预带来的错误和延迟。 1. 单一数据源:IP-XACT 标准化 现代 SoC 设计涉及众多团队——架构设计、RTL 开发、验证、物理实现和嵌入式软件——每个团队都可能依赖不同的数据格式(如电子表格、SystemRDL、IP-XACT 或自定义文档)。这种碎片化信息管理极易导致版本不一致,进而引发后期设计返工。 单一可信数据源,实现更高质量的设计 Magillem 采用 IP-XACT(IEEE 1685)作为统一数据模型,从根本上解决这一问题: 数据一致性:所有团队(硬件、软件、证)从同一数据库获取信息,避免规格冲突。 自动化接口:通过标准化 API和脚本环境,实 现设计数据的快速访问与更新。 IP重用与移植:封装 IP 的配置、连接性和寄存器映射信息,便于跨项目复用。 (注:Arteris 是 IP-XACT 标准的核心推动者,曾担任 Accellera 委员会联合主席,其解决方案深度融入这一标准。) 2. Magillem 核心功能:从集成到寄存器管理 IP-XACT提供了数据基础,而 Magillem 的自动化工具链则在此之上实现了高效设计集成。其功能覆盖两大关键领域。 (1)集成管理:解决 SoC 组装的复杂性 现代 SoC 可能需要集成数百个 IP,并处理复杂的总线协议、信号分割和层次结构调整。 Magillem 提供: 智能连接生成:自动检测总线接口,插入胶合逻辑,优化信号布线。 层次结构重组:支持模块的移动、合并或扁平化,适应物理设计的功耗和布局需求。 错误预防:在仿真前检查连接规则(如地址冲突或未对接信号),避免后期代价高昂的修复。 通过RTL重组功能,设计团队可以快速调整模块层次: 优化物理设计:缓解布线拥堵,改善时序。 多芯片集成:将大型 SoC 拆解为 Chiplet,提升良率。 快速迭代:设计变更(如 IP 替换)可在 1-2 天内完成,而非传统手工调整所需的数周。 (2)寄存器与内存映射管理:确保硬件/软件一致性 寄存器配置直接影响硬件功能和软件驱动开发。Magillem 的寄存器管理功能包括: 统一数据库:统一管理所有寄存器定义,支持参数化配置(如访问权限、复位值)。 自动化生成:同步输出 RTL、验证测试平台、软件头文件和文档,消除人工转录错误。 合规性检查:内置规则检查器(如地址重叠、未定义寄存器),提前拦截潜在问题。 这一流程尤其适合复杂内存映射场景(如多级子系统寄存器合并),确保硬件设计与软件预期完全匹配。 Arteris 如何助力 SoC 设计? 从数据到设计,全程可控 下图概述了 Arteris 为 SoC 集成提供的所有功能,以及支持的标准和 EDA 工具。 Arteris Magillem 的 IP-XACT 数据中枢和自动化工具链共同构成了 SoC 集成的“神经中枢”: 标准化:统一数据模型消除团队间的信息孤岛。 自动化:从 IP 连接到寄存器生成,减少人工干预。 可扩展性:支持从传统 SoC 到芯粒(Chiplet)设计的平滑过渡。 Arteris 的完整EDA工具链正在重新定义 SoC 集成方式。通过这一体系,Arteris 让设计团队能够专注于创新,而非淹没在数据管理的琐碎工作中。