台积电3DFabric先进封装技术最新进展

2023-06-18 12:00:43 EETOP6月8日台积电宣布开设一家先进的封装测试工厂Fab 6,以扩展台积电 3DFabric系统集成技术。这是一个重要的公告,因为与英特尔和三星的芯片封装军备竞赛正在升温。

Fab 6 是台积电首个一体式先进封装测试工厂,是台积电不断增加的封装投资的一部分。该晶圆厂已准备好量产台积电 SoIC 封装技术。请记住,当台积电说量产时,他们指的是 Apple iPhone 尺寸的量产,而不是工程样品或内部产品。

如今,封装是半导体代工产品的重要组成部分。它不仅是芯片级产品的差异化因素,还将代工客户的忠诚度提升到一个全新的水平。这将是至关重要的,因为小芯片革命已经站稳脚跟,使客户更容易独立于代工厂。然而,Chiplet 封装非常复杂,并且将因代工厂而异,这就是台积电、英特尔和三星花费如此多的资本支出来确保其在封装业务中居于领先地位的原因。

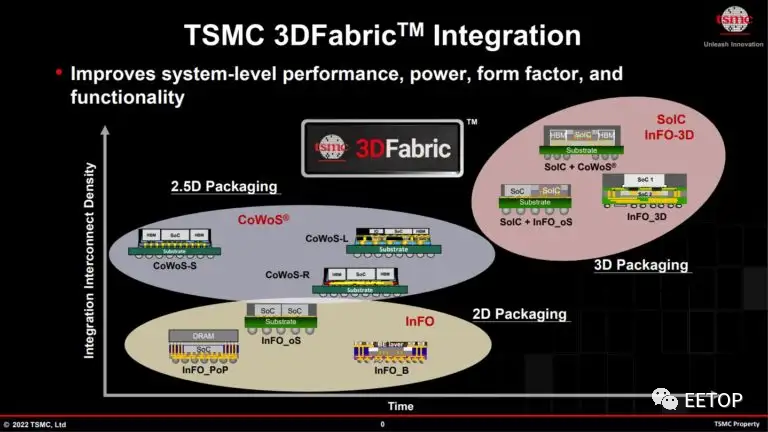

TSMC 3DFabric 是 3D 硅堆叠和先进封装技术的综合系列:

SoIC 堆叠芯片可以集成到 InFO 或 CoWoS 封装中,以实现最终系统集成。

CoWoS家族

台积电正在开发一种 CoWoS 解决方案,该解决方案具有高达 6 倍光罩尺寸(约 5,000 平方毫米)的 RDL 中介层,能够容纳 12 个 HBM 存储器堆栈。

InFO技术

对于移动应用,自 2016 年以来,InFO PoP 一直在为高端移动设备量产,并且可以在更小的封装尺寸中容纳更大、更厚的 SoC 芯片。

3D硅堆叠技术

SoIC-P 基于 18-25μm 间距 μbump 堆叠,适用于对成本更敏感的应用,如移动、物联网、客户端等。

SoIC-X 基于无扰动堆叠,主要针对 HPC 应用。其晶圆上芯片堆叠方案具有 4.5 至 9μm 键距,并已在 TSMC 用于 HPC 应用的 N7 技术上量产。

台积电以客户为中心的文化将成为小芯片封装革命的重要组成部分。通过与数百家客户合作,可以肯定台积电将为全球无晶圆厂和系统公司提供最全面的 IC 封装解决方案。