封装技术是功率半导体突破的关键!带你深度了解顶部散热封装

2023-04-27 12:07:45 未知最近,英飞凌的QDPAK及DDPAK顶部散热(TSC)封装技术入选JEDEC标准。JEDEC组织是由美国众多厂商联合发起,旨在为芯片行业制定通用标准的组织。目前,JEDEC标准已经是半导体行业公认的标准,并且它不设置专利门槛,所有入选的标准均可免费下载。对于入选JEDEC的企业标准来说,最大的好处,便是可以在整个半导体行业快速推行企业的技术及产品。

封装是功率半导体演进的突破口

过去的十几年中,半导体技术的演进,主要体现在晶圆部分,芯片的设计朝向更低的导通阻抗,以及越来越小的芯片尺寸发展。芯片的尺寸设计从最初的28纳米到14纳米,再到7纳米、3纳米,甚至2纳米、1纳米,其不断的向着极限工艺发起挑战。摩尔定律主要对数字化产生影响,而提高算力则是解决问题的关键,这就要求在单芯片的面积里尽可能多地放置代表0101演算速度的开关管。英特尔在今年年初就曾表示,2030年前将实现一个芯片封装上集成1万亿个晶体管的目标。

不过,每一个工艺节点的进步,随之而来的,就是在设计和制造过程中所需要的如天文数字般的成本。成本的上升正促使人们探索其它多种的选择,更高级的封装技术则是其中突破研发瓶颈的关键技术之一。而对于功率半导体而言其又有自身的特殊性。尽管其也强调在同样的晶圆上能够存放更多的晶胞,但其对于尺寸的要求却远大于CPU以及GPU,一般接近上百纳米。在这种情况下,芯片尺寸进一步缩小的空间非常有限。所以在这些综合因素的影响下,封装技术无疑是推进研发进展的突破口。

程文涛,英飞凌科技电源与传感系统事业部大中华区应用市场总监

英飞凌科技电源与传感系统事业部大中华区应用市场总监程文涛以硅基功率半导体为例,详细解读了封装技术在现代半导体产业中的重要地位。程文涛介绍,高压超结硅功率器件的FOM值基本已经达到了物理极限,在此情况下要想继续降低导通阻抗或者是实现更高的能效,封装技术是继续把硅的功率发挥到极致的必经之路。不仅是硅基半导体,现在大热的宽禁带半导体SiC/GaN也需要仰仗新的封装技术。

插件封装技术VS顶部散热封装技术

十年前,在功率半导体行业,千瓦及以上的大功率应用基本上是插件封装技术为主导。这些插件封装技术在当时的装配和封装工艺里面能使工程师最大限度地利用外加的散热片,非常高效地将芯片内部产生的热量散出芯片之外,让芯片能够工作在一个大功率的场景里面。但是随着物联网、5G、云计算等技术的不断发展和演进,万物互联的设备越来越多,下游厂商更加倾向于把整个设备的功率密度做得越来越小,或者说在同样的机架尺寸或者同样的安装尺寸里面,要传递的功率耗散越来越大,这两大发展需求都在迫使功率器件不仅要用更少的独立散热片,同时还需要把更多的热量均匀地散布到整个设备以外。而顶部散热封装技术就是英飞凌经过多年调研和考证而得出的有效解决途径。

贴片化是从带独立散热片的插件封装走向更高功率散热的第一步。一般贴片封装的散热主要是靠芯片底部跟PCB(印刷电路板)之间的接触,利用PCB铜箔把芯片产生的热量传导出去。程文涛分析说:“这样做的一个明显弊端在于,它需要耗费比较大的PCB铜箔面积,才能有效地把热量散发出去。如果在此期间不能用面积足够大的PCB铜箔,那么在芯片底部就会形成一个热点,而这个热点会给PCB带来很大的压力。”

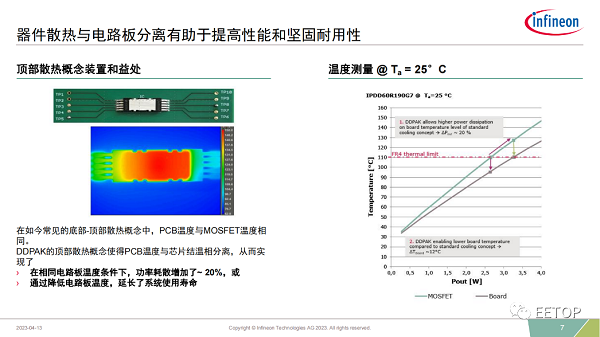

目前业界常用的PCB是FR4材质,该材质的最高温度上限为110度左右,在更高的功率设计中,底部散热封装无法通过贴片和PCB之间结合均匀地把更多热量散出去,导致这种散热方式走到了瓶颈。据程文涛介绍,英飞凌研发的顶部散热,通过在顶部增加一个薄薄的散热片,使得PCB温度与芯片结温相分离,从而实现了在相同电路板温度条件下,功率耗散增加了大约20%,而且通过降低电路板温度,延长了系统使用寿命。

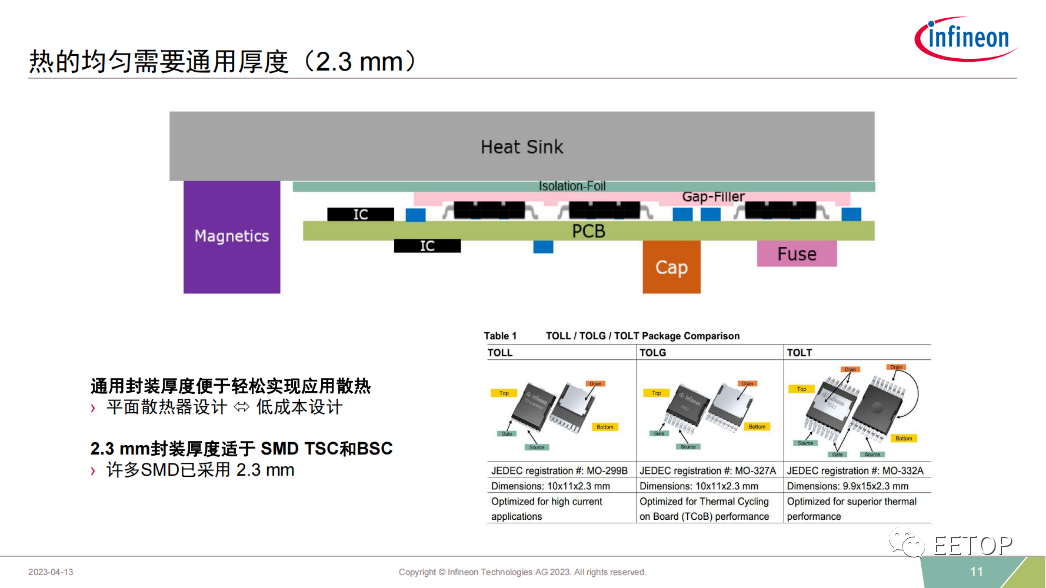

此外,插件封装基本上是靠锁螺丝或铜夹子等导热方式,对芯片厚度的一致性要求没有那么高。但是贴片顶部散热封装技术,由于需要把所有的器件都贴在同一个平面的PCB板上,因此为了让散热片能够把热量均匀地散发出去,同样的器件高度就变成一个必要的因素,这同时也可以有效降低成本。程文涛分享说:“英飞凌定义的封装厚度为2.3毫米。这样的厚度能够让足够多的器件并存在同一块PCB板上。英飞凌也希望通过这次跟JEDEC标准组织的互动,能够使2.3毫米的厚度成为一个业界通行的做法”。

要实现这种采用一个顶部平面的均匀散热,最有效的方式就是用一层能够适应公差的导热胶+隔离片,让所有并排摆放的顶部散热芯片的热量能够均匀地传导到一个平面的散热片上,这是目前业界共同接受的方法。而如果只需要对单独一个顶部散热芯片进行散热,则可以采用锁螺丝、铜夹子甚至焊接等多种选择。程文涛分析表示:“但是从加工的速度、以及制造的成本考虑,导热胶的方法是最行之有效的。而综合对比不同导热胶的导热能力来看,Gap Filler导热胶又是最有效的方式。”

因为插件封装的固有局限,如人工成本,锁螺丝等工艺复杂很难实现自动化,无法实现整个功率最大化,以及空间占用面积大等原因,目前在数据中心、通信,乃至在某些对储能要求更加便携、更加高功率密度的情形下,顶部散热这种贴片形式的占比越来越高,而与之相应的插件封装的占比是越来越少。

英飞凌的顶部散热封装技术

英飞凌的QDPAK和DDPAK顶部散热(TSC)封装技术,其前身就是我们所熟知的DPAK,即TO252封装。其中QDPAK相当于4个DPAK并排;DDPAK则是相当于两个 DPAK并排在一起。那么,这两种封装技术解决的是什么问题呢?

程文涛介绍:“QDPAK和DDPAK这两大顶部散热封装技术能够带来最大的益处在于:高度优化了生产工艺,让整个装配过程步骤变少,自动化制造流程更简洁,最终在下游厂商端实现包括PCB数量、层级和板间连接器用量减少,带来装配及整体系统成本大幅降低。在效能表现上,电源领域最常用的封装是TO247和TO220,而QDPAK和DDPAK,在温度稳定之后,它们的散热能力跟TO220和TO247是对等的。”

其实利用芯片顶部散热的方式,在早期的手机充电器中已经有尝试,当时的做法有的靠灌胶,有的靠通过塑料封装将热量传导到机壳上。可以说顶部散热方式覆盖的功率段范围相当广泛。而英飞凌提供的这类顶部带铜箔的顶部散热封装在功率约为200-300W的应用场景中,就开始凸显其价值了,采用该封装方式,可以实现取消独立散热片,或替代插件器件;而一般功率在1000W时,顶部带裸铜的顶部散热封装就是一个必选项。OBC是顶部散热封装技术很有代表性的应用,如说充电桩、储能设备、数据中心、通信设备等。程文涛表示:“其实但凡是需要体积小、重量轻、功率密度高、效率高的产品,顶部散热封装技术都非常受欢迎。”

就英飞凌顶部散热封装技术的成功应用场景,EETOP也特别向程文涛进行了深度对话。据介绍,目前有两类典型的应用场景是很成功的,而且一些头部客户已经在积极采用。

第一类,是在5G或通信领域。目前的基站所做的设计都是无风扇设计,这跟手机充电器的环境本质上是类似的,但它是靠密闭的金属外壳给基站散热。如果不是顶部带裸铜的方式,就没有办法有效地让它均匀地把热量传导到外壳上,这时候顶部散热几乎是必备的。

第二类是对功率要求越来越高,而且持续增高的应用场景。数据中心就是这一类的典型应用场景。程文涛分享到:“从最近火爆的ChatGPT可以看到人类对数据无止境的需求增长是近似指数级的,在这种情况下对电源转换的效率,以及对同样机房尺寸中能够安装的设备数量提出了更高要求。所以该应用场景中的头部企业也在积极地采用顶部散热封装技术。”

其实除了以上两种,还有一种应用场景是新能源汽车,目前为了满足电动汽车的设计要求,业界在不断增加功率半导体能效的同时,还致力于减少它所占用的PCB面积,这时候对功率密度的要求也很高。顶部散热能够帮助工程师在设计新能源汽车时,把更多空间留给电池动力部分。

结束语