如何应对芯片设计的能源危机?

2022-11-18 12:51:45 EETOP当下,每每谈及芯片设计所面临的挑战时,总绕不开摩尔定律及后摩尔时代、EDA工具、越来越复杂的电路设计,及芯片架构等话题。而与此同时,所有这些挑战,又同时和节能减碳这个能耗问题密不可分。

芯片从生产到使用过程中都需要大量的能源供给。据相关数据显示,2019年台积电用掉了143.3亿度电,这些用电量相当于深圳约1300万的人口一年的用电量。万物互联网的数字时代,每一秒,世界上都有数以千亿计的芯片在高速运转,进一步降低芯片的能耗问题已经迫在眉睫。

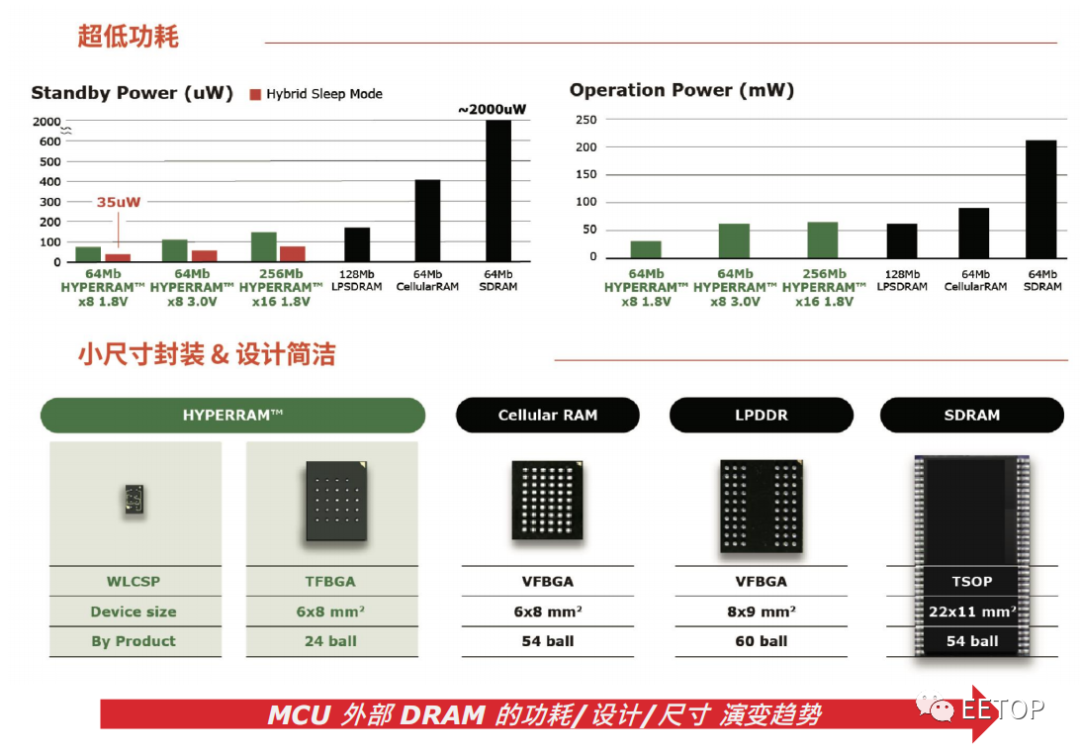

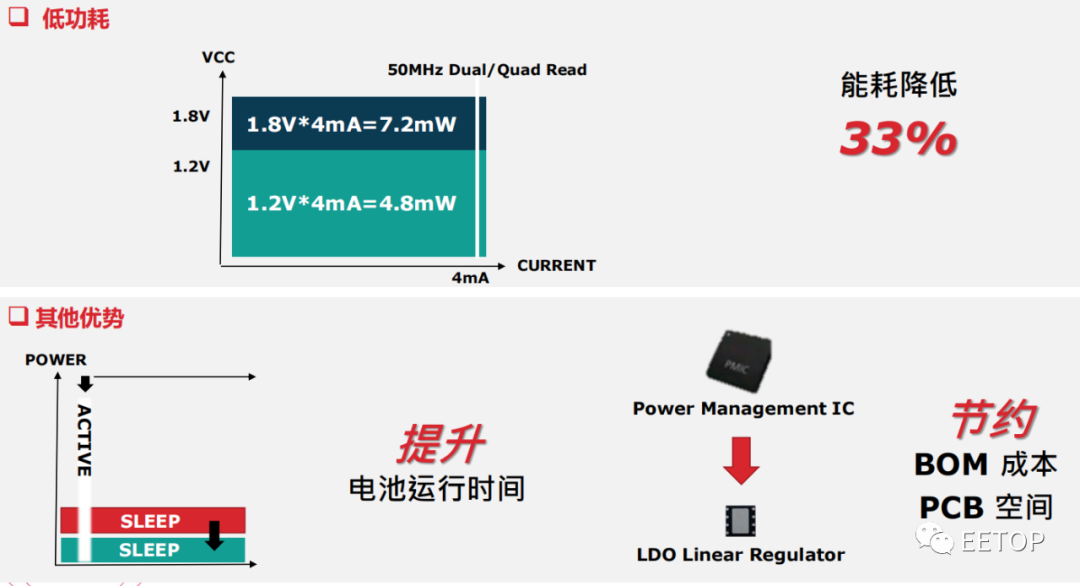

从市场需求来看芯片节能降碳设计方向 芯片是现代工业产品的核心和灵魂,小到耳机手机,大到飞机火箭等,都离不开芯片。其中最常见的就是消费类芯片和汽车类芯片,此外还有应用于数据中心、工业、军工和国防等领域的芯片。 目前在国内,尤其是华南地区,消费类电子,包括物联网芯片、穿戴式芯片的发展非常快。这类终端的下一代产品趋势,首先是低功耗,因为它们的电池设备大多都是要保证较长的续航时间。其次就是降低成本。消费类电子市场竞争非常激烈,几乎所有的公司都在持续不断地去做成本降低。 而在智能监控这种需要进行边缘计算的应用领域,需要提高算力去做AI计算,实现人、物品的识别功能,芯片也演变的越发复杂。汽车ADAS芯片同样如此,很多应用的的算力高达数百T,比如雷达识别或者是特斯拉的视觉识别,对芯片性能的要求都是越来越高的。那么随之制程也一定是越来越先进的,可能会赶超手机、电脑、服务器等应用。 华邦电子大陆区产品营销处处长朱迪在接受EETOP采访时表示:“降低成本,不一定要采取牺牲产品性能的方式,制程降低同样可以有效降低成本,比如说从40nm,降到28nm、22nm,甚至到1X nm。其实汽车,尤其是现在的EV造车新势力,对于ADAS或者智能座舱的要求都非常高,芯片性能也越来越强。因此,制程一定同步发展,甚至可能会选择最先进的制程去做。” 除了制程之外,车机系统同样需要考虑功耗问题。在过去,大家都没有想到在汽车里面会需要搭载几百瓦的芯片,如今这些高性能芯片对整个系统的散热、整体功耗,以及外围器件和存储芯片的影响,都需要重新考虑。 “芯片的集成化将是主流的发展趋势,这也是内存厂商和主芯片厂商合作逐渐增多的领域。”多芯片合封技术同样是减少封装面积、减少能源消耗、降低客户成本、提升产品性价比方式。朱迪分享说,多芯片封装一方面可以通过降低封装材料使用,从而实现节能减碳;另一方面也契合现在整个电子产品,尤其是消费类产品的小型化要求。多芯片合封到一起之后,穿戴类或者是物联网模块类的产品尺寸都可以很小。单芯片,把里面的存储、PA、蓝牙等芯片都合封在一起,可以有效降低整体的成本,并且尺寸也更加轻薄短小。 据介绍,华邦目前就在和主芯片厂商合作进行SiP(多芯片合封技术)的开发,提供KGD产品跟客户的主芯片一起封装,在华邦进行测试,免去单独的封测环节。朱迪指出:“目前,节能减碳是全世界各国的共同趋势。华邦主要从两个方面来实现节能减碳的目标:首先是在产品设计时就实现低功耗,减少终端产品的能源消耗;其次,在产品制造过程中,通过先进工艺减少碳排放,同时工厂做好节能减排和水资源回收等。” 从具体产品设计看华邦的降耗思路 GP-Boost DRAM 目前,华邦专注于GP-Boost DRAM产品的研发及推广,GP-Boost DRAM意为Green Power Boost-DRAM,也就是低功耗的DRAM。相比过去几年在业内用得较多的标准型DRAM产品,例如SDRAM、DDR1、DDR2等,华邦的Green Power产品运行功耗会比常规产品低10%左右,待机功耗更是显著降低,可以比常规的SDRAM产品低60%到70%。同时性能也同样出众,GP-Boost DRAM的带宽较传统产品也有增加,如此一来就可以满足更多像边缘计算这种对算力有要求的应用场景。 除了产品本身的低功耗特性之外,产品封装上所用的化学原材料用量也与能源消耗息息相关。朱迪说:“华邦的每一颗芯片的外部都有厚厚的一层塑胶保护层,如果我们把封装做小就会减少化学物品的消耗。”据介绍,华邦最新推出的100BGA LPDDR4/4X就是一个在封装层面降低消耗的经典产品。相对于传统的200BGA,100BGA的封装,其体积缩小了一半左右,节约了整体材料成本,也减少在PCB的占用空间。 HYPERRAM HYPERRAM产品具备超低功耗特性,运行功耗远低于同容量的CellularRAM和SDRAM,同时通过特有的混合睡眠模式(Hybrid Sleep Mode),HYPERRAM功耗可进一步降低。此外,HYPERRAM大多采用24BGA、 WLCSP这类没有外部塑料的封装,比传统的LPDDR产品封装还要都小很多,可以节约PCB面积、降低成本,同时降低消耗。 除了24BGA封装以外,WLCSP跟KGD封装非常小,可以算是“免封装”产品,相应的功耗也比较低。低功耗带来的另一个好处就是可使客户的产品功耗降低、提升产品续航能力,从而提升客户产品的竞争力。对于需要电池供电的产品来说,还能减少电池的消耗,有助于减小电池生产和回收的环境污染等。 1.2V NOR Flash 低电压也是华邦所努力的方向之一。以NOR Flash 而言,目前的主流电压是3.3V,而可穿戴设备以及其他低功耗的应用,主流电压会达到到1.8V。华邦是全球第一家推出1.2V NOR Flash的厂家,并于2020年实现量产,目前已经有海外的大客户在批量生产采用1.2V NOR Flash的产品。 1.2V NOR Flash有以下好处: 可以同步配合主芯片厂商的制程的演进。因为制程越往下微缩,产品电压会持续下降,需要的I/O电压也持续下降,采用1.2V产品就可以很好地匹配,无需使用电平转换器即可直接和SoC连接,从而降低BOM成本和PCB占用空间。 可以有效降低功耗。此外从 1.8V 电压降至 1.2V,产品本身在运行上会降低50%的功耗,待机功耗也会减少33%,电池寿命、续航能力有大幅的增加,对于整机产品的功耗会有非常显著的改善。 相比传统 1.8V,1.2V 接口具有显著优势 朱迪总结说:“华邦当前的NOR Flash产品容量涵盖2Mb~2 GB、电压范围是1.2V~3V,且都通过AECQ100认证。虽然大容量NOR Flash的成本相对较高,但由于其高可靠性和高稳定性的特点,非常适合汽车的应用。同时华邦的产品目前也得到了国内一线汽车厂商的认证,并且已经有相关项目正在进行。” 从制作工艺角度实现节能减碳 在产品之外,华邦在制作工艺上也有积极探索。比如低温焊接 (Low Temperature Soldering,LTS) 制程,朱迪介绍说:“在存储行业,华邦很早就开始进行LTS制程的研发,推出配合低温焊接制程 (~190C)的闪存产品。” 其实,低温焊接最早是由英特尔于2017年开始提出的。过去,出于环保的考虑,将原有的铅焊转变成无铅焊接,但付出的代价则是焊接温度从常规的210℃、220℃上升到260℃,近40℃的温度升高对能源消耗是巨大的。 所以2017年英特尔主导研发了低温焊接的技术,最先在电脑和平板产品开始使用。 低温焊接技术的核心是焊接材料、芯片本身的需求以及低温焊接锡膏,好处就是温度可以从260℃降到190℃,能源消耗、碳排放都有显著减少。根据计算结果,将 SMT 温度从无铅制程的 220~260C 降到低温焊接制程的190℃,每 条 SMT 生产线的二氧化碳排放量一年可以减少 57 公吨,对于碳排放减量帮助非常明显。 除了节能减碳以外,对于有插件式组件的 PCB,因为插件式组件可以承受低温焊接制程的温度,SMT 就可以一次将所有组件组装到 PCB上,大幅简化及缩短 SMT 流程。而且随着焊接温度下降,芯片及 PCB 还可以选较低成本的低温材料,对于 SMT 生产成本帮助很大,根据统计 SMT 整体每年约可减少 40% 成本开销。 如何实现自身发展和环境保护之间的平衡,对于所有行业都是非常关键的。不过,要实现ESG和减碳目标带来的成本上升一定会降低产品的价格竞争力。现在整个行业,尤其是消费类电子行业的竞争非常激烈,并不是每个公司都愿意去牺牲价格优势,投入资金去做环保,所以这是一个相当大的挑战。朱迪表示:“华邦一直在研究更先进的技术,在不增加成本的前提下实现节能减碳。”