为什么IBIS建模对设计成功至关重要?

2022-10-31 12:13:32 EETOP除了节省成本外,使用 IBIS 模型的设计人员还可以在进行电路板原型设计或制造之前预见并解决信号完整性问题,从而缩短电路板开发周期,从而加快上市时间。

关于IBIS,本文为您介绍以下几部分:

IBIS 模型验证过程的两个部分。

IBIS 代表输入/输出缓冲区信息规范。它代表了 IC 供应商向其客户提供用于高速设计仿真的设备数字引脚的特性或行为。这些模型使用IBIS 开放论坛指定的参数来模拟设备的 I/O 行为,这是一个管理和更新 IBIS 模型规范和标准的行业组织。

IBIS 模型通过表格电压-电流和电压-时间信息使用 ASCII 文本文件格式。它们不包含专有数据,因为 IC 原理图设计信息(例如晶体管尺寸、缓冲器原理图设计中使用的器件模型参数和电路)并未在模型中显示。此外,大多数 EDA 供应商都支持 IBIS 模型,并且可以在大多数行业范围的平台上运行。

为什么使用 IBIS 模型?

想象一下,一个 IC 经过测试通过之后,会使用该 IC 设计PCB,随后立即批准用于制造。PCB制造完成后,如果电路板性能出现故障,而故障是由一些信号完整性问题引起的,这些问题导致串扰、信号过冲/下冲或阻抗不匹配引起的反射。这些板子就必须重新设计和重新制造。

这样时间浪费了,成本也上升了——这一切都是因为一个非常重要的阶段没有进行:预先模拟(presimulation)。此阶段是系统设计人员在构建电路板之前使用仿真模型来验证其设计的信号完整性的阶段。

Spice 和 IBIS 等仿真模型现在正被广泛用于仿真,以帮助系统设计人员在预仿真阶段预见信号完整性问题,以便在制造之前解决这些问题。这个阶段有助于减少电路板在测试期间失败的机会。

历史

1990 年代,随着个人电脑的日益普及,英特尔开始为其工作频率高达 33 MHz 左右的低功耗 ASIC 开发新的 I/O 总线。需要确保信号完整性不受影响,这引发了 IBIS 的创建。

由 Donald Telian 领导的一个团队提出了为 I/O 缓冲区创建信息表并将此信息用于测试英特尔电路板的想法。很快,它还与客户分享了这些表格,用于他们的电路板设计,而没有提供任何专有信息。为了能够将纸质电子表格中的信息可靠地传输到客户的模拟器,英特尔决定与 EDA 供应商和其他计算机制造商合作。

IBIS 开放论坛旨在帮助标准化基于文本的机器可读格式的缓冲区信息。IBIS 最初称为 Intel 缓冲区信息表,后来改为 I/O 缓冲区信息规范。IBIS 1.0 版于 1993 年发布。

此后,IBIS 开放论坛继续推广 IBIS,提供工具和文档,改进标准以增加专业领域的能力。2019 年,IBIS 7.0 版获得批准。这只是表明 IBIS 不断进步并满足技术的新需求。

IBIS 模型是如何生成的?

IBIS 模型通常对设备的接收器和驱动程序缓冲区行为进行建模,而不会泄露专有过程信息。这是通过提取标准 IBIS 缓冲区元素的行为并通过 VI 和 Vt 数据以表格形式表示的来完成的。

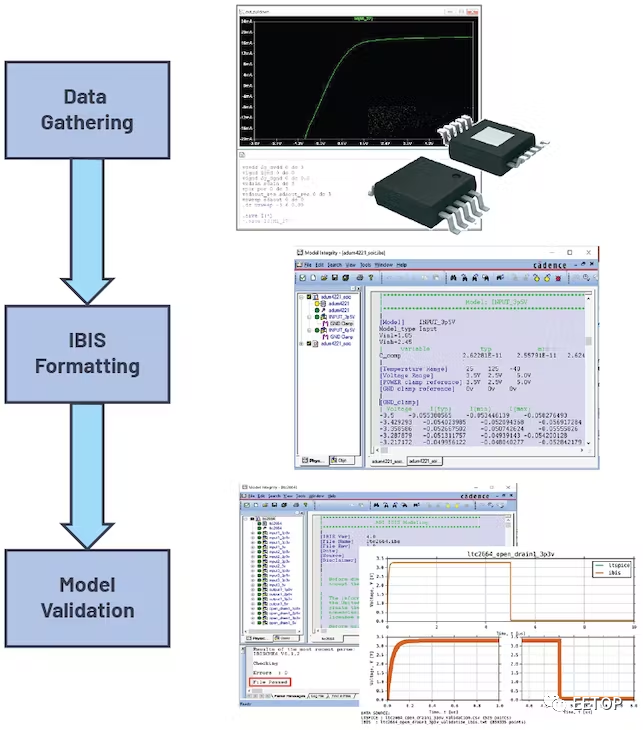

在生成 IBIS 模型时,数据收集通常是开发过程的第一步。图 1显示了生成 IBIS 模型的三个主要阶段。

图1 IBIS 模型生成过程。

数据收集

为 IBIS 模型收集数据有两种方法:

仿真方法:此方法需要访问部件的设计原理图、数据表和集总 RLC 封装寄生参数。

基准测量方法:此方法需要实际单元和/或评估板、数据表和集总 RLC 封装寄生参数。

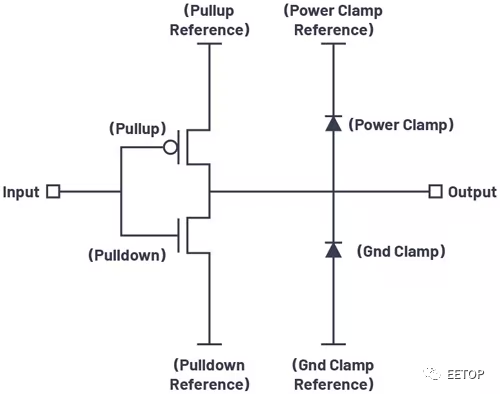

图 2显示了 IBIS 模型中描述的四个主要元素/组件的图表。

图2. IBIS 模型关键字

连接到引脚的两个二极管负责在输入超出工作范围或缓冲器限制的情况下保护缓冲器或 –V DD,具体取决于它的设计运行方式。这些二极管用作 ESD 钳位保护并根据需要打开,而上拉和下拉组件负责驱动缓冲器在高电平和低电平状态下的行为。因此,当缓冲器处于操作模式时,将获取上拉和下拉数据。

这四个主要元素在模型中以电压与电流 (VI) 数据的形式在关键字 [Power Clamp]、[GND Clamp]、[Pullup] 和 [Pulldown] 下表示。I/O 缓冲器的开关行为也在模型中以电压随时间 (Vt) 数据的形式表示。

电压-电流行为关键字

[Power Clamp] 表示数字 I/O 引脚的电源钳位 ESD 保护二极管在高阻抗状态下相对于电源钳位电压基准的 VI 行为。

[GND Clamp] 代表数字 I/O 引脚的接地钳位 ESD 保护二极管在高阻抗状态下相对于接地钳位电压参考的 VI 行为。

[Pullup] 表示 I/O 缓冲器的上拉组件在驱动为高电平时相对于上拉电压参考的 VI 行为。

[Pulldown] 表示 I/O 缓冲器的下拉组件在驱动为低电平时相对于下拉电压参考的 VI 行为。

这些关键字的数据取自 –V DD至 2 × V DD的推荐电压范围,并取自三个不同的角:典型值、最小值和最大值。典型角代表缓冲器在标称电压、标称工艺和标称温度下运行时的行为。最工艺角(corner )代表缓冲器在最低电压、最弱工艺和 CMOS 最高工作结温/BJT 最低工作结温下工作时的行为。最大工艺角代表缓冲器在最大电压、最强工艺和 CMOS 最低工作结温/BJT 最高工作结温下工作时的行为。

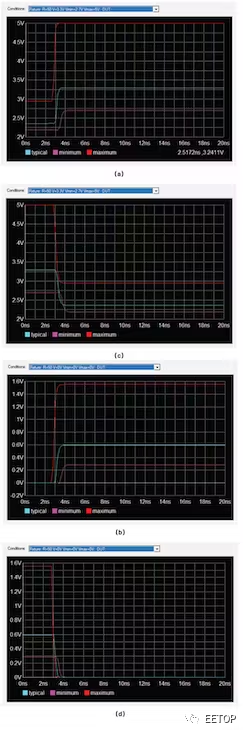

对于在引脚中扫描的每个电压,都会测量其相应的电流,从而获得 IBIS 规范在对缓冲器进行建模时所需的电压-电流行为。这四个VI曲线在三个角的波形示例如图3所示。

5GZQ9ibHb4FeyA/640?wx_fmt=png" data-type="png" data-w="239" data-index="4" data-origin-display="" _width="239px" crossorigin="anonymous" alt="图片" src="https://www.eetop.cn/uploadfile/2022/1031/20221031121716548.jpg" data-fail="0" style="margin: 0px; padding: 0px; outline: 0px; max-width: 100%; box-sizing: border-box !important; overflow-wrap: break-word !important; vertical-align: bottom; height: auto !important; display: initial; visibility: visible !important; width: 239px !important;"/>

图3. (a) 电源钳位数据、(b) 接地钳位数据、(c) 上拉数据和 (d) 下拉数据的VI 曲线示例波形。

切换行为

除了 VI 数据,I/O 缓冲器的开关行为以上升(低到高输出转换)和下降(高到低输出转换)波形的形式也包含在 Vt 数据表中。该数据是使用连接到输出的负载测量的。

使用的负载通常为 50 Ω,以代表典型的传输线特性阻抗。最好使用输出缓冲器实际驱动的负载。该负载与系统中使用的传输线阻抗有关。例如,如果系统将使用 75Ω 走线或传输线,则获得 Vt 数据的推荐负载为 75 Ω。

对于标准推/拉 CMOS,建议将四种类型的 Vt 数据包含在 IBIS 模型中:

负载以地为参考的下降波形

两个上升波形包含在模型关键字 [Rising Waveform] 下。它描述了 I/O 缓冲器在其负载分别连接到 VDD和GND时从低到高的输出转换。另一方面,模型关键字[Falling Waveform]下的两个下降波形描述了I/O缓冲器在其负载也分别连接到V DD和地时从高到低的跳变。

应该注意的是,由于输出端连接了负载,预计输出摆幅不会发生完全转换。与电压-电流行为一样,电压-时间数据取自三个不同的角落。这些转换的示例如图 4所示。

图4. I/O 缓冲器开关行为的采样波形:(a)负载以 VDD 为参考的上升波形,(b) 负载以地为参考的上升波形,(c) 负载以 VDD 为参考的下降波形,以及(d) 负载以地为参考的下降波形。

Vt 表还提取斜率值。斜坡速率是电压从一种状态切换到另一种状态的速率,取自上升或下降过渡沿的 20% 到 80%。斜率在 IBIS 模型中以 dV/dt 比率的形式在 [Ramp] 关键字下列出,通常显示在 Vt 表之后。该值不包括封装寄生效应的影响,因为它仅代表固有输出缓冲器的上升时间和下降时间特性。

此外,IBIS 模型包括一些模拟所依据的数据表规范,例如工作电压和温度范围、输入逻辑电压阈值、时序测试负载值、缓冲电容和引脚配置。它们还包括集总 RLC 封装寄生效应。它们在数据表中找不到,但在模拟高速设计系统的迹线时必不可少,因为这些寄生效应会在模拟中增加负载效应。它们会影响通过传输线的信号的完整性。

IBIS 格式

本节介绍第二阶段,即构建模型——也称为 IBIS 格式化。收集所有必要数据后,现在可以创建模型。IBIS 模型由三个主要部分组成:主头文件、组件描述和缓冲区模型。

主标题包含有关模型的一般信息(图 5)。

RFr5Pm08LOQwwtEgOHqAkWOPuPicUwToFc1DjgA/640?wx_fmt=png" data-type="png" data-w="770" data-index="6" data-origin-display="" _width="677px" crossorigin="anonymous" alt="图片" src="https://www.eetop.cn/uploadfile/2022/1031/20221031121718729.jpg" data-fail="0" style="margin: 0px; padding: 0px; outline: 0px; max-width: 100%; box-sizing: border-box !important; overflow-wrap: break-word !important; vertical-align: bottom; height: auto !important; display: initial; visibility: visible !important; width: 677px !important;"/>

图5. 使用 Cadence 模型完整性的 IBIS 模型中的示例主头文件。

它指定了以下内容:

IBIS版本

型号关键字:[IBIS Ver]

这是模型的基础。它告诉模拟器的解析器检查器在文件中期望什么类型的数据;因此,它在确定模型是否通过解析器检查器方面起着重要作用。

文件名

型号关键字:[文件名]

这应该使用正确的文件扩展名 .ibs 以小写格式显示文件的实际名称。

修订号

型号关键字:[文件版本]

这有助于跟踪文件的修订级别。

日期

型号关键字:[日期]

这显示了模型的创建时间。

笔记

型号关键字:[备注]

这包括供客户参考模型,也就是说,如果数据是从模拟或台架测量中获取的。

资源

型号关键字:[来源]

这会告诉模型起源于何处或指示模型提供者。

免责声明

型号关键字:[免责声明]

版权

型号关键字:[版权]

请注意,主标题下列出的前三项是必需的。其他项目不是必需的,但最好包括在内,因为它们添加了有关文件的其他详细信息。

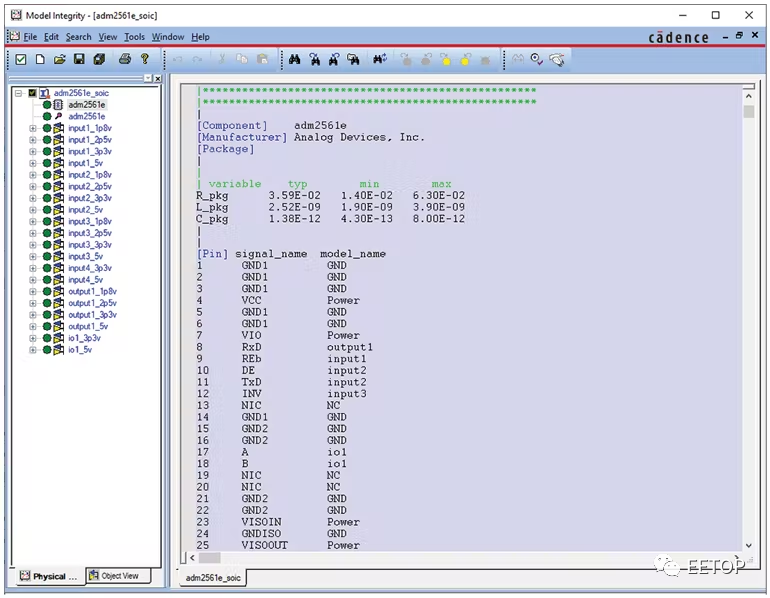

IBIS 模型的第二部分描述了组件(图 6)。

图6. 使用 Cadence 模型完整性的 IBIS 模型中的示例组件描述。

对于这部分,需要以下数据:

组件名称

模型关键字:[组件]

正如名称所述,这是正在建模的设备的名称。

引脚列表

型号关键字:[Pin]

这部分出现在模型中至少有三列:管脚号、管脚名称和模型名称。此列表基于数据表。它应该反映引脚编号和引脚名称的正确匹配,以避免混淆。还需要注意的是,在 IBIS 模型中,每个引脚都有一个专用的模型名称。此型号名称不一定与数据表中所述的引脚名称相同,因为引脚的型号名称由模型制造商自行决定。此外,一些引脚可能指向一个型号名称。具有相同设计原理图的缓冲器就是这种情况。预计它们将具有相同的行为,因此一组数据足以代表它们。

制造商

型号关键字:[制造商]

它标识正在建模的组件的制造商。

封装寄生

型号关键字:[包]

此项描述了组件封装的电气特性,包括集总电阻、电感和电容值。如果引脚的 RLC 寄生参数也可用,则应在模型中的 [Pin] 关键字下与引脚列表一起列出。这提供了一个更准确的模型,并将覆盖 [Package] 关键字下列出的 RLC 值。

IBIS 模型的第三部分描述了缓冲模型。这就是 I/O 缓冲区的行为,特别是它的 IV 和 Vt 数据。它首先使用 [Model] 关键字识别模型名称。型号名称应与 [Pin] 关键字下第三列中列出的名称相匹配。

对于每个缓冲区模型,必须指定参数 Model_type。缓冲电容也必须出现在参数 C_comp 下,以描述从焊盘回看缓冲时看到的电容。

缓冲模型的类型

可以对不同类型的缓冲区进行建模,并对每种缓冲区应用特殊规则。下面描述了四种最常见的缓冲区类型及其在 IBIS 模型中的要求:

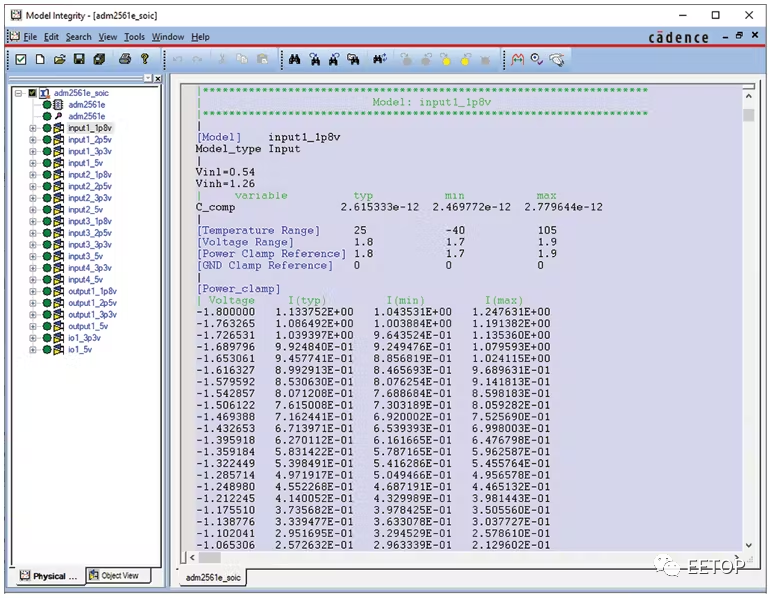

输入缓冲器模型类型:输入

这种模型类型需要输入逻辑阈值的值,在参数 Vinl 和 Vinh 下(图 7)。如果未定义,则模拟器使用的默认值分别为 0.8 V 和 2 V。这些参数有助于模拟器执行时序计算并检测信号完整性违规。

图7. 使用 Cadence 模型完整性的输入缓冲区模型的示例表示。

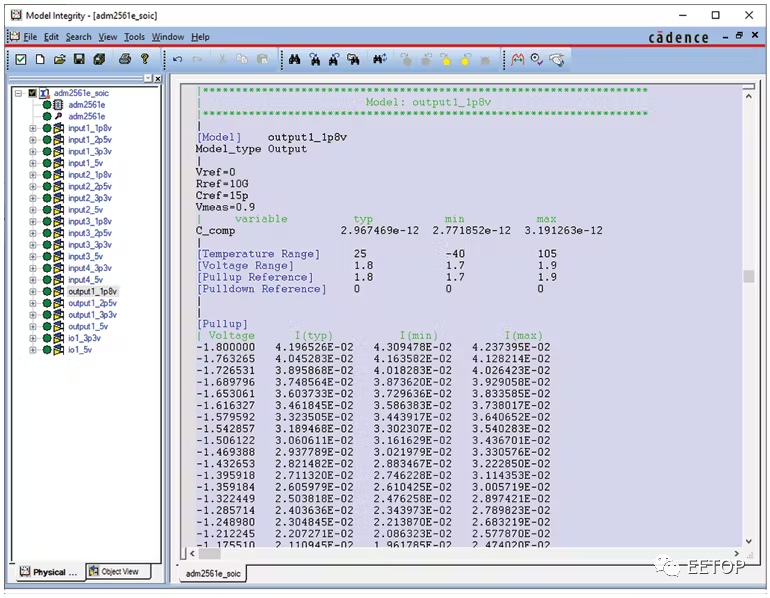

两态输出缓冲器型号类型:输出

此模型类型表示始终启用的输出缓冲器,驱动高或驱动低(图 8)。它包括参数 Vref、Rref、Cref 和 Vmeas 下的时序测试负载值。这些参数不是必需的,但它们在模型中的存在将有助于模拟器执行板级时序计算。

图8. 使用 Cadence 模型完整性的两态输出缓冲区模型的示例表示。

请注意,由于此类缓冲器无法禁用,因此不会列出关键字 [Power Clamp Reference] 和 [GND Clamp Reference],以及 [Power Clamp] 和 [GND Clamp] 的 VI 表格数据。

三态输出缓冲器型号类型:三态

这种模型类型代表了一个输出缓冲器,它不仅在其驱动高电平和驱动低电平状态下表示,而且在其高阻抗状态下表示,因为这种类型的缓冲器可以被禁用(图 9)。与输出模型类型一样,它还包括参数 Vref、Rref、Cref 和 Vmeas 下的时序测试负载值。在模型中添加这些将有助于模拟器执行板级时序计算。

图9. 使用 Cadence 模型完整性的三态输出缓冲区模型的示例表示。

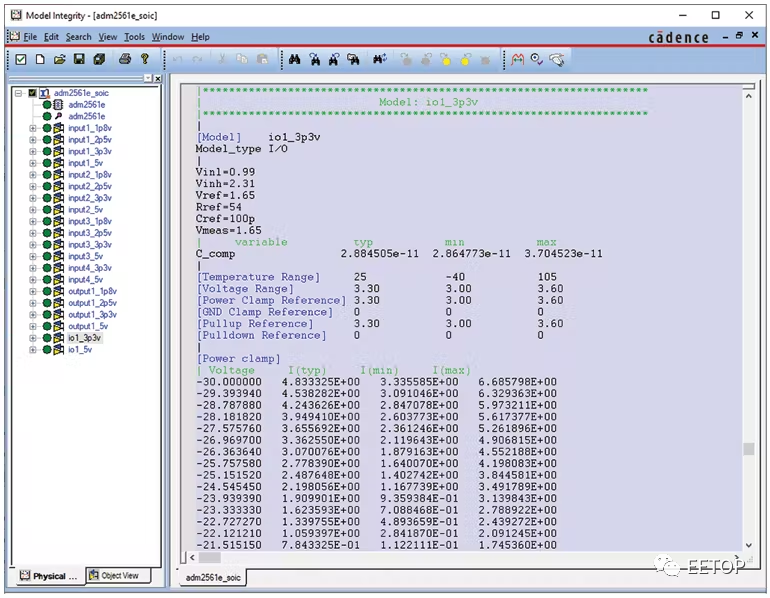

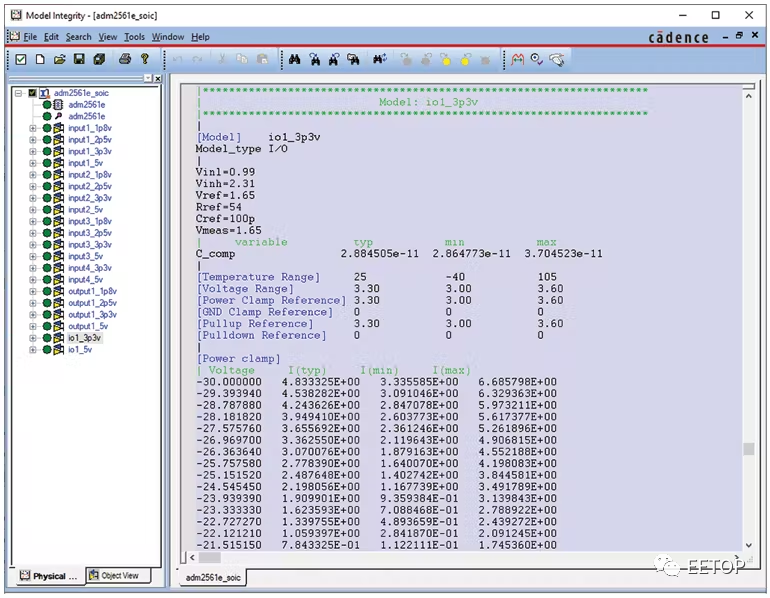

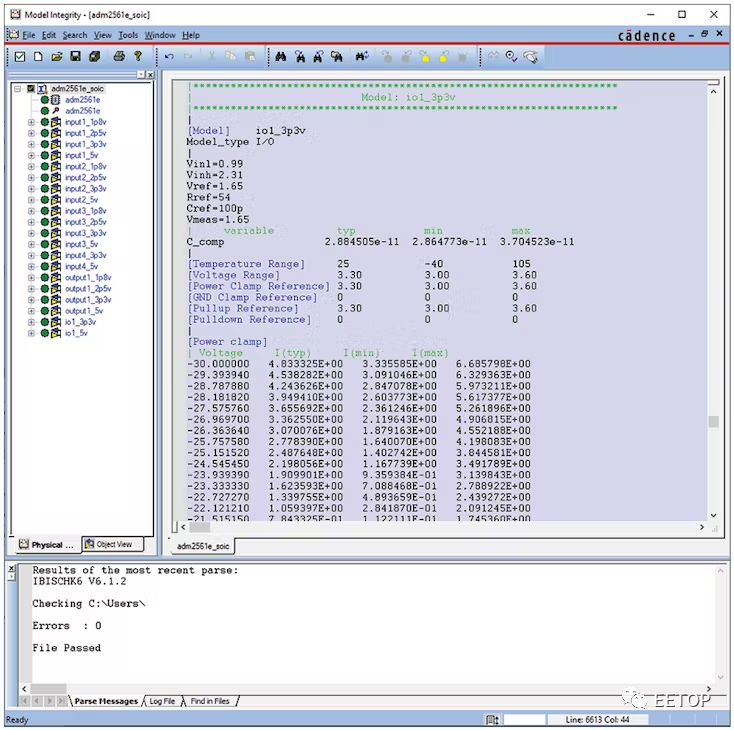

I/O 缓冲器型号类型:I/O

这种模型类型是输入和输出缓冲区的组合(图 10)。因此,该模型中要包含的参数是 Vinl、Vinh、Vref、Rref、Cref 和 Vmeas。

图10. 使用 Cadence 模型完整性的 I/O 缓冲区模型的示例表示。

模型制作者在生成 IBIS 模型时必须注意这些指南。更多内容可在IBIS 开放论坛网站的IBIS Cookbook中找到。必须遵循正确的建模指南;否则,模型将无法通过验证阶段。

模型验证

验证 IBIS 模型分为两部分:解析器测试和相关过程。

解析器测试

在构建模型时,最好使用已经具有 Golden Parser 的软件。该程序根据模型版本的规范执行语法检查并验证创建的 IBIS 模型的数据匹配。一些具有此功能的软件是 Cadence Model Integrity 和 Hyperlynx Visual IBIS Editor。

如果模型通过了解析器测试,这意味着生成的模型遵循标准格式和规范,VI数据与Vt数据匹配。如果没有,最好找出导致错误的原因。最简单的可能原因是模型中使用的格式或关键字不符合 IBIS 规范——这很容易纠正。

另一种类型的错误是 VI 和 Vt 数据匹配。发生这种情况时,错误可能在于上拉或下拉 VI 数据,或 Vt 数据。这是 VI 数据表示的行为与 Vt 数据表示的行为不匹配的情况。

为了解决这个问题,可能需要重新仿真。不过,在此之前,请先查看您放置在模型中的电压和负载值,并检查它们是否正确。当错误的原因与错误定义的电压值一样简单时,您可以避免花费更多时间重新仿真。

图 11 和 12分别显示了一个失败并通过了解析器测试的示例 IBIS 模型。

在图 11中,观察软件如何标记导致模型在解析器测试期间失败的错误。这使得模型制作者在进行下一个验证步骤之前可以轻松地更正模型。在此示例中,错误是由用于缓冲区的模型类型引起的。IBIS 规范要求以大写格式输入 I/O 模型类型,而在此图中,使用小写格式。

GPUWdAaFM8n43zVEmGxdpwpkgNIyCRT5NiaFcIPg/640?wx_fmt=png" data-type="png" data-w="733" data-index="12" data-origin-display="" _width="677px" crossorigin="anonymous" alt="图片" src="https://www.eetop.cn/uploadfile/2022/1031/20221031121721376.jpg" data-fail="0" style="margin: 0px; padding: 0px; outline: 0px; max-width: 100%; box-sizing: border-box !important; overflow-wrap: break-word !important; vertical-align: bottom; height: auto !important; display: initial; visibility: visible !important; width: 677px !important;"/>

图11. 使用 Cadence 模型完整性对失败的 IBIS 模型进行解析器测试。

图 12显示了通过解析器测试的模型。注意 Model_type 关键字中的 I/O 已更改为大写格式。这解决了错误。

图12. 使用 Cadence 模型完整性对通过的 IBIS 模型进行解析器测试。

模型只有通过此阶段才能继续进行关联过程。

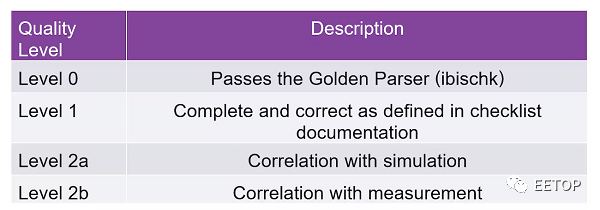

相关过程

那么,有人可能会问,我们如何确保生成的模型与实际零件一样准确?答案是相关过程。IBIS 模型有不同的质量等级/相关性(见表格)。

本文描述了一个质量级别 2a 的 IBIS 模型。通过解析器测试后,将模拟模型,包括添加外部负载的 RLC 封装寄生效应。负载通常是数据表中用于表征 I/O 缓冲器的时序测试负载值。同样,零件的设计原理图将使用相同的设置和负载进行仿真。两个仿真的结果将被叠加,以验证生成的模型是否与基于原理图的结果的行为相匹配。

为什么 IBIS 模型对您的仿真至关重要

大多数 EDA 供应商都广泛支持 IBIS 模型。它们易于使用且尺寸更小,从而提供更快的仿真时间。它们不包含专有工艺和电路信息,这使大多数半导体供应商能够轻松地向其客户提供 IBIS 模型。这些模型展示了所有这些优势,同时准确地建模了设备的 I/O 行为。

IBIS 模型使设计人员能够在进行电路板原型设计或制造之前预见并解决信号完整性问题。这样做使他们处于有利位置,可以缩短电路板开发周期,进而有助于加快产品上市时间。

简而言之,客户使用 IBIS 模型是因为在他们的仿真中使用它们不仅有助于节省成本,还有助于节省设计、调试和从电路板设计中获得收益的时间。

原文

https://www.electronicdesign.com/technologies/test-measurement/article/21253556/analog-devices-ibis-modeling-part-1-why-ibis-modeling-is-critical-to-design-success

关键词: IBIS