亚10纳米节点的时钟老化问题

2022-10-28 11:47:15 EETOPEETOP编译自semiwiki

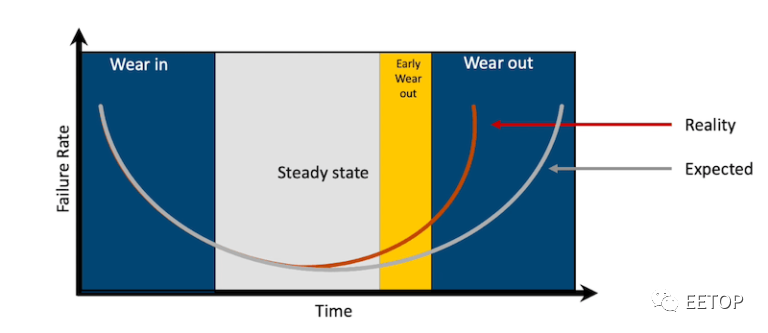

半导体芯片在发货前都经过测试,以排除早期故障,但是还有一些更微妙的可靠性影响,这些影响只会在较长时间内出现,比如时钟老化。甚至还有一个经典图表显示了故障率随时间变化的“浴缸曲线”:

IC故障率图

如果磨损区域的现实和期望不一致,那么召回嵌入系统内的芯片所带来的财务影响可能要花费数百万美元,甚至在安全关键应用中要付出人命。

一个 7nm 的 SoC 可以有 100 亿个晶体管,并且为了满足功率规范,有许多时钟域和多电压电源域;导致老化问题,如抖动、占空比失真、插入延迟、设计余量减少和工艺变化增加。要预测晶体管老化的影响,需要了解电路拓扑、开关活动、电压甚至温度——这是一个复杂的目标。

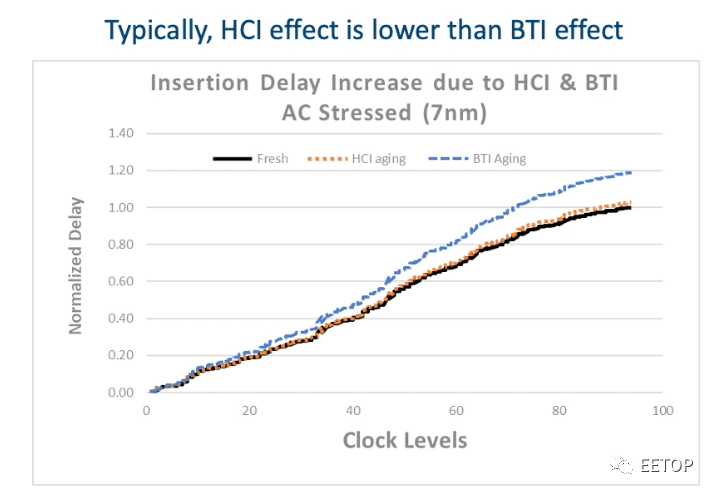

晶体管老化来自几个影响:热载流子注入 ( HCI )、负基极温度不稳定性 ( NBTI )、正基极温度不稳定性 ( PBTI )。较高的温度会加速这些影响。占空比影响 BTI 效果,频率对 HCI 有成比例的影响。使用 HCI 时,电荷会被困在晶体管的氧化层中,从而永久改变器件的 Vt。对于 7nm 节点,BTI 效应高于 HCI 效应,如下图所示插入延迟,其中黑线是新电路,而 HCI 的老化效应是橙色,BTI 效应是蓝色。

BTI 和 HCI 效应

10nm 以上的 IC 设计方法使用静态时序分析 (STA) 和一些时钟的 SPICE 仿真,以及抖动等参数的保护带。老化可以应用于所有设备,以提供有关电气和时间影响的概念。

10nm 以下的设计需要对时钟老化影响进行更全面的分析,比如Infinisim 创建了一个名为ClockEdge的工具,可以有效地分析大型时钟网络。ClockEdge 工具会自动创建一个晶体管级网表进行分析,然后可以在一夜之间进行仿真,向您展示最新的和老化的结果。

从现有文件创建一个新的时钟域网表:Verilog、Lib、叶单元定义、约束、SPEF。以您的功能时钟频率为新鲜状态生成具有完全 SPICE 精度的仿真结果。然后对时钟进行压力分析,作为分析的第二步。第三步是使用老化的时钟域网表,以功能时钟频率运行完整的 SPICE 精确仿真,并评估占空比失真、插入延迟、轨到轨电平,甚至时钟摆率。新鲜和陈年结果之间的差异告诉设计团队他们是否有可靠的设计。

深入研究第一步,新运行分析从锁相环的输出,一直到触发器或输出垫的时钟域。这个时钟域可以非常大,包含数百万个器件,晶体管级分析结果向我们展示了延迟和压摆值。

步骤1:全新运行

通过使用分布式 SPICE 仿真方法,ClockEdge 工具可以在一夜之间对一个具有 450 万个门、5.17 亿个 MOSFET 和 32 亿个器件的块运行时钟分析。你的时钟拓扑结构可以实现为树状、网格和刺状。

步骤2:压力运行

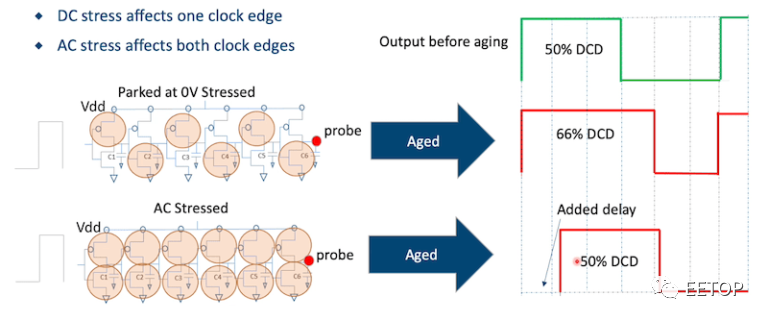

特定的晶体管将被选中进行老化,所有这些都取决于电路拓扑结构和时钟是否被停顿(卡在VDD或VSS),或切换。压力运行也取决于温度、电压和每个使用模型的持续时间。

步骤3:老化模拟

使用老化的器件。对于有停顿时钟值的器件,那么在老化分析过程中,只有时钟的一个边会受到影响,而有时钟切换的器件在老化分析过程中,两个边都会受到影响。所以占空比延迟(DCD)的形状将取决于你的电路拓扑结构。使用 ClockEdge,设计人员可以执行假设压力分析,比较时钟停在 0、停在 1、切换甚至是停放和切换组合的影响。

总结

时钟老化是一个新的可靠性问题,特别是对于低于 10nm 工艺节点的 IC 设计。通过适当的分析,可以减轻老化的影响。文中提及的ClockEdge 工具可专注于为设计人员提供对其时钟网络的准确老化分析,并在一夜之间快速提供结果。你可以看到你的老化时钟域的直流和交流压力条件。

原文

https://semiwiki.com/eda/319691-clock-aging-issues-at-sub-10nm-nodes/