400G 以太网改用 PAM-4 信令取代 NRZ

2019-12-30 10:31:36 SynopsysIEEE 等众多标准机构已经对多级信令进行了广泛讨论,即在更高数据速率下克服信道带宽限制时,将他作为 NRZ 信令的替代编码方案。

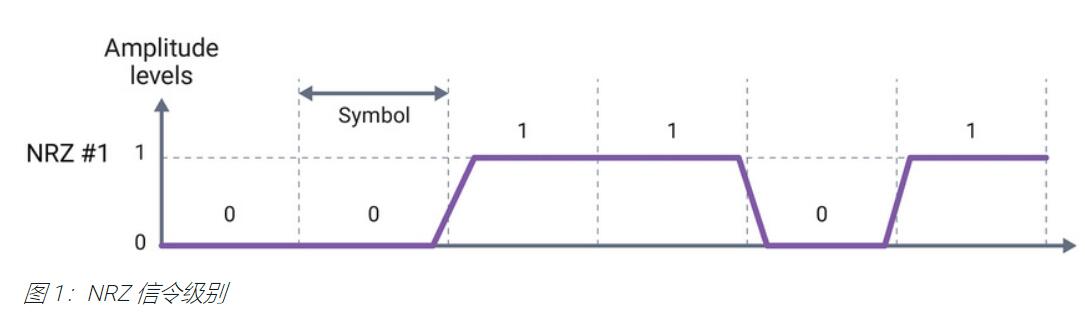

在 NRZ 信令中,一个比特是一个符号,具有 0 或 1 这两个不同的幅度(图 1)。符号以波特表示。NRZ 比特率等于其符号率,1Gbps 等于 1G 波特。

图 1:NRZ 信令级别

图 2:PAM-4 信令级别

图 3:采用格雷码的 PAM-4 信令

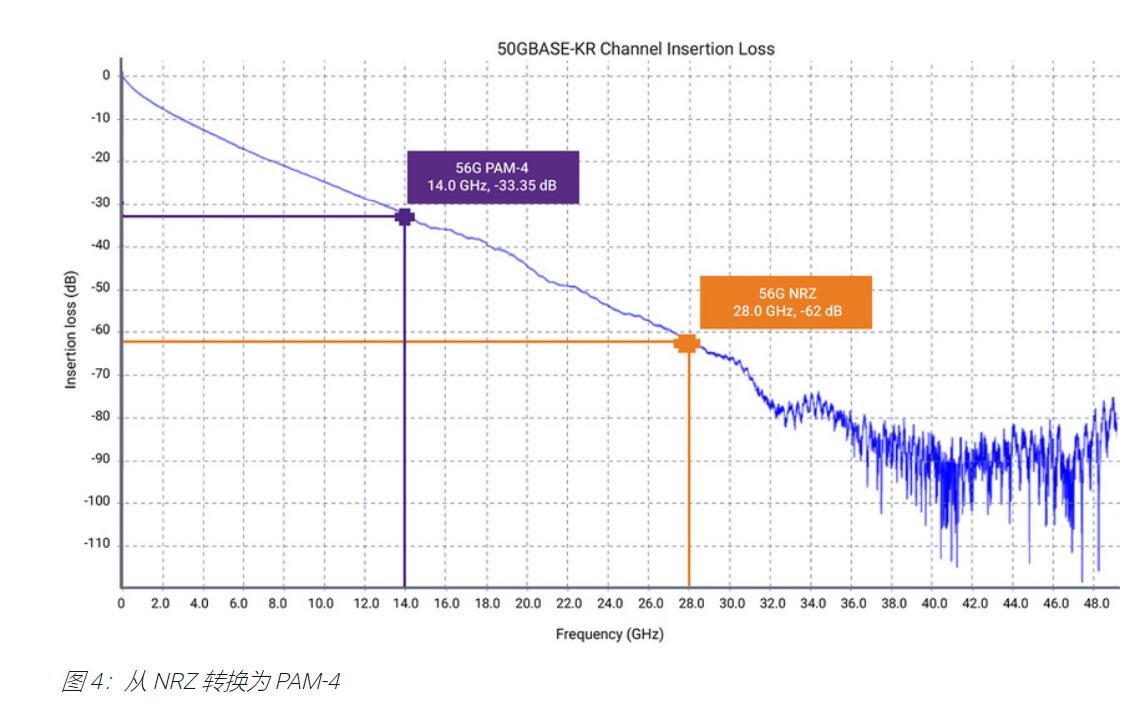

图 4:从 NRZ 转换为 PAM-4

然而,PAM-4 并不普遍保证能使用传统信道设计,因为串扰、回波损耗和非线性等信道损伤对 PAM-4 信号的影响较大,需要加以解决。

与 NRZ 的两个电压级相比,PAM-4 具有四个电压级,导致 12 种不同的信号转换(六次上升和六次下降),产生三个区域眼图开度,如图 5 所示。每个眼高为 NRZ 眼高的 1/3,致使 PAM-4 信噪比 (SNR) 降低 9.5 dB 以上,这会影响高速信令的信号质量并带来额外的约束。垂直眼图开度减小 33% 会降低 PAM-4 中信号的串扰和反射容差,从而导致更高的误码率。

图 5:NRZ 与 PAM4 信号转换及眼图开度的比较

非线性也会改变信号眼高,显著影响误码率性能。误码率主要受确定性抖动和噪声的影响。

信道损伤对 PAM-4 中的三处眼图中每一处都有不同的影响,要求每处眼图都有自己的专用数据、错误和信号交叉检测器组合。PAM-4 中的所有三处眼图都不对称,每一处都需要分别进行均衡。

超大规模数据中心正在成为企业的首选,可以处理和存储大量数据,以执行针对各种数据密集型应用程序的工作负载。为了实现更快的数据连接以在超大规模数据中心中传输大量数据,服务提供商开始利用基于 56G PAM-4 信令的 400G 以太网链路。由于 NRZ 信令不足并且 PAM-4 能够以波特率的一半实现更高的比特率,因此设计人员可以继续以有望达到 400G 的以太网数据速率使用现有信道。然而,PAM-4 信令对诸如串扰和非线性之类的信道损伤更加敏感,这一问题需要在 PHY 设计实现中予以解决。

Synopsys 提供经过硅验证的 PAM-4DesignWare®56G PHY IP,设计人员可将其集成到其超大规模 SoC 中,以支持高达 400G 的以太网链路。PHY 基于 Synopsys 经过硅验证的数据转换器构建,具有可配置性发送器和基于 DSP 的接收器,使设计人员能够优化信号完整性和性能。在支持 IEEE 和光互连网络论坛 (OIF) 标准规范的同时,PHY 还支持芯片到芯片、芯片到模块(铜缆和光纤)以及铜背板互连,信道损耗低至 35 dB。此外,嵌入式误码率测试仪和内部眼图监控器为通道性能提供了片上可测性和可见性。