IC封装设计者利用新的Cadence Allegro SiP和IC封装软件提高生产率

2009-11-03 14:56:34 本站原创新的软件版本具有协同设计和设计链支持技术,通过改进的小型化设计功能来帮助设计者降低成产成本

【加州圣荷塞,2009年11月03日】全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,利用最新的系统封装(SiP)和IC封装软件,封装设计者将在芯片封装协同设计过程中和整个半导体设计链中担当更重要的角色。Cadence® Allegro® 16.3版提供的新产品的SiP Layout XL,它将协同设计直接融入封装设计环境中。新的协同设计技术支持在封装和芯片设计团队共同对芯片和封装设计进行优化,整个过程中封装设计者无需另外学习新的IC设计工具。通过Allegro Package Designer (APD)提供的新型SiP Finishing技术,设计链协作也将得到进一步增强。

利用这一新技术带来的协同设计方法,封装设计者、封装设计服务公司,装配测试公司(OSAT)可以共同参与到多芯片 SiP的设计链中。Cadence协同设计技术也使设计链合作伙伴彼此之间能够轻松地传输数据。使用了16.3版软件的公司将受益于更短的设计周期、更高的生产率和更低的成本。

“我们非常期望采用16.3版软件,因为我们能够籍此提高生产率,为我们的客户提供更好的IC封装协同设计服务”,ASE公司的R&D产品设计经理CT Chiu表示,“我们相信新的Cadence SiP和IC封装技术将在提高半导体设计链效率方面担当重要的角色。”

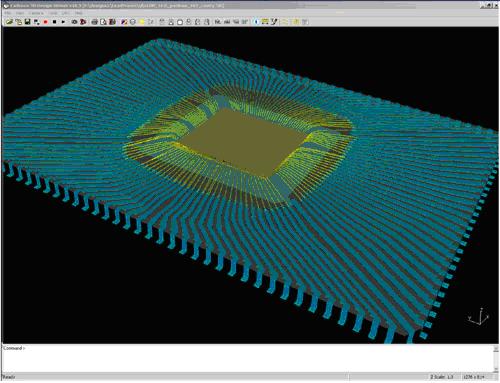

在设计小型化方面,SiP Layout XL为封装设计者提供了成效显著的新功能;利用协同设计技术,他们能够将从封装环境中直接编辑IC abstrcat 如IO Pad Ring、Bump Matrix和RDL虚拟化连接,然后将封装设计的建议通过工程更改单(ECO)返标至IC设计团队;通过Super smooth布线技术, 设计者在确保成品率的同时可实现更高的布线密度,以达到封装设计小型化;Allegro Constraint Manager中带有装配规则检查(DRC)功能,可确保小型化设计能够针对共同约束环境中的装配规则进行检查;新版的SiP Layout XL支持Windows、Unix或Linux等各种计算机平台,还拥有三维物理设计效果图和不同团队分区设计功能。

最新软件版本的其他重要功能包括对Wirebond的改进,增强了Leadframe设计中的Wirebonding工艺。另外,Allegro Package Designer现在提供了SiP完成模式,它可以对封装设计进行读取和对基板编辑的功能,使APD用户可以针对最终的artwork/tapeout进行封装设计准备,实现生产准备设计的就绪。

“我们已经将这些重要的新功能集成在新的软件版本中,它能够帮助封装设计者在协同设计中成为真正的增值合作伙伴”,Cadence产品营销部门总监Keith Felton表示,“采用最新的Cadence SiP和Allegro Package Designer软件,可帮助这些工封装设计工程师在整个半导体设计链中成为重要的一环。”

Allegro SiP and IC Packaging 16.3版将于2009年12月初上市。