D波段:6G的未来之路及电路挑战

2020-05-24 12:13:17 EETOP编译自allaboutcircuits就目前而言,5G已经登上了主舞台。但6G或许并不像我们想象的那么遥远。

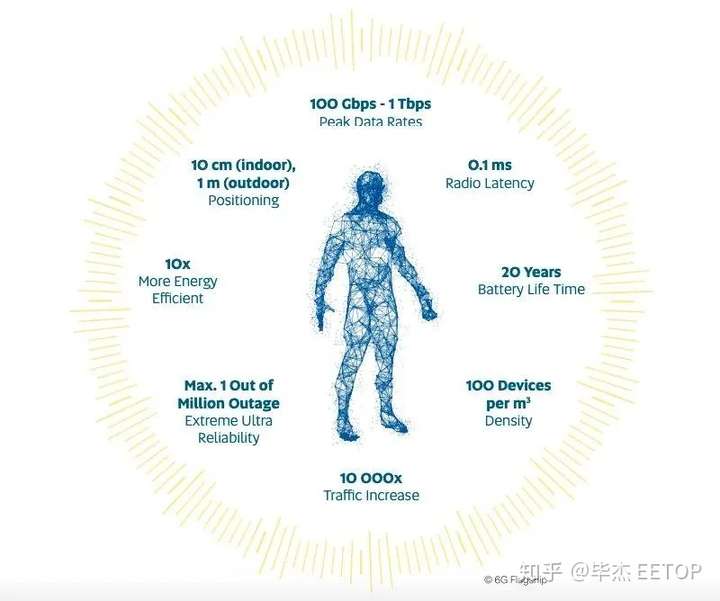

在世界范围内开始广泛使用5G技术的同时,研究人员正在为6G奠定基础。这将以超过10 Gbps的数据速率和1毫秒的延迟超越目前的5G功能。Thales在对5G技术的评论中指出,它还可以连接比4G LTE多100倍的设备,并提供1000倍的带宽以及其他改进。

现在,我们知道6G至少需要满足什么条件,但是我们将如何做到?为了回答这个问题,研究人员正在研究频率范围以及将发送和接收这些信号的电路。

根据电子实验室CEA-Leti撰写的一篇论文,通过毫米波(mmWaves)(特别是D波段)通信是6G技术的传播的渠道。D波段只是无线通信的一组指定频率范围。在D波段的演示中,诺基亚概述了这些范围:

这些加起来总共高达31.7 GHz的频率可用于6G,这是非常大的带宽!高通公司表示,这与5G大约13 GHz的带宽相比。此升级可以在单位面积上启用更多连接。不过当这些频率开放时,物理障碍将对这些波产生影响。CEA-Leti建议需要高增益天线和电路。

格勒诺布尔大学(University of Grenoble)发明了一种具有非常高增益的天线设计。该天线模块利用一些D波段,工作在114 GHz和138 GHz之间,最大增益为25 dB,最小增益为22 dB。

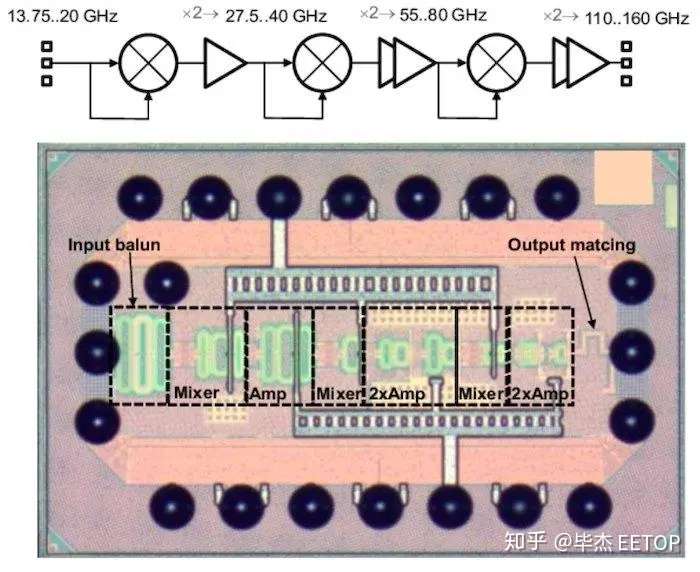

该电路旨在通过集成的倍频器实现超快的短距离通信。该乘法器由一系列自混频器电路和放大级组成。自混频器使输出频率相对于输入信号加倍。下面是天线驱动器电路和单个混频器级电路的框图。

关于整个天线驱动器电路,标记为“输入平衡-不平衡转换器”的部分是差分信号进入第一混频器级的地方。混频器和放大器级的电路活动部分(晶体管电路–每个模块的橙色部分)的大小相同,但是输出电感器和变压器(布局图中的绿色)在每个阶段都得到了优化他们正在处理的频率。

因此,我们看到电感器和变压器的尺寸随着频率的增加而减小。相应的级是级联放大器,每级增益加倍。所有这些放大器都是相同的公共源伪差分级。

NMOS晶体管优化频率响应

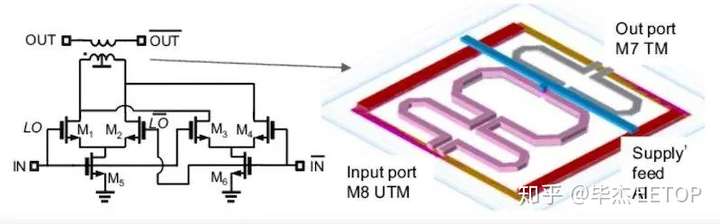

现在,我们可以看到混频器原理图只实现了NMOS晶体管。这是因为CEA-Leti报告担心CMOS电路对D波段高频的响应能力。该混频器电路实现了两个用于差分输入的晶体管(M5和M6),以下拉方式连接到差分对NMOS晶体管(M1和M2;M3和M4)。

耦合变压器的自混级原理图和布局

M1和M3连接到输出变压器的一侧,而第二个连接到M2和M4。

现在,由于M5和M6由差分信号控制,因此M1和M3在输入波的相反半个周期导通。这意味着在前半个周期中,M1闭合,M3断开,而在后半个周期中,M3闭合,M1断开。

M2和M4也相同。M1 / M3和M2 / M4的输出节点组合为一个差分信号,并且是输入频率的两倍,因为晶体管组合在不同的半周期内导通和截止。然后,混频器通过变压器耦合到下一个放大级。

该电路中的所有NMOS晶体管(混频器和放大器)均为低阈值晶体管,可优化电路的频率响应。

D波段和新颖的电路设计(例如天线电路)可以成为6G技术的良好初始框架。尽管我们对6G信号将在何处传播有所了解,但还有很长的路要走。我们仍然需要使用该频段进行远程通讯,并考虑大规模集成的挑战。

D波段具有远超5G的空间和能力,新的晶体管电路设计将为天线发射和接收带来如此高的增益,这将使我们能够在高频下进行通信。

6G或许没有我们想象的那么遥远!