Hot Chips 2023 :进一步揭露世界最大FPGA技术细节

2023-09-14 11:21:42 EETOP来源:科技新报(台) 作者:痴汉水球

AMD在2022年2月14日,完成收购FPGA第一大厂赛灵思(Xilinx),价值约500亿美元(原先估值350亿美元,被AMD股价上涨推高),创下芯片产业的交易纪录。因为FPGA可编程的特性,使其具灵活性、可客制性、平行处理能力、易于升级等优势。

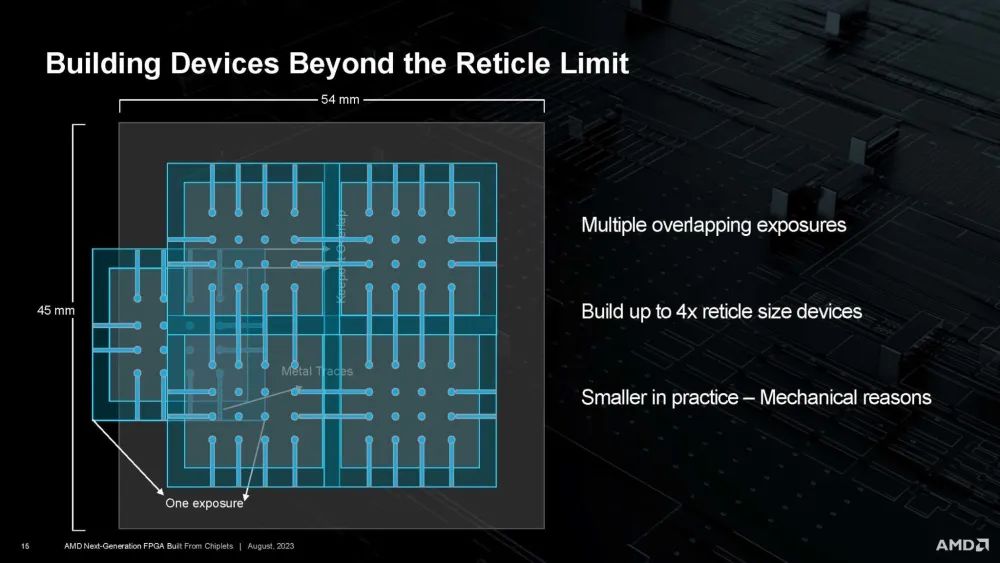

通过FPGA,芯片设计者能在芯片送交制造(Tape Out)前,先为即将完成的ASIC或系统单芯片(SoC)创建数位双胞胎版本,有助于产品验证,并提高开发软件。人工智能蔚为风潮且相关技术快速翻新当下,FPGA更同时是AMD和英特尔(2015年6月以167亿美元收购全球第二大FPGA厂商Altera)AI产品布局的重要一环。 AMD于今年 6月27日发布了世界最大的FPGA芯片Versal Premium VP1902,相较上一代赛灵思Virtex UltraScale+VU19P,增加了AI专用处理器Versal,所有性能规格指标都是两倍起跳,并采用Chiplet设计,尺寸约为77×77毫米,拥有1,850万个逻辑单元,以及控制平面操作的专用Arm 核心与协助调试的板载网络。AMD预定第三季提供样品给客户,2024年初全面供货。 Hot Chips 2023(第 35 届)进一步揭露 Versal Premium VP1902 技术细节,就让我们仔细瞧瞧这颗「专为研发更大芯片诞生」的巨大 FPGA。

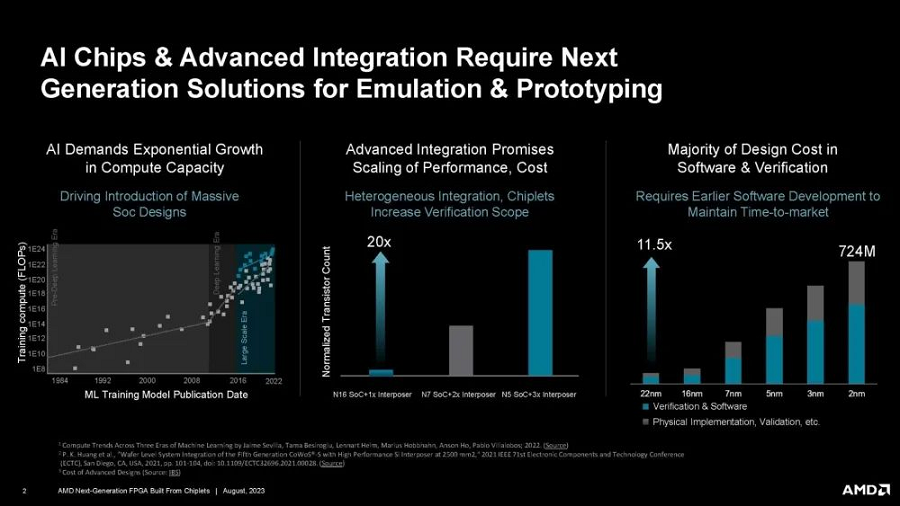

▲ AMD开宗明义:现在就是 AI 时代,无论是 CPU、GPU 还是专用加速芯片,都要有 AI 能力。

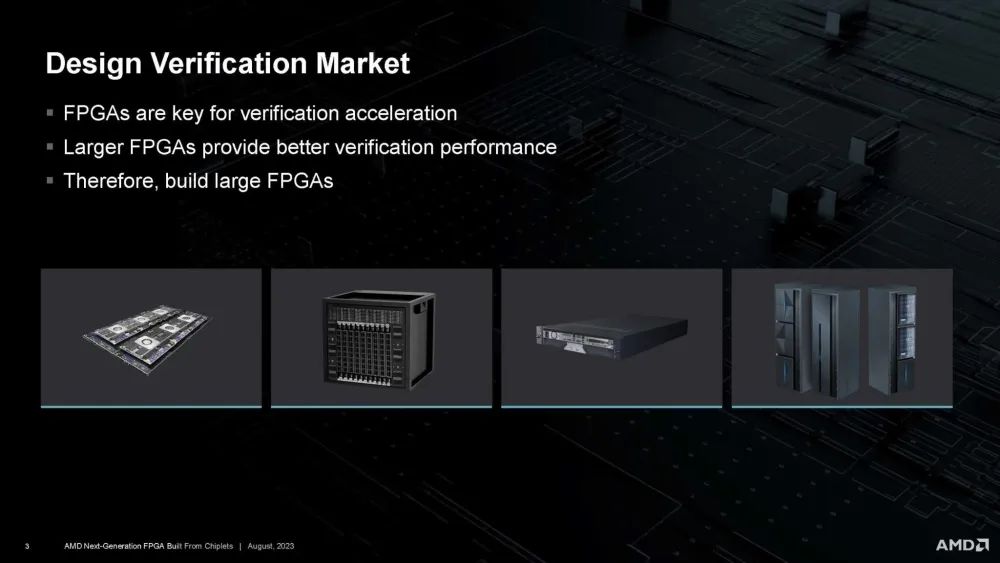

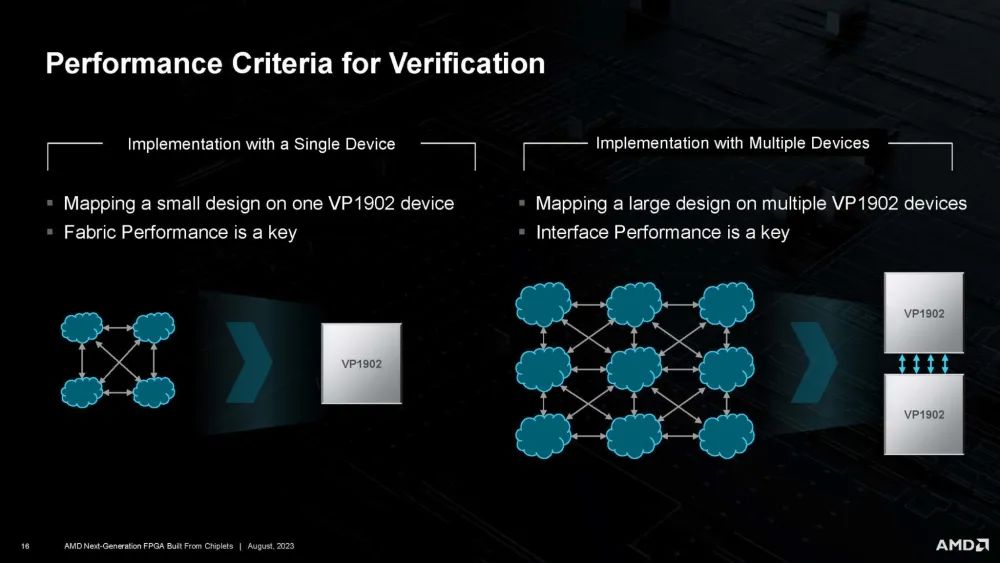

▲ VP1902 设计目的不是当单设备使用,更多以丛集部署,以协助芯片验证和测试。模拟有数十亿个晶体管的现代SoC相当耗费资源,依芯片大小和复杂性,可能需要跨越多个机架、数十甚至数百个FPGA。

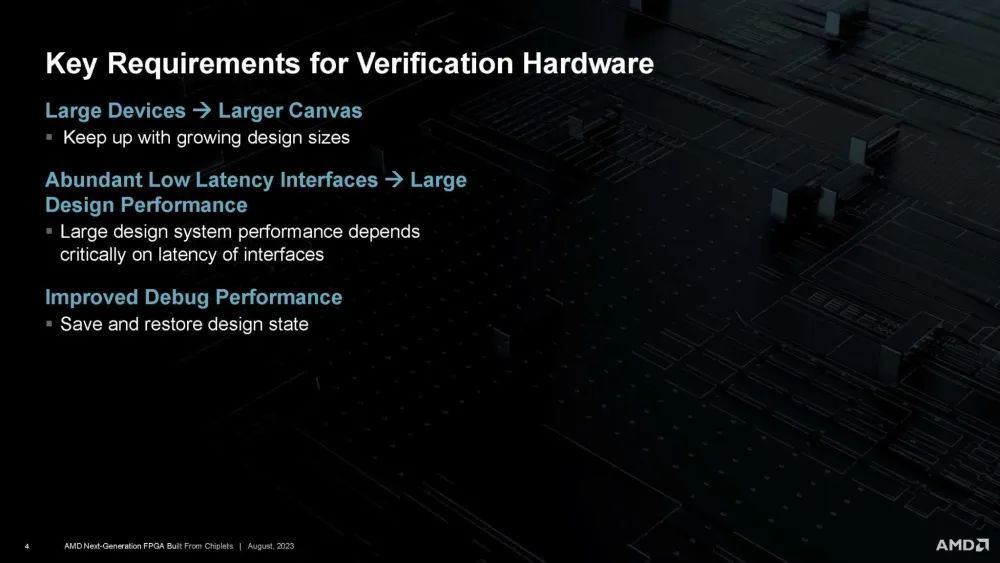

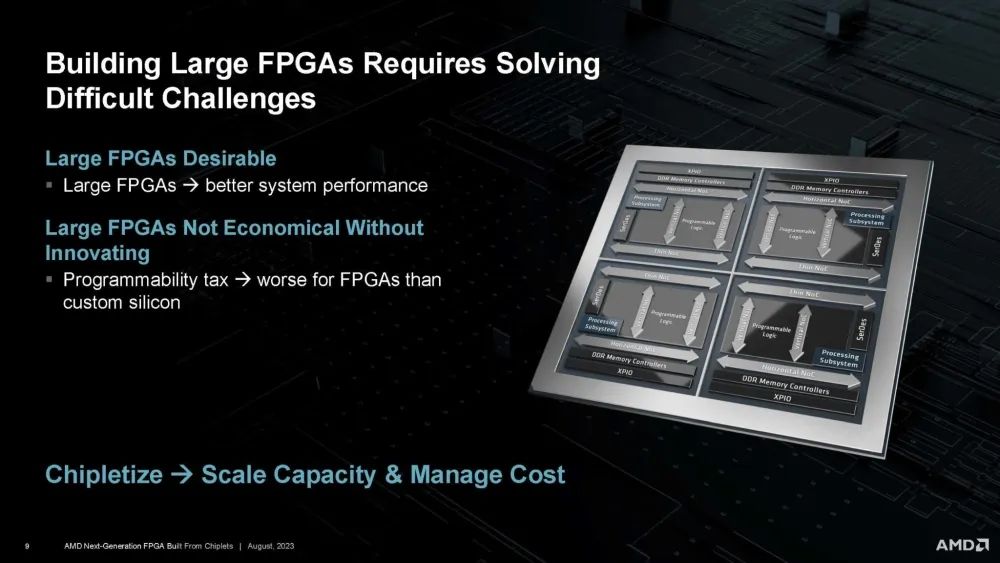

▲ 因为FPGA 电路密度远不如原型设计的晶片,更大FPGA 容纳更大晶片的设计逻辑,或FPGA 丛集放入更大规模设计。

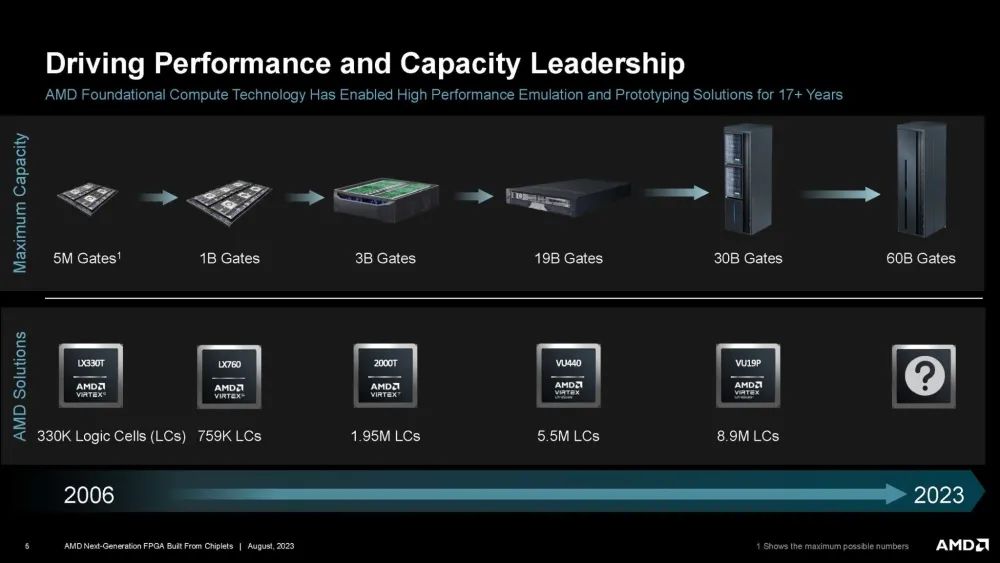

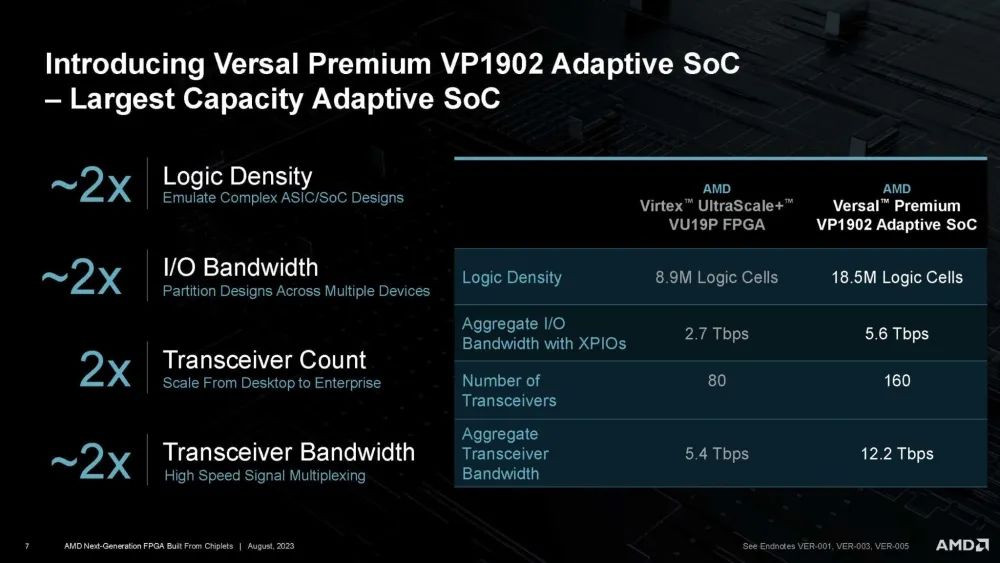

▲ 2019 年 Hot Chips,赛灵思发表 Virtex UltraScale+ VU19P,今年 Versal Premium VP1902 规模则是两倍。

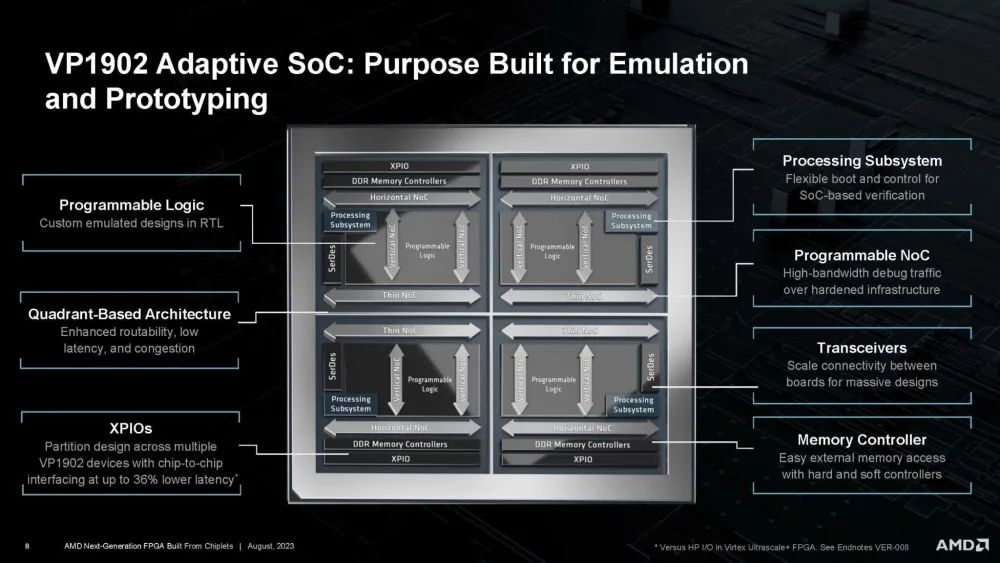

▲ 由四块 Chiplet 组成的 Versal Premium VP1902 逻辑密度是前代两倍,且 AI 专用处理器 Versal 加持后,可提升八倍除错表现。

▲ Versal Premium VP1902 各种性能指标约是上代产品两倍。

▲ Versal Premium VP1902 规格细节。

▲ AMD 藉 Chiplet 技术「经济的」扩大 FPGA 规模。

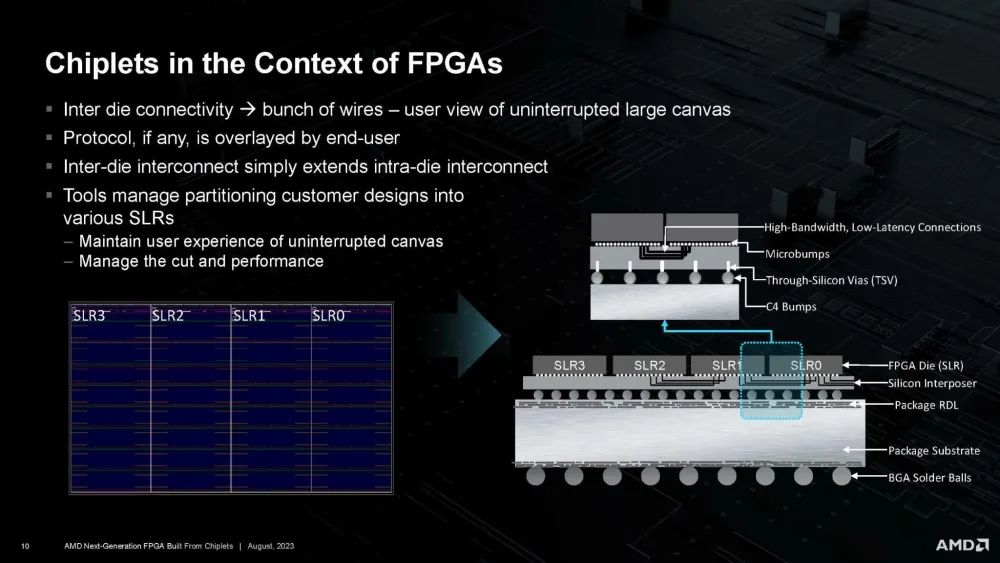

▲ 芯片连接与封装方式,不仅需接合 Chiplet,且还需支持密集的高速 I/O。

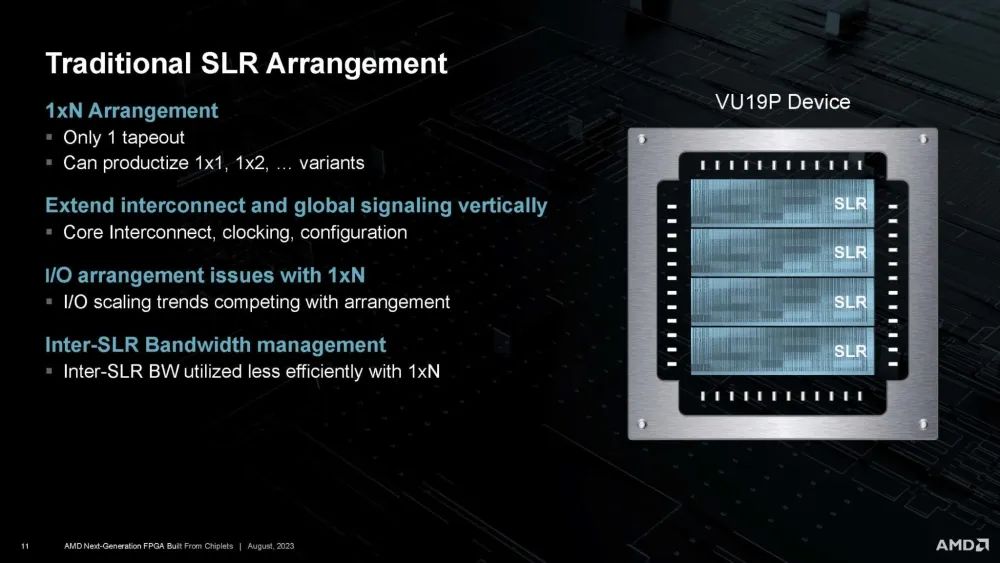

▲ 前代 Virtex UltraScale+ VU19P 的 Chiplet 配置方式。

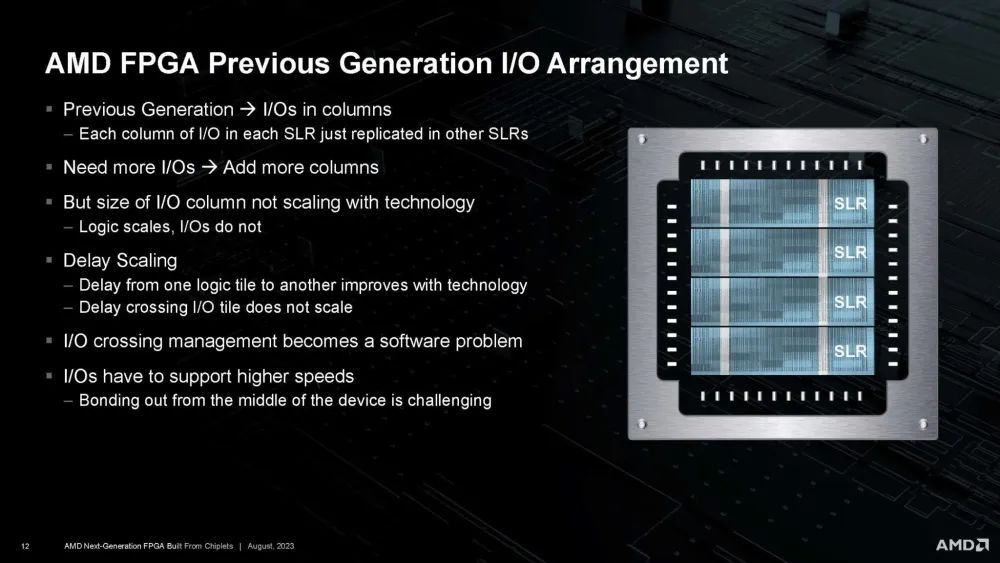

▲ 前代 Virtex UltraScale+ VU19P「又长又宽」配置导致难以扩展 I/O。

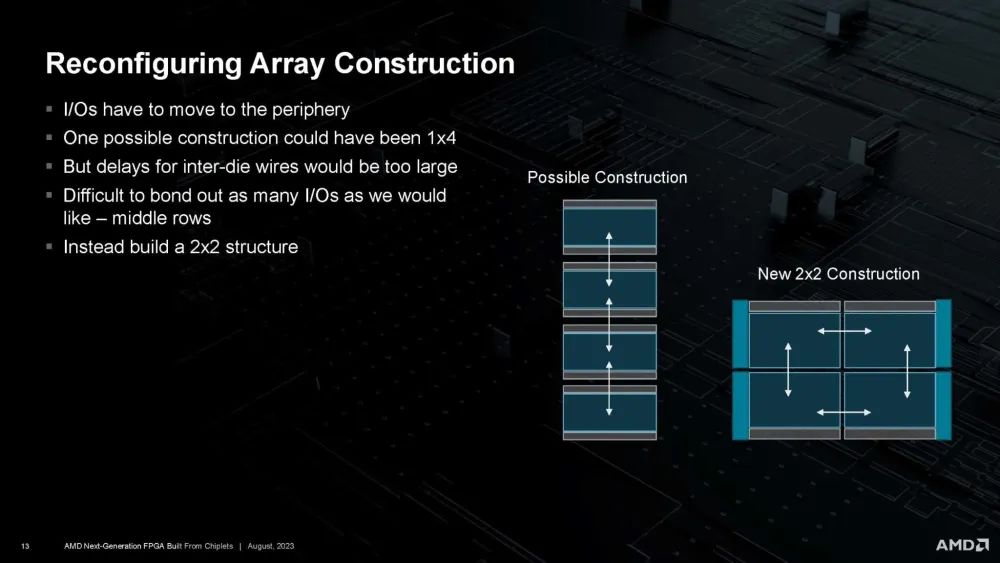

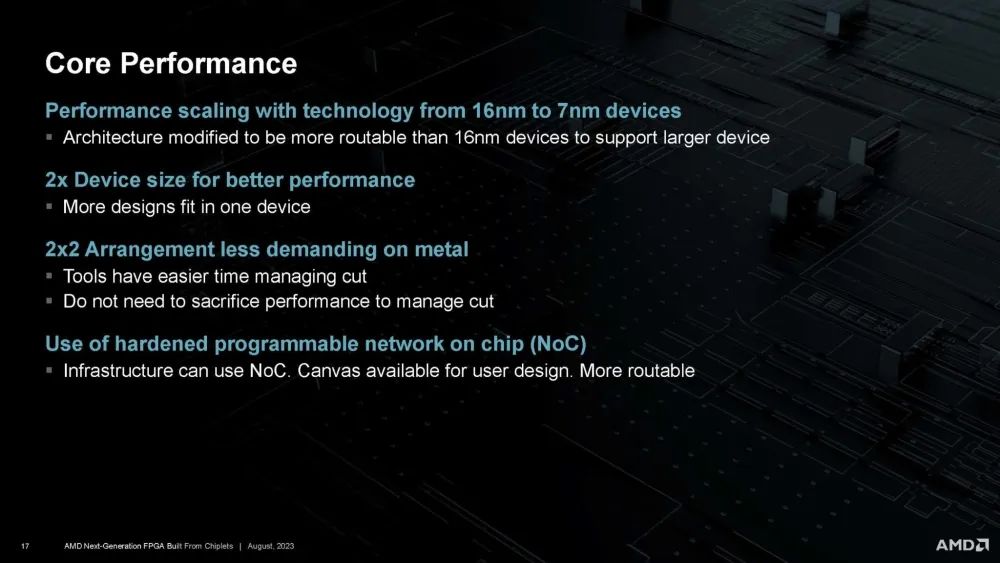

▲ 所以这次从1×4改为2×2,更能平衡Chiplet间的延迟。

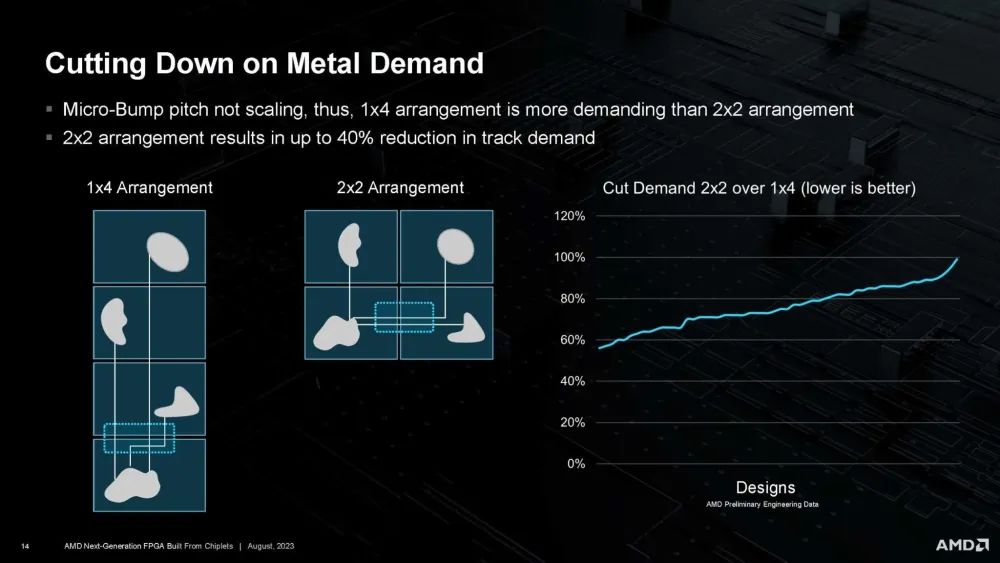

▲ 2×2 Chiplet 亦能减少 40% 导线长度。

▲ 一颗 FPGA不够,可以来第二颗。

▲ 结合更新 7 纳米制程、两倍规模、2×2 Chiplet 排列、可程式化芯片内网路。

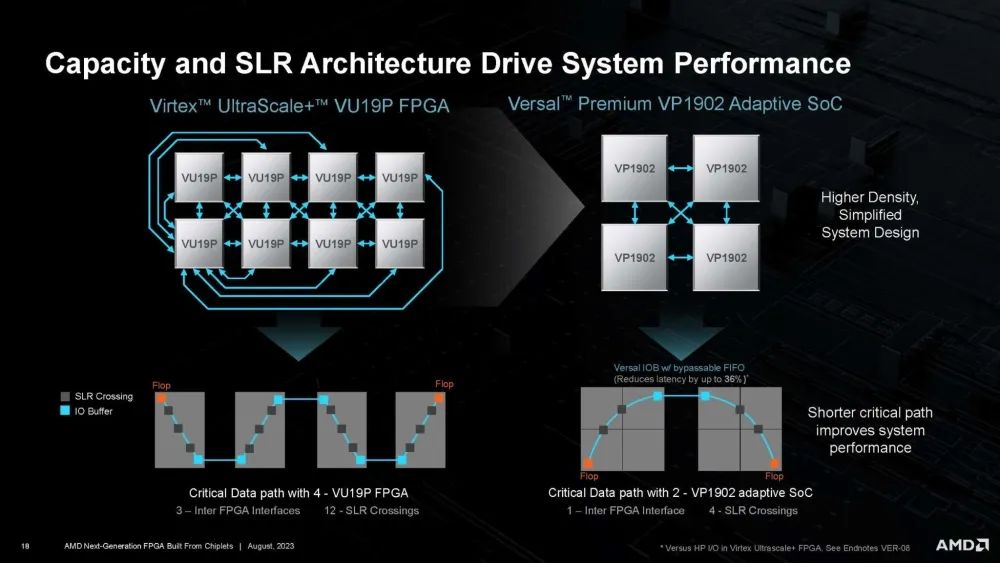

▲ 四颗 VP1902 可比八颗 VU19P 有更高密度和更简单系统设计。

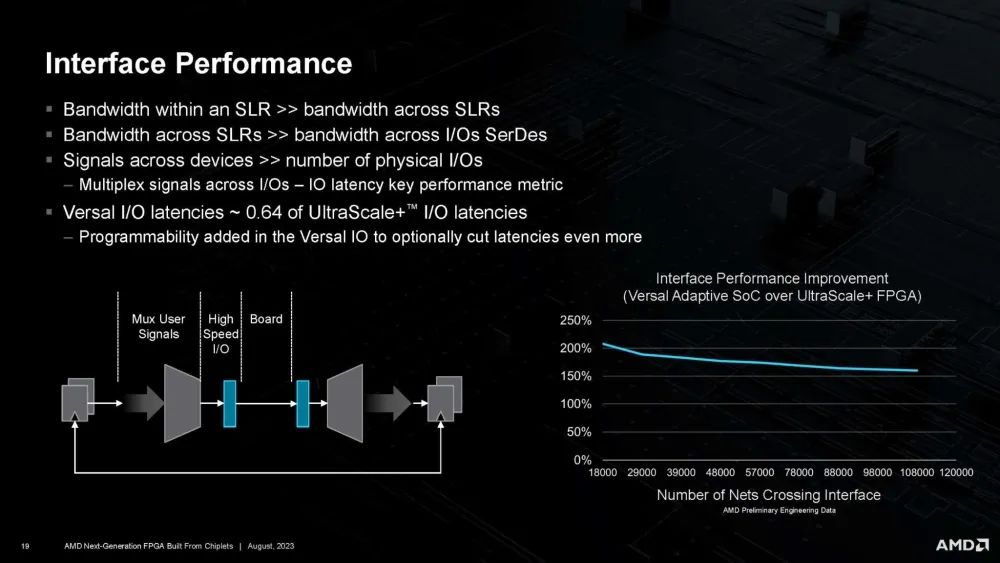

▲ I/O 接口性能。

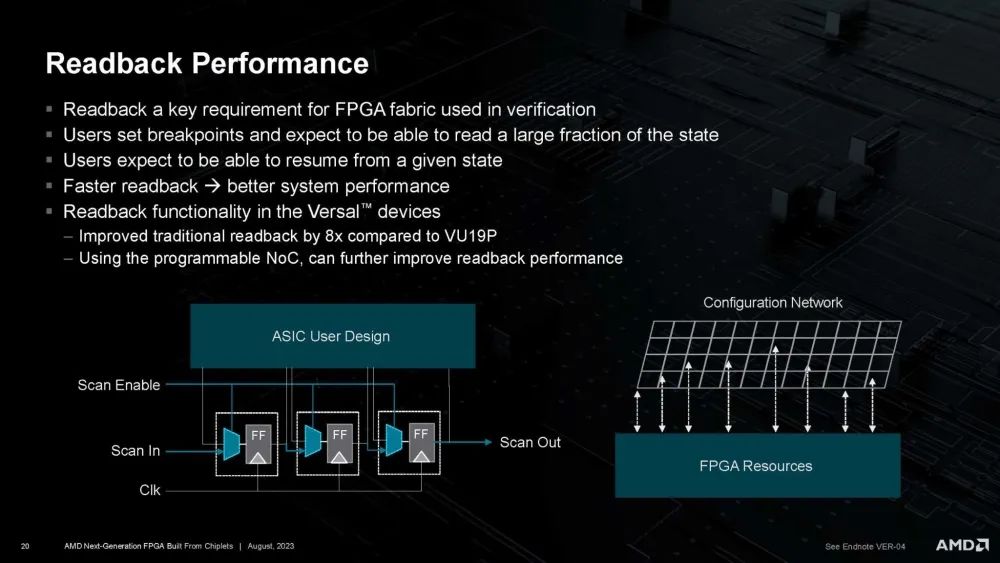

▲ FPGA 读回性能。

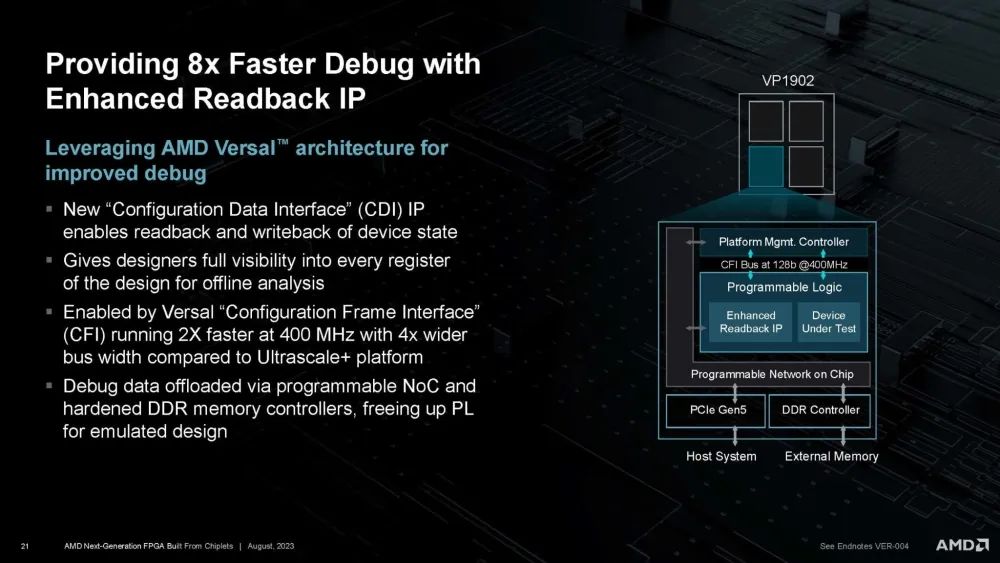

▲ 经Versal加持,达八倍除错效率。

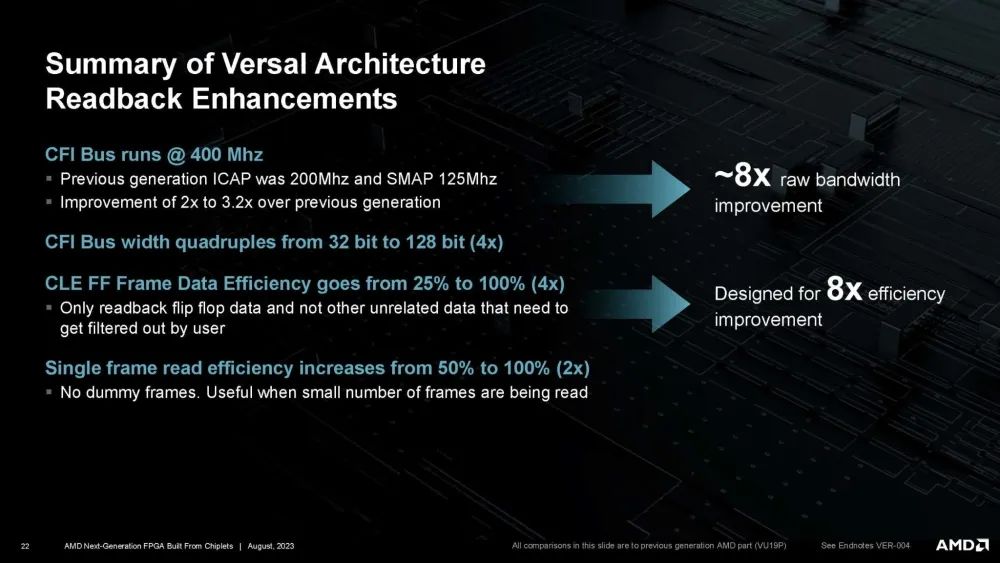

▲ 八倍效率差距就是这样来的。

RFytU1tg/640?wx_fmt=jpeg" data-w="1000" data-index="23" src="https://www.eetop.cn/uploadfile/2023/0914/20230914112407132.jpg" _width="100%" crossorigin="anonymous" alt="图片" data-fail="0" style="margin: 0px; padding: 0px; outline: 0px; max-width: 100%; box-sizing: border-box; overflow-wrap: break-word !important; vertical-align: middle; height: auto !important; width: 677px; visibility: visible !important;"/>

▲ 软件串列扫描链(Scan Chain)的效能提升。

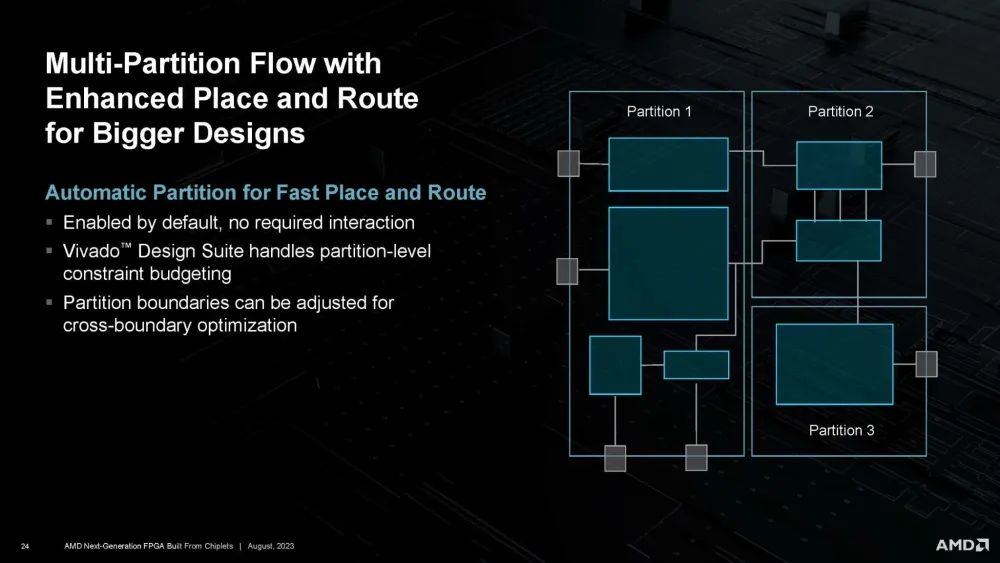

▲ 多层分区流程可更快速布局和布线。

▲ 经过17年发展,赛灵思最新FPGA成为AMD第六代设计模拟装置。 这堪称本届 Hot Chips 罕见的完整简报,内容钜细靡遗,AMD 变相对「靠设计芯片过日子的潜在受众」做了整整 30 分钟广告,但 AMD 也表示,这些 FPGA 也非常适合固件开发和测试、验证 IP 区块和原型开发用。既然AMD都放出世界最巨大FPGA,接着我们就期待手握Altera的英特尔会如何出招吧。