BAW(体声波)技术及应用

2022-12-24 13:42:33 EETOP体声波 (BAW) 技术能够制造出具有可编程频率的紧凑、精确、可靠的时钟,无需储备多个以不同固定频率运行的晶体。BAW 谐振器在确保移动和物联网 (IoT) 设备与云计算资源之间的无缝通信方面发挥着关键且日益重要的作用。

基于 MEMS 的谐振器

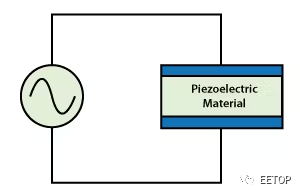

1. 体声波谐振器包括夹在两个电极之间的压电材料。

体声波谐振器是一种微机电系统 (MEMS),由夹在两个电极之间的压电材料组成(图 1)。这种材料可以将电能转化为机械声能,产生可靠的振荡,从而实现高频时钟输出。

比如BAW 谐振器使德州仪器 的 CC2652RB SimpleLink MCU 能够在没有外部晶体振荡器的情况下运行。

MCU 的集成谐振器在不影响延迟的情况下减少了占据PCB的面积并最大限度地降低了物料清单 (BOM) 成本,并且它在整个工作温度和工作电压范围内提供 ±40 ppm 的频率稳定性。此外,2.4-GHz 多协议 MCU 提供超低抖动和相位噪声以满足各种无线通信标准的时钟要求。

TI 还将 BAW 技术集成到其 LMK6C 低抖动、高性能、固定频率振荡器中。它在振动、冲击、温度稳定性和可靠性方面提供增强的抖动性能和改进的可靠性。

最重要的是,该技术还用于 TI 的 LMK05318 高性能网络同步器时钟设备,该设备提供抖动清除、时钟生成和高级时钟监控,以满足通信基础设施和工业应用的定时要求。该器件的超低抖动和高电源噪声抑制 (PSNR) 可以降低贯穿互联世界的高速串行链路中的误码率 (BER)。

BAW 与石英

新的 BAW 技术与古老的石英晶体振荡器竞争,石英晶体振荡器在计时参考市场占据主导地位超过一个世纪。但 BAW 具有显着优势:它消耗的功率更少,允许更小的系统设计,并简化系统集成,同时提供与石英类似或更好的性能。

与 BAW 实施相比,对石英谐振器的回顾有助于说明它们的一些缺点。图 2说明了一种实现石英振荡器的方法——结合石英晶体、振荡电路和输出驱动器。

2. 一个简单的石英振荡器的输出频率取决于晶体(红色)的选择。

设置简单,启动时间快,但其频率完全取决于所选晶体——改变频率需要更换晶体,因此您需要为每个感兴趣的频率储备不同批次的晶体。此外,这种振荡器很少在超过大约 50 MHz 的基频下工作,因为更高频率的晶体难以制造。

图 3中所示的方法克服了其中的一些缺点。在这里,晶体用作锁相环 (PLL) 的参考,它可以产生G赫兹范围内的频率。小数输出分频器可通过内部集成电路 (I 2 C)接口进行编程,编程信息存储在电可擦可编程只读存储器 (EEPROM) 中,生成所需的频率。

RFicxicUWCYywENdt722v3q2Oo5TcYPQ/640?wx_fmt=png" data-type="png" data-w="600" data-index="4" data-origin-display="inline" _width="600px" crossorigin="anonymous" alt="图片" src="https://www.eetop.cn/uploadfile/2022/1224/20221224014310844.jpg" data-fail="0" style=";padding: 0px;outline: 0px;max-width: 100%;box-sizing: border-box !important;overflow-wrap: break-word !important;vertical-align: bottom;height: auto !important;float: none;display: inline;visibility: visible !important;width: 600px !important"/>

3. 小数输出分频器可对输出频率进行编程。

然而,这种方法比图 2中的方法需要更多的核心块,从而导致更大的封装尺寸和更高的功耗。此外,启动时间很慢,因为 PLL 需要 10 ms 或更长的时间来校准和锁定。

图 4显示了一个带有集成 BAW 谐振器的振荡器,该谐振器取代了外部晶体。与图 3的电路一样,小数输出分频器根据存储在存储器中的编程值生成所需的频率。TI可以采用四引脚或六引脚封装(分别用于单端和差分输出)制造此类设备。

4. 具有单端输出的 BAW 振荡器适合四引脚工业标准封装。

每个这样的设备都将其电路集成在采用深亚微米工艺技术设计的基础芯片上。位于同一位置的传感器持续监控温度变化,信号处理算法使用存储在非易失性存储器中的校准系数将频率保持在 ±10 ppm 预算范围内。低抖动低功耗小数输出分频器可实现温度补偿,同时对相位抖动的影响极小。除了温度稳定性外,该器件还提供良好的相位噪声性能,差分输出版本将抖动限制在 125 fs。

基于 BAW 的设备包括内部低压差稳压器 (LDO),以提供改进的 PSNR。它还符合 MIL-STD-2007 Condition A 和 MIL-STD-2002 Condition A 对冲击和振动的要求,振动引起的频率偏差限制在 1 ppb/g 左右。与石英振荡器相比,这几乎是一个数量级的改进。

FPGA 的时钟生成

FPGA 设计通常需要灵活的高性能振荡器或时钟发生器 IC 来提供一个或多个时钟输入。FPGA 的串行器/解串器 (SERDES) 收发器通常依赖具有低集成均方根 (RMS) 抖动的外部参考时钟来最大限度地减少收发器位错误。BAW 谐振器可以轻松生成 FPGA 设计所需的频率。

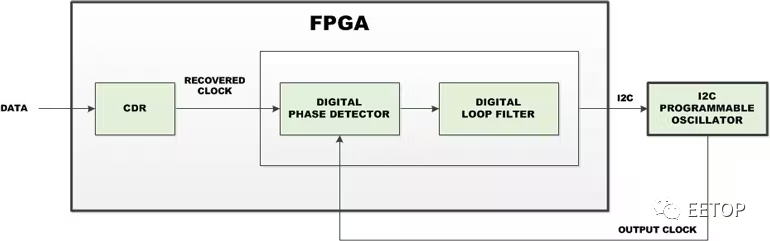

对于需要从串行数据流中恢复时钟信号的应用,串行可编程谐振器可以用作基于 FPGA 的时钟数据恢复 (CDR) 电路中的数控振荡器。

如图 5所示,FPGA 逻辑实现了数字鉴相器和数字环路滤波器。后者通过I 2 C接口将控制字写入可编程振荡器寄存器。然后振荡器根据这个环路滤波器控制字调整它的输出频率。跟踪恢复时钟所需的频率调整通常以百万分之一来衡量(例如,小于标称值的 ±50 ppm)。

5.数控可编程振荡器服务于FPGA中实现的CDR电路。

结论

BAW 谐振器提供了扩展应用的灵活性,从包含 MCU 的物联网边缘设备到采用 FPGA 的高性能系统。带有串行编程接口和板载 EEPROM 的版本提供了支持多种频率和简化整个产品生命周期的灵活性。与基于石英晶体的谐振器相比,体声波谐振器将高性能、可靠性和可用性与较短的交货时间和简化的供应链管理相结合。

原文

https://www.electronicdesign.com/tools/learning-resources/whitepaper/21256004/texas-instruments-the-connected-world-marches-to-the-beat-of-baw-technology