返璞归真--设计消除 PPA 风险

2023-07-26 12:58:11 EETOP编译自semiwiki我之前写过有关管理 SoC 设计中的服务级别风险的文章,因为系统在实际流量下可以保证的最低服务级别对于 OEM 保证可靠的系统性能至关重要。也就是说,满足 PPA 目标仍然是成功设计的核心基准。假设架构设计和 IP 应能够满足这些目标,PPA 仍然是先进工艺中高复杂性 SoC 设计的主要风险来源。

原因很容易理解,先进的设计依赖于具有高水平并行性的先进架构,通过非常复杂的通信互连网络连接许多内核。该互连占设计面积的 12% 或更多,其功耗远高于内核的功耗,而且由于它跨越通常非常大的芯片,因此高效设计对于性能至关重要。PPA 目标取决于系统设计、功能设计和物理布局规划,如果不平衡这三者,就无法安全地保证这些目标。

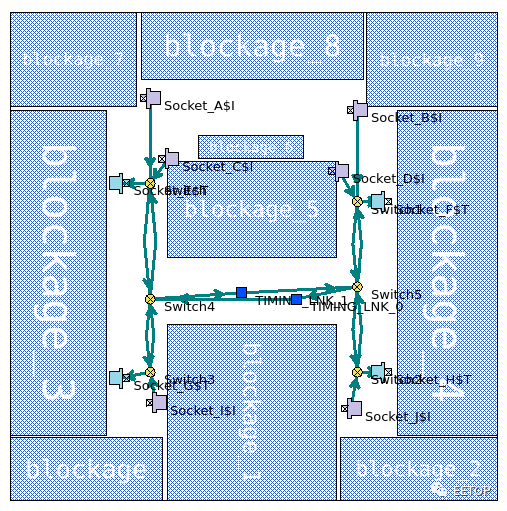

如果没有floorplan,就很难考虑floorplan的限制因素。幸运的是,在产品规划之初,就应该对设计中主要功能的布局有一定的了解,即使这只是一张手绘草图。可以将草图中的区块作为物理约束来指导 NoC 设计规划工具。

这将允许您评估拓扑(上例中的树)、NoC 组件布局以及可用区域内的资源利用率。通过可视化布局规划中的 NoC 设计,您可以识别未充分利用或资源分配过多的区域。这种见解有助于优化区域利用率、减少不必要的资源重复并提高整体区域效率。

在此视图中进行规划还允许通过路由进行近似延迟估计,从而使您能够沿着延迟关键路径规划延迟最小化,或在可以处理增加的延迟的路径中添加管道。同时,您可以权衡带宽和网络链路宽度之间的权衡。宽链路将支持更高的带宽,但可能会增加该区域的拥塞,这在详细的计划视图中应该很明显。

您还可以考虑最大程度地减少面积/拥塞的其他选项,包括压缩/解压缩(在发起方/目标处处理)以及通过长路由的流量复用。您仍然为这些方法提供机制;平面图视图有助于强调在构建 NoC 时做出这些选择的必要性。

在设计进度的后期,当有更完整的平面图可用时,可以对这些选项进行微调以优化该floorplan。鉴于上面定义的早期优化,这实际上将是微调,而不是如果第一个设计被证明不够灵活,无法适应布局规划,则可能会进行 NoC 拆除和重新设计。

NoC 架构相对于交叉结构的一个非常好的优势是,它们可以在内部控制动态和静态功耗,就像您可以控制设计中的其他逻辑一样。时钟门控当然是一种选择,但在本主题的背景下,还值得考虑功率门控和电压缩放选项(在这种情况下通常是后期优化)。利用这些选项取决于对电源/电压域的访问,这些域必须位于布局规划中。您应该拥有有关功能块(CPU、GPU 等)的域支持的信息,建议附近 NoC 元素中域支持的可能性。

采用先进工艺构建的复杂 SoC 中的互连设计可能是导致 PPA 风险的重要因素,从而导致无法达到目标规格或设计进度。这种风险在很大程度上是当今先进设计中架构、微架构和实现之间紧密耦合的一个因素。

当在 SoC 布局规划的背景下考虑互连设计(最初估计并随后完善)时,这种风险是非常可控的。