台积电分享更多关于2纳米的技术细节

2023-06-02 11:10:03 EETOP台积电在其 2023 年欧洲技术研讨会上透露了有关其即将推出的N2 和 N2P 工艺技术的更多细节。这两个生产节点的开发都考虑到了高性能计算(HPC),因此,它们具有许多专门设计用于改进的增强功能表现。同时,鉴于大多数芯片旨在改进的性能效率重点,低功耗应用也将利用台积电的N2 节点,因为与前代产品相比,它们自然会提高每瓦性能。

“N2 非常适合我们今天所处的节能计算范式,”负责代工厂高性能计算业务部门的台积电业务发展总监Yujun Li 在公司2023 年欧洲技术研讨会上说。如图所示,在整个电压供应范围内,N2相对于 N3 的速度和功率优势非常一致,使其同时适用于低功率和高性能应用。”

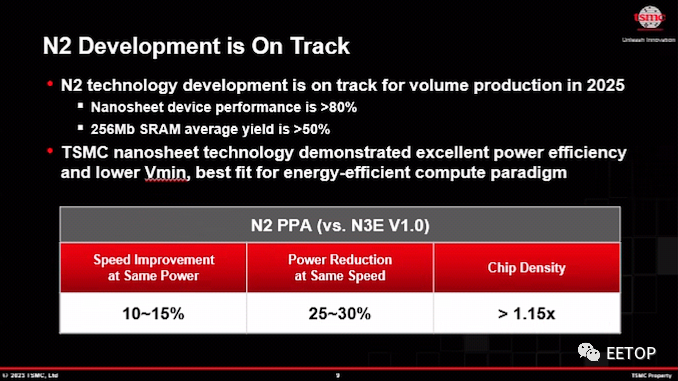

台积电的N2制造节点--该晶圆厂的第一个使用纳米片栅极环绕(GAAFET)晶体管的生产节点--承诺在相同的功率和复杂性下将晶体管性能提高10-15%,或者在相同的时钟速度和晶体管数量下将功率使用降低25-30%。在提高晶体管性能方面,功率传输是基石之一,台积电的N2和N2P制造工艺引入了几个与互连有关的创新,以挤压一些额外的性能。此外,N2P引入了背面电源轨,以优化电源传输和芯片面积。

N2带来的创新之一是超高性能金属绝缘体-金属(SHPMIM)电容器,以增强电源稳定性并促进片上去耦。台积电表示,与几年前为HPC推出的超高密度金属-绝缘体-金属(SHDMIM)电容器相比,新的SHPMIM电容器的容量密度提高了2倍以上(与上一代HDMIM相比,其电容提高了4倍)。与SHDMIM相比,新的SHPMIM还将Rs片状电阻(欧姆/平方)降低了50%,而Rc通孔电阻也比SHDMIM降低了50%。

然而,减少电力输送网络中的电阻的另一种方法是重新构建再分配层(RDL)。从其N2工艺技术开始,台积电将使用铜RDL而不是今天的铝RDL。铜RDL将提供类似的RDL间距,但将减少30%的薄层电阻,并将通孔电阻减少60%。

SHPMIM和铜RDL都是台积电N2技术的一部分,预计将在2025年下半年用于大批量生产(HVM)。

去耦电源和I/O布线

使用背面电源输送网络(PDN)是N2P的另一项重大改进。背面电源轨的一般优势是众所周知的:通过将电源轨移到后面来分离I/O和电源布线,有可能使电源线变粗,从而减少线路后端(BEOL)的通孔电阻,这有望提高性能和降低功耗。此外,将I/O和电源线解耦可以缩小逻辑面积,这意味着成本降低。

在2023年技术研讨会上,该公司透露,其N2P的背面PDN将通过减少红外衰减和改善信号,使性能提高10%至12%,并使逻辑面积减少10%至15%。当然,现在这样的优势在高性能的CPU和GPU中会更加明显,这些CPU和GPU拥有密集的电源传输网络,因此将其移到背面对它们来说是非常有意义的。

Backside PDN 是台积电 N2P 制造技术的一部分,将于 2026 年底或 2027 年初进入 HVM。