苹果 M1 UltraFusion 芯片互连背后的技术--台积电CoWoS-S

2022-03-12 13:03:20 未知

如今,构建高性能微处理器变得越来越棘手,成本也越来越高,这就是为什么开发人员必须选择复杂的封装技术以及针对性能要求高的应用程序的设计。苹果承认,要制造其 M1 Ultra 处理器,它必须将两个 M1Max SoC芯片融合在一起,但它没有说它必须使用台积电最先进的封装技术之一来制造 M1Ultra。

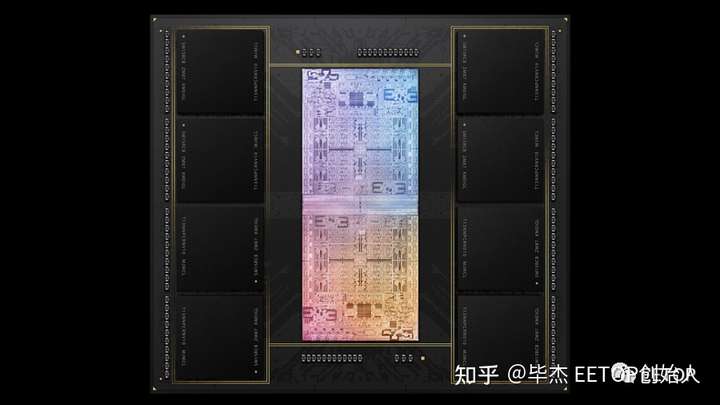

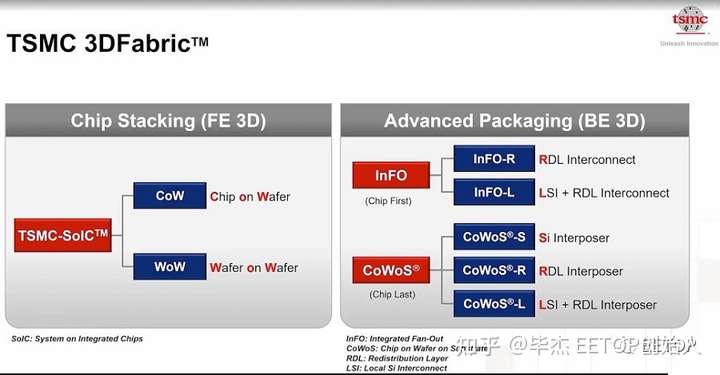

幸运的是,非官方消息来源没有苹果公司那么神秘,并且能够挖掘出有关苹果公司 UltraFusion 处理器间互连的更多细节,该处理器提供 2.5TB/s 的带宽。DigiTimes 报道称,Apple的 M1 Ultra 处理器使用了台积电的 CoWoS-S(带有硅中介层的晶圆上芯片)基于 2.5D中介层的封装工艺来构建 M1 Ultra。AMD、Nvidia和富士通等公司也使用类似的技术来构建用于数据中心和高性能计算 (HPC) 的高性能处理器。

Apple 的 M1 Ultra 无疑是一个强大的设计。每个 M1 Max SoC 的裸片尺寸为 432mm2,因此 M1 Ultra 使用的中介层必须超过 860mm2。这是相当大的,但并非闻所未闻。AMD 和 Nvidia 使用更大的中介层,其计算 GPU 具有高带宽内存。

- 我们不知道如何称呼 M1Ultra。从技术上讲,这是一个系统级芯片封装,或SoCiP,但这可能有点拗口,所以我们现在还是称它为“处理器”。

但台积电的 CoWoS-S 并不是这家全球最大的半导体合同制造商在带宽密集型应用中的唯一选择。一些专家推测,苹果可能会选择台积电的InFO_LSI 技术进行超高带宽小芯片集成。与 CoWoS-S 不同,InFO_LSI 使用局部硅互连而不是大型且昂贵的中介层。英特尔的嵌入式芯片互连桥(EMIB) 使用相同的概念。请记住,Apple 展示了带有大型 I/O 焊盘的 M1Max die shot,该焊盘类似于旨在连接到中间芯片的本地互连,因此许多人认为Apple 使用了 InFO_LSI 也就不足为奇了。

但苹果可能坚持使用可能更昂贵的CoWoS-S是有原因的。台积电的InFO_LSI于2020年8月正式推出,原定于2021年Q1完成认证。同时,Apple的M1 Max将于2021年Q2或Q3进入量产,因此苹果可能根本没有足够的时间实施InFO_LSI。或者它决定不冒险并坚持使用被各种公司广泛使用的技术。