北航类脑芯片团队提出“混合概率逻辑计算”机制(FPGA原型机已实现!)

2022-02-08 13:01:11 EETOP近几年,随着人工智能、深度学习的迅速发展,类脑计算逐渐成为学术界、产业界的另一个研究热点。早在1943年,心里学家提出人工神经元数学模型以来,人工智能就一直依赖着数据计算、神经科学的发展,对非二进制数的类脑计算的突破,将对类脑计算的构造起到决定性作用。

今天,深度学习神经网络是一种生物学简化的模型,具有数学可解释性,硬件架构(冯诺依曼架构)可实现性。而硬件实现受限于布尔逻辑(二进制数)和冯氏架构代来的物理瓶颈,使得当前的AI计算芯片与脑计算存在着巨大差异。尽管深度学习在一些固定任务上超越人类,但数百亿神经元由树突和轴突连接成的大脑在完成学习、认知、推理、抽象等多种复杂智慧功能时,还是当前人工智能的平台所无法企及的。

脉冲神经网络(Spiking Neural Network,SNN)由W.Maass在1997年首次提出,其底层用脉冲函数模仿生物点信号作为神经元之间的信息传递方式。SNN的优点是具有更多的生物解释性,一方面可以作为计算神经学对生物脑现象模拟的基础工具;另一方面,由于其信息用脉冲传递的特点,而非人工神经网络的二进制数,其结构也容易在FPGA、ASIC等芯片上实现。但是,离散的脉冲函数不可导,因此脉冲信号不能直接应用反向传播的梯度法进行训练,是其难以构造复杂网络而应用受限的主要因素。

2、研究成果

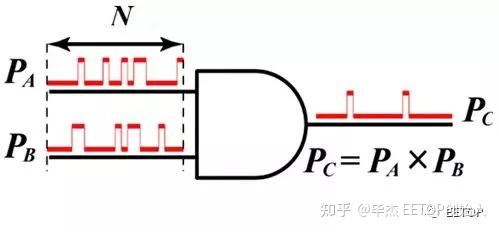

众所周知,二进制逻辑(布尔代数)中,通常用0和1表示两个变量值中的一个。二进制逻辑是目前数据计算、信息传输的基础。在计算N*N维的矩阵乘法时,每计算一个矢量元素将需要N^2个加法和乘法!为了减小二进制计算的硬件资源消耗,一种有别于布尔逻辑的概率(逻辑)计算(Stochastic Computing,SC,或Stochastic Logic)在1969年由B. Gaines 提出【1】。

概率计算机中,算术运算是借助于表示数据的逻辑电平的随机和不相关性来执行的,并且由其“高电平”所占的概率来决定。也就是所发生的“高电平”脉冲的频率表示其概率值。即遵循古典概型伯努利所证实的“当试验次数愈来愈大时,频率接近概率”。概率计算已经在图像处理、通信、神经网络和深度学习中被使用【2】。

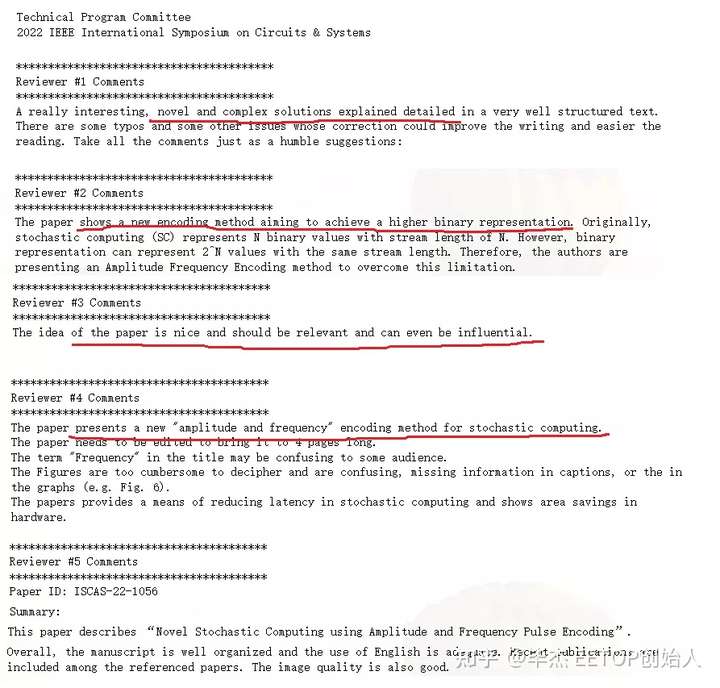

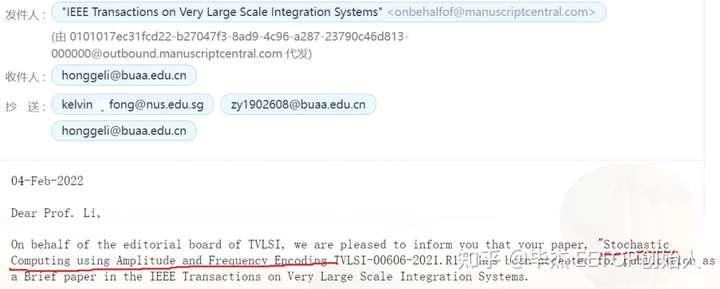

北京航空航天大学类脑芯片教授李洪革谈到:“尽管概率计算比二进制计算存在硬件消耗上的巨大优势,但其基于脉冲频率表示概率数值的本质带来了较大的计算时延的问题。”基于此,本团队提出了混合概率逻辑计算取代原始单比特流概率计算的思想。在2022年伊始,该思想被国际电路与系统顶会ISCAS和IEEE 权威期刊TVLSI等多位国际专家所认可并全文接收。其中,一位评审专家甚至给出评语是”the paper is nice and should be relevant and can even be influential.”

3、 研究亮点

提出了基于概率逻辑计算与二进制逻辑的混合逻辑计算机制;

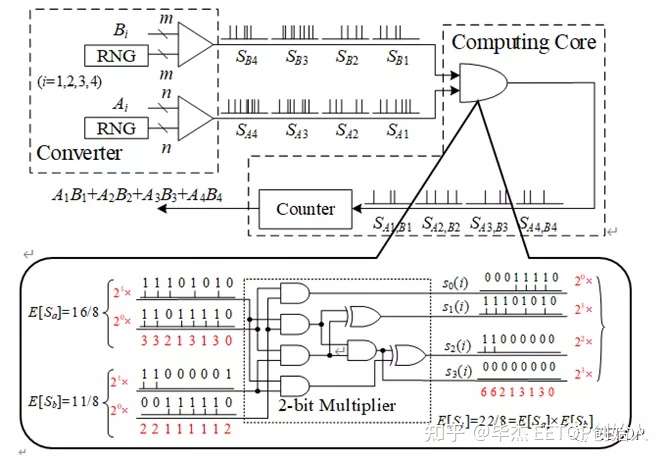

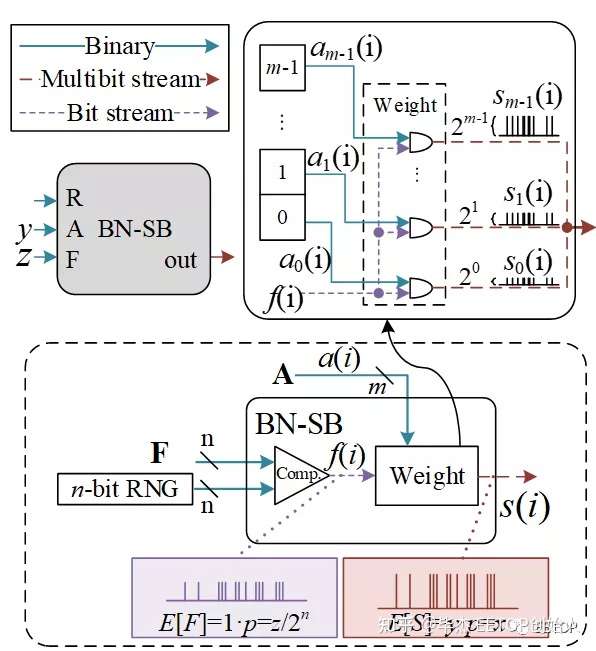

构造了混合逻辑计算机制的各计算电路模块,如图1、图2

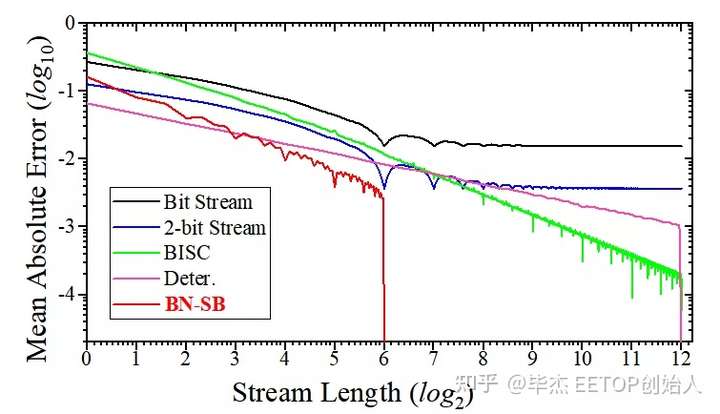

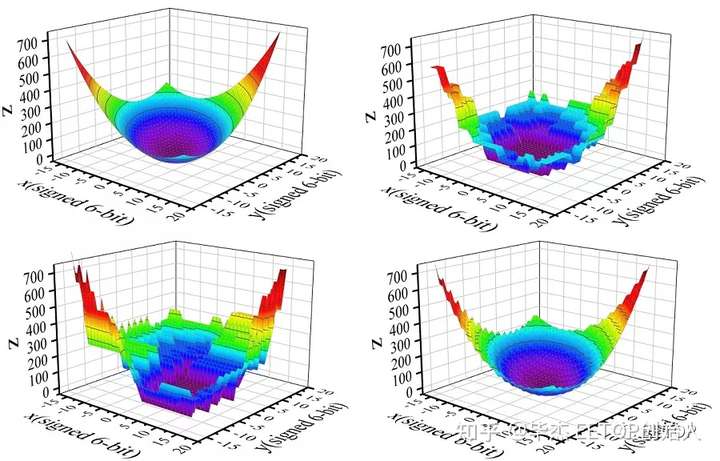

讨论了基于混合逻辑计算的误差分析和容错机制,如图3、4

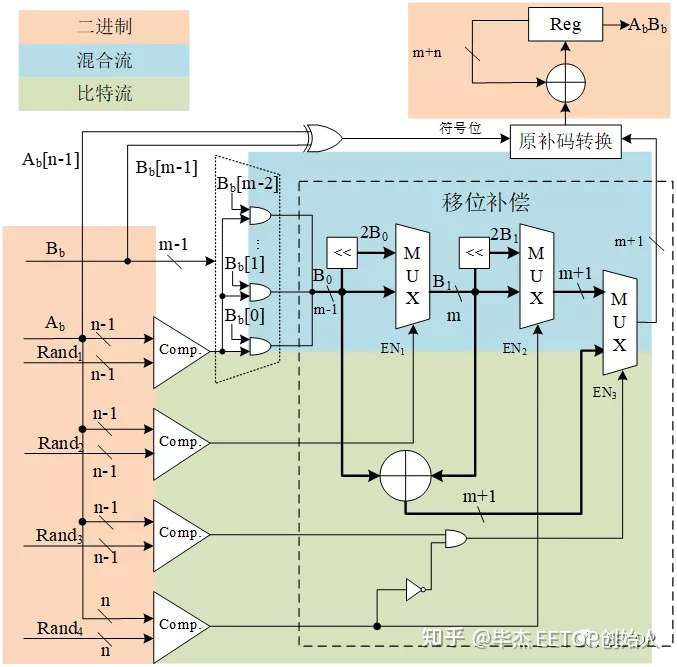

构建了混合逻辑流的多核类脑计算网络加速器芯片,如图5、6.

4、结论展望

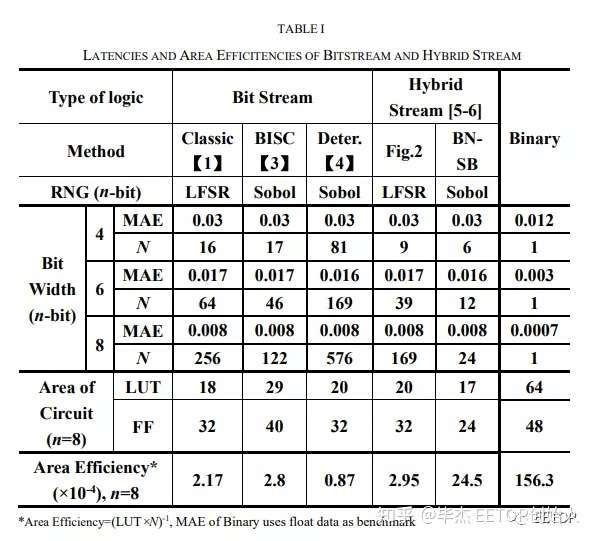

北航类脑计算芯片团队提出了一种新的数字计算(有别于二进制、概率计算)——混合逻辑SC。该方法利用多位流的期望值来取代传统概率计算。与传统的单比特流相比,混合逻辑计算突破了传统SC长时延的制约,实现了低时延和低面积。实验证明了混合逻辑计算规则的合理性,使用该方法乘法器延迟降低了1/2m,且达到零错误计算。对于8-bit输入数据,混合逻辑作为乘法器的面积效率是经典SC方法的11.3倍。

凭借该技术方案,团队荣获全国研究生创芯大赛一等奖,陈宇昊博士补充到。最后,李洪革教授谈到,该提案解决了传统概率计算大时延问题,在未来的类脑计算、人工智能、深度学习和信息处理等边缘计算产业将会产生影响力的(influential)发展契机。

参考文献

B. R. Gaines, “Stochastic computing systems,” in Advances in Information Systems Science, J. T. Tou, Ed. New York, NY, USA: Springer, 1969, pp. 37-172.

Hongge Li, Y. Hayakawa, S. Sato, K. Nakajima, “Hardware Implementation of an Inverse Function Delayed Neural Network using Stochastic Logic,” IEICE Trans. Inf. Syst., vol.E89, pp.2572-2578, 2006.

H. Sim , J. Lee, “A new stochastic computing multiplier with application to deep convolutional neural networks,”in Proc. 54th Annu. Design Automat. Conf. (DAC), p. 29, 2017.

D. JENSON, M. RIEDEL. “A deterministic approach to stochastic computation”. ACM International Conference on Computer-Aided Design (ICCAD), 2016:1-8.

YuHao Chen,HongGe Li,“Novel Stochastic Computing using Amplitude and Frequency Pulse Encoding“ ISCAS 2022.

Yuhao Chen,Hongge Li,“Stochastic Computing using Amplitude and Frequency Encoding“ IEEE TVLSI 2022,accepted。

Y Chen, Y. Song, Y. Zhu, Y. Gao, H. Li. “Hardware Architecture of Stochastic Neural Network”. Journal of Frontiers of Computer Science and Technology, 2021: 1-12.

李洪革 北京航空航天大学教授、博士生导师

IEEE\IEICE\SID\CCF\电子学会高级会员;国家多个部委专家;CCF集成电路设计专委会委员、密码芯片专委会委员等,申请国家专利30余项,其中获发明专利授权18项。发表论文近百篇,他引300余次,70余篇被SCI、EI和ISTP三大索引收录,第十届人工智能大会等特邀报告近10次。承担科技部、自然基金委等国家项目十余项。出版专著教材4部,获省部级科技进步、发明奖三项。

研究领域:集成电路芯片设计与智能计算等

陈宇昊 福建泉州, 博士研究生在读

主要研究方向为人工智能、类脑计算和芯片设计等。设计实现了混合概率逻辑FPGA硬件计算系统,完成了类脑计算FPGA原型机。获得第四届全国研究生创芯大赛一等奖。

(其他参与人员:祝亚楠、高云飞、宋印杰、郭晓宇等)