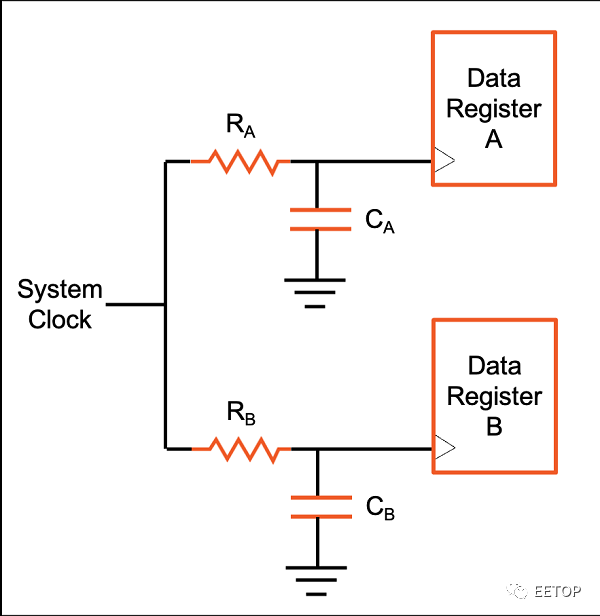

EETOP编译自allaboutcircuits

本文将通过了解同步电路、时钟传输和时钟分配网络,进而了解什么是时钟偏差(clock skew)以及它对现代系统的影响。

现代数字电子产品设计的最大挑战之一是满足时序约束的能力。保持可预测和组织良好的操作逻辑流程的方法之一是在数字电路中拥有控制良好、定义明确的时序。clock skew是这些电路中的一个设计考虑因素,如果没有得到适当的考虑,它可能是一个重要的问题来源。事实上,在许多情况下,系统的clock skew可能是整个系统速度和时钟频率的限制因素。要了解clock skew,我们必须首先讨论同步电路。同步电路需要一种计时机制来保持有序和周期性的时序逻辑流。在数字电子学中,这种计时机制被称为时钟,简单来说,它是一个具有恒定频率 的方波。如图 1 所示,这些电路通过将静态数据存储在数据寄存器中来工作,该数据寄存器旨在锁存数据,直到寄存器遇到时钟的上升(或下降)沿。当时钟沿发生时,数据从寄存器中释放,通过组合逻辑块发送,然后存储在下一个寄存器中。

图 1. 具有两个顺序寄存器的数据路径同步电路。

这些操作发生的频率由时钟频率设置,时钟频率由其他几个参数设置。最小时钟周期的一般公式定义为:

Tc是时钟周期

tpcq是数据寄存器时钟到 Q 的时间

tpd是组合逻辑传播延迟

tsetup是下行寄存器的建立时间

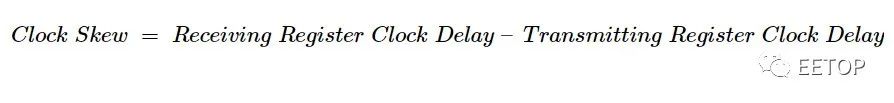

由于数字逻辑往往是同步电路,所有逻辑块的精确时序对于正确的系统行为至关重要。当考虑将图 1 中的设置从一个数据路径扩展到数百万个数据路径(因为它存在于实际芯片设计中)时,很快就会发现保持一切同步是一项不小的挑战。在实践中,时钟信号通常由晶体振荡器生成,馈入锁相环 (PLL),并在整个 IC 中分布到系统内的每个逻辑块和晶体管。这种追求中最大的挑战之一就是clock skew,它可以定义为顺序相邻寄存器的时钟信号到达时间之间的差异。

发生clock skew的传统设置如图 2 所示,其中时钟分配网络中的延迟导致数据寄存器 B 比寄存器 A 更晚地接收其时钟信号。

图 2. 时钟偏差通过在时钟传输网络中插入延迟来证明。

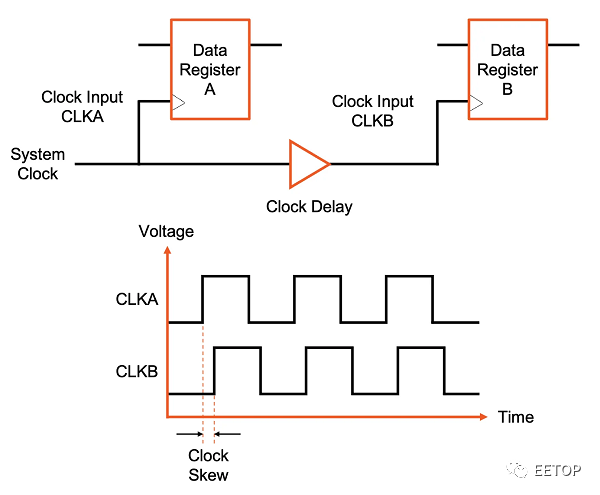

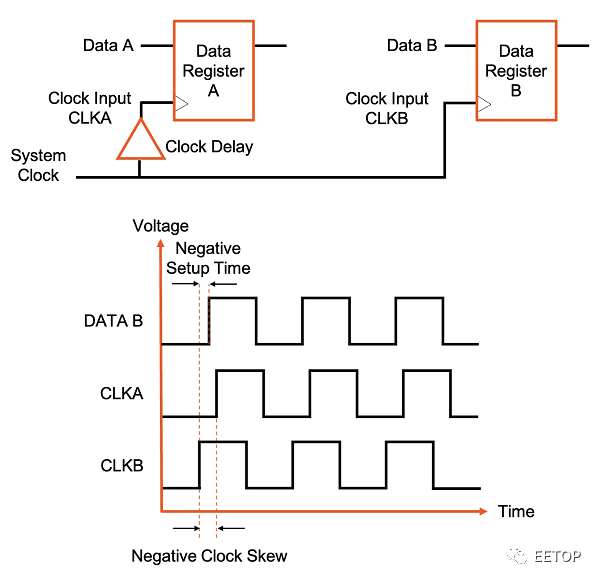

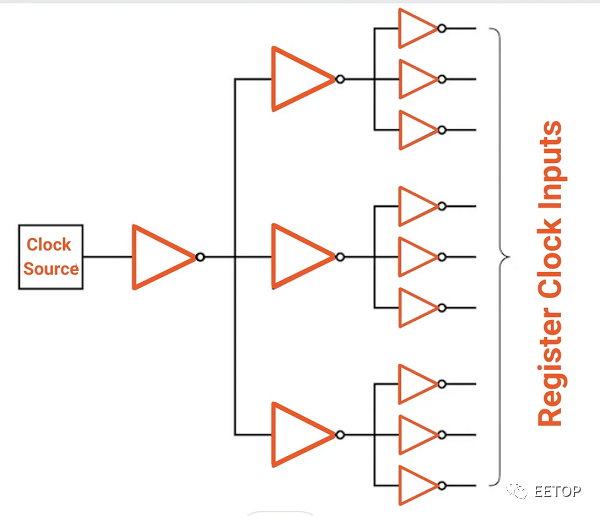

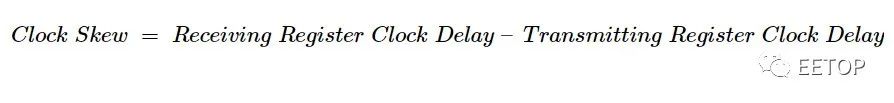

如果接收寄存器晚于发送寄存器接收时钟,则偏移可以定义为正,反之则定义为负。clock skew成为数字设计中的一个严重问题,因为它可能违反同步电路所依赖的时序约束。 例如,给定一个恒定的时钟频率和负偏斜,如图 3 所示,时钟到达接收寄存器 B 的时间要比发送寄存器 A 早得多。在这种情况下,从发送寄存器发出的数据将到达时钟到达后接收寄存器。这里,数据不满足接收寄存器的建立和保持要求(即,在时钟到达时,接收登记处还没有现成的数据)。因此,由于接收寄存器不能安全地锁存数据,数据将会丢失。这个概念会产生复合效应,因为后续依赖丢失数据的逻辑操作也会失败。图 3. 负时钟偏移导致数据在其时钟之后到达接收寄存器 B。正如我们在最大时钟频率等式中看到的,clock skew的增加将增加最小时钟周期并降低系统的最大时钟频率。这是因为clock skew有效地增加了排序开销,减少了组合逻辑中有用工作的可用时间。还值得注意的是,时钟不需要同时到达,但clock skew通常存在可接受的误差范围。虽然造成clock skew的原因有很多,但它们最终都归结为时钟分配网络中的延迟差异。 clock skew的一个原因是时钟分配网络中互连之间的长度不同。如果到两个连续寄存器的时钟传输路径中的互连长度变化很大,则可能会发生clock skew。沿着较短互连行进的时钟将比沿着较长互连行进更快地到达其寄存器。 clock skew的另一个原因可能是时钟分配网络中互连延迟的差异。即使两条时钟传输路径的长度相同,它们也会由于诸如电阻、电容或电感耦合等寄生效应而经历不同的延迟。在图 4 的示例中,RC 寄生效应的任何差异都会导致寄存器 A 和 B 的时钟到达时间延迟不同。线路上延迟较大的时钟信号自然会比延迟较小的信号更晚到达其目的地. 设计具有相同延迟的互连可能是一项极其困难的任务。clock skew也可能是由时钟信号的逻辑路径延迟的差异引起的。例如,在包括时钟门控的设计中,时钟的传输路径中可能存在额外的门,每个门都具有自己的负载电容和传播延迟。如果不平衡,逻辑路径的差异会导致时钟传递时间不等。使用时钟分配网络最大限度地减少时clock skew随着时钟频率的增加,clock skew可能会成为一个更具挑战性的问题,因为随着时钟频率的提高,误差幅度会显著降低。为了最大限度地减少clock skew,复杂的同步电路采用类似于图 5 所示的时钟分配网络。这些通常也称为时钟树。时钟树中的每个反相器都会放大时钟信号以驱动时钟树的下一级。目标是让时钟信号同时到达所有寄存器输入。对于具有数百万甚至数十亿晶体管的超大型 IC,时钟分配网络可能会比图 4 的简单示例复杂得多。这些网络的创建通常由EDA软件自动处理。工程师输入目标频率、寄存器设置和保持时间限制以及最大时钟偏差等关键参数。然后,软件生成时钟分配网络以满足目标时序约束。clock skew是数字集成电路设计中需要考虑的重要课题。如果没有正确考虑,时钟偏差会对系统性能造成严重破坏,导致系统操作不当、数据丢失或成为系统时钟频率的限制因素。

https://www.allaboutcircuits.com/technical-articles/what-is-clock-skew-understanding-clock-skew-and-clock-distribution-networks/