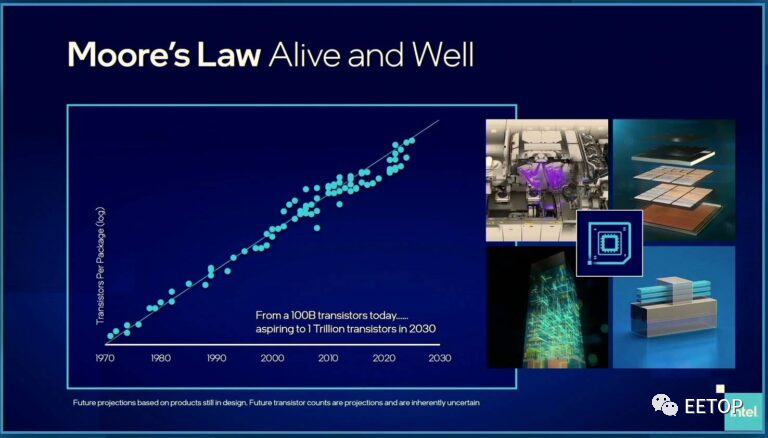

根据外媒报道,在上周的HotChips 34 大会上,英特尔CEO 帕特·基尔辛格(Pat Gelsinger)阐述了英特尔对未来的愿景,而这一愿景的基础在于结合多个小芯片设计的先进封装。这在业界来说并不是什么新鲜事,但却说明了英特尔对即将推出的以小芯片设计的代号Meteor Lake 系列CPU 的重视。而且,Pat Gelsinger 还说明了这基础如何影响未来整个半导体产业。Pat Gelsinger 表示,小芯片设计将先进封装将延续未来10 年摩尔定律的蓬勃发展。甚至,到2030 年之际,晶体管密度将增加10 倍,这将使得英特尔在芯片上发展到拥有1 万亿个晶体管。Pat Gelsinger 表示,小芯片加先进封装对半导体产业最大的变化是摆脱了晶圆厂只生产晶圆的观念。相反,他认为这项服务正在演变成为客户提供完整的「系统」。该系统包括提供晶圆以及多个小芯片、先进的封装,以及将它们连接在一起的软体。这样的做法称之为System on Package,简称SOP。Pat Gelsinger 解释,数据中心内的机架式服务器蔚为风尚,这就是依赖以SOP 为主所累积起来的发展模式,也就是当SOP 成为了先进系统后,未来就能看到整体的持续发展。

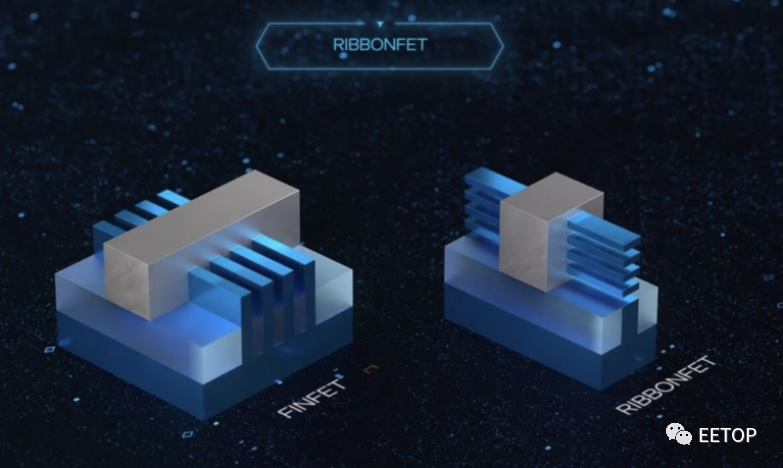

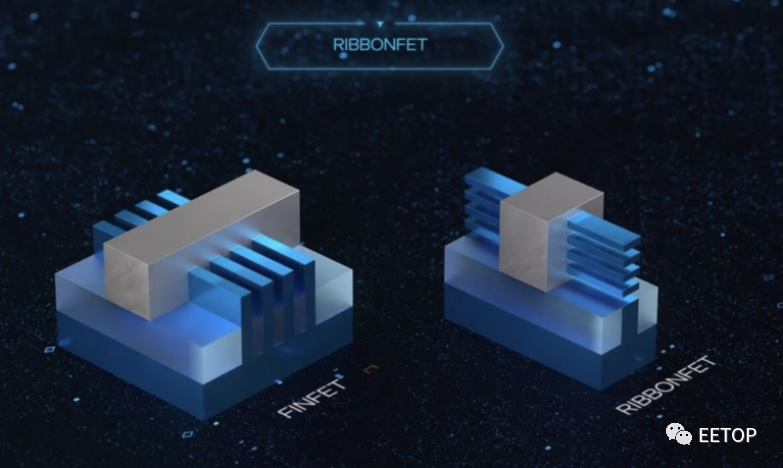

事实上,要达到这种改变,其中一部分涉及节点微缩以及芯片堆叠技术。英特尔之前已经讨论过,将在2024年将放弃FinFET 技术,转而使用环栅(GAA) RibbonFET技术,也就是将在其intel 20A 节点的解点开始采用新的技术。同时,还将以PowerVIA,也就是背面供电技术来支援。Pat Gelsinger 认为,这种制程以及封装技术的进步,将为半导体提供无限制的进步。「今天,一个芯片上大约有1,000 亿个晶体管。而在有了环栅(GAA) RibbonFET 技术之后,将会产生一个芯片新的基本晶体管结构,预计到达2030 年之际,将可以使得晶体管数量达到1 万亿个,而英特尔也会持续发展。」Pat Gelsinger 说道。

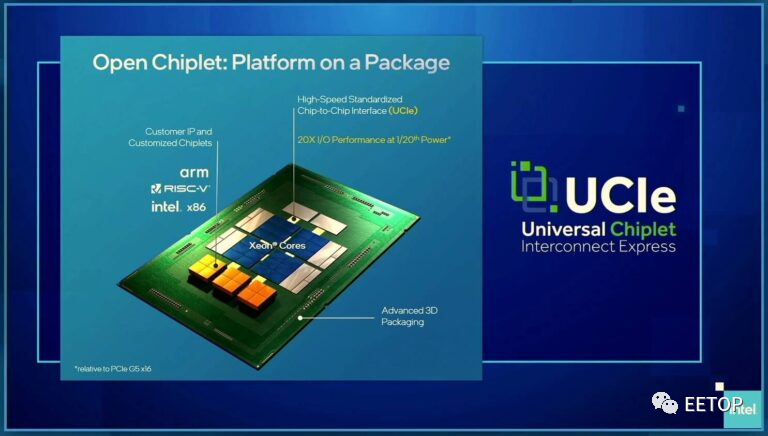

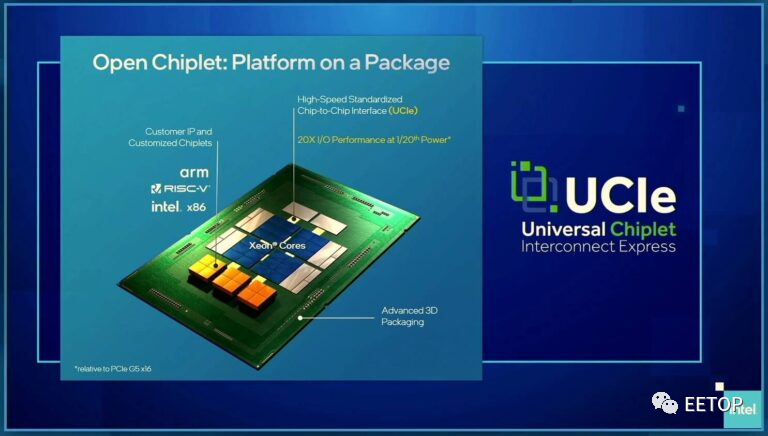

Pat Gelsinger 强调,下一代代号Meteor Lake 系列CPU采小芯片及先进封技术是一种未来。这代表着根据最有效的方式组合不同的小芯片,而每个小芯片依需求构建在不同的制程节点上。例如,Meteor Lake 系列CPU 将结合自己的代工厂和台积电的四个不同制程节点。它将在其22 纳米制程上构建基础中介层,并在Intel 4 (之前为7 纳米) 上构建CPU 小芯片。同时,台积电将采用的5 纳米和6 纳米制程来生产SoC、I/O 和GPU 等的小芯片。而从这些不同制程所生产出来的各个小芯片,英特尔再将其以先进封装技术整合连结再一起,最后生产出了Meteor Lake 系列CPU。报道进一步指出,随着芯片缩小未来变得不那么频繁,并且小芯片生产将会是其中的关键下,这些小芯片与元器件如何整合在一起将成为未来几年的关键技术。为此,Pat Gelsinger 还推荐了基于PCI Express 的通用小芯片连接器。这个由英特尔所主导,包括AMD 和高通等相关知名半导体厂商也参与的Universal Chiplet Interconnect Express (UCIe) 联盟所开发出来的标准,目的在标准化来自不同代工厂的小芯片的连结和协同工作。而这联盟未来值得关注的,就是苹果和英伟达两家厂商是不是也会加入。

不过,市场人士指出,这是否会成为英特尔的致胜战略还有待观察,但是应该很快就能看到答案。因为英特尔会议上确认代号Meteor Lake 系列CPU 将在2023年的推出。这将是该公司采小芯片设计的重要产品,具有来自两个不同代工厂所生产出来的小芯片,能不能受到市场青睐至关重要。另外,先前市场传出Meteor Lake 系列CPU 就是因为大小芯片设计的连结与协同运作设计有其问题,因此将延后推出的情况。不过,对此英特尔否认了传闻,并指出计划仍按照时程进行中。