摩尔定律(Moore′s Law)似乎面临极限,要处理器性能持续发展,小芯片堆叠技术(Chiplet)成了重要解决方式。工程师正用堆叠把平面发展处理器结构变成立体堆叠结构,透过整合储存、图像、电源管理等功能芯片,将小芯片堆叠整合,再藉技术连结,提升处理器效能,且也达处理器面积缩小目标。

摩尔定律代表处理器发展以每两年晶体管翻倍,但从纳米进入埃米时代,技术克服越来越困难。要延续处理器效能提升发展,小芯片堆叠技术生产的处理器就成为解决方案之一。荷兰半导体制造商艾司摩尔(ASML)已垄断全球先进制程曝光机市场,2021年法说会指出,要处理器效能与面积再发展,只靠制程微缩会面临瓶颈,必须堆叠架构才能达成。

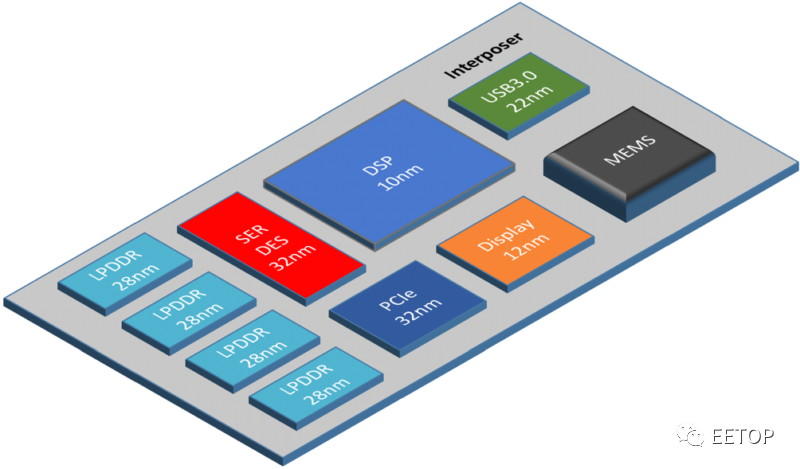

以前生产堆栈架构处理器并不容易,除了必须精准控制每个芯片制程,还要用技术连结芯片,就像两个单位必须有交通连结。现在这些问题都能通过先进工艺和封装技术解决,将分隔两地的芯片以技术整合至处理器,再以先进封装连结芯片,不但减少数据传输瓶颈,甚至提高运作效率,让处理器效能大大提升。International Business 前高层指出,这就像是将两地单位集中到一栋楼,减少三分之一电路空间,也让沟通像搭电梯更快速。

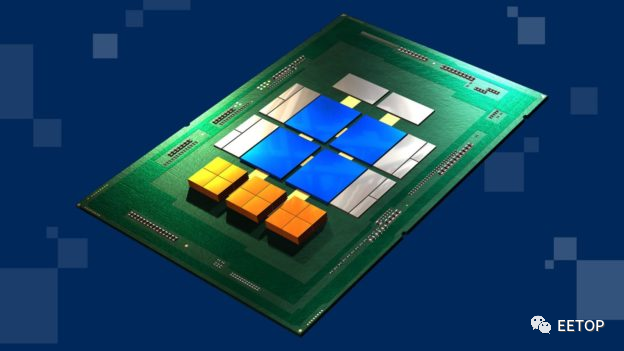

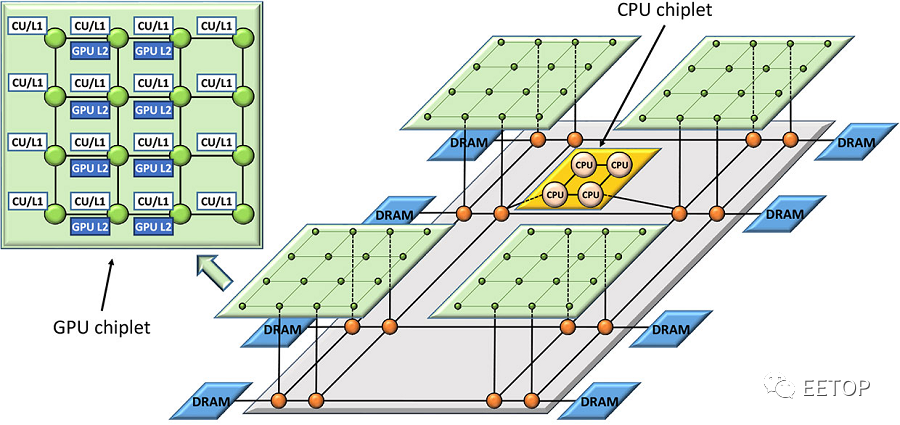

建构处理器垂直架构核心,就在处理器各功能小芯片。每个小芯片透过堆叠整合至处理器,再以硅穿孔技术连结,完全封装在处理器内,不需外部电路连结。小芯片沟通更快速,也能达到透过制程微缩生产处理器的运作效能。以英特尔 Ponte Vecchio 图形处理器来说,每个图形处理器都由 63 个小芯片连结。小芯片总堆叠面积为3,100平方公釐,含1,000亿个晶体管。相比笔电核心处理器面积不到150平方毫米,约Ponte Vecchio图形处理器堆叠面积5%,却约15亿个晶体管,仅Ponte Vecchio图形处理器1.5%,运算效能也由此可知。

除了运作效能,先进制程芯片生产成本高得令人咋舌,未来2纳米制程芯片设计成本将超过28纳米14倍。但小芯片堆叠处理器因每个小芯片都能以需要制程生产,不需要耗资高成本,即便多数桌机与笔电处理器都还没以这方式生产,英特尔仍表示,堆叠大小芯片给予效率更好、成本更省的生产方式。英特尔竞争对手AMD已是小芯片堆叠技术领先者,透过处理器外加上存储器,使小芯片堆叠技术处理器,运算效能高于传统处理器。

EDA 大厂ANSYS指出,小芯片堆栈市场需求过去仅个位数,现在增加20倍之多,甚至英特尔与AMD是竞争对手的半导体大厂也加入Universal Chiplet InterconnectExpress (UCIe)联盟,一同与Arm、台积电、三星等推动标准与技术。越来越多科技大厂对小芯片堆叠技术有浓厚兴趣,陆续加入自研芯片以发展业务,有谷歌、亚马逊、微软、特斯拉等。未来可期待从云端服务器到智能手机、游戏主机与自驾车等都能看到小芯片堆栈架构为主的处理器。

小芯片堆叠处理器预计超越传统制程处理器,专家提醒,小芯片堆叠处理器除了提高效能,因不需接电路,甚至是生产软性终端设备的利器,且有团队正在研究。尽管小芯片堆叠处理器仍有许多困难待克服,但运算能量很难不让人注意,摩尔定律延续下去也可能得靠它。小芯片堆叠处理器发展,还只是开始。