美光声称通过一种新工艺打破了1z DRAM节点的天花板,该工艺将存储密度提高了40%!

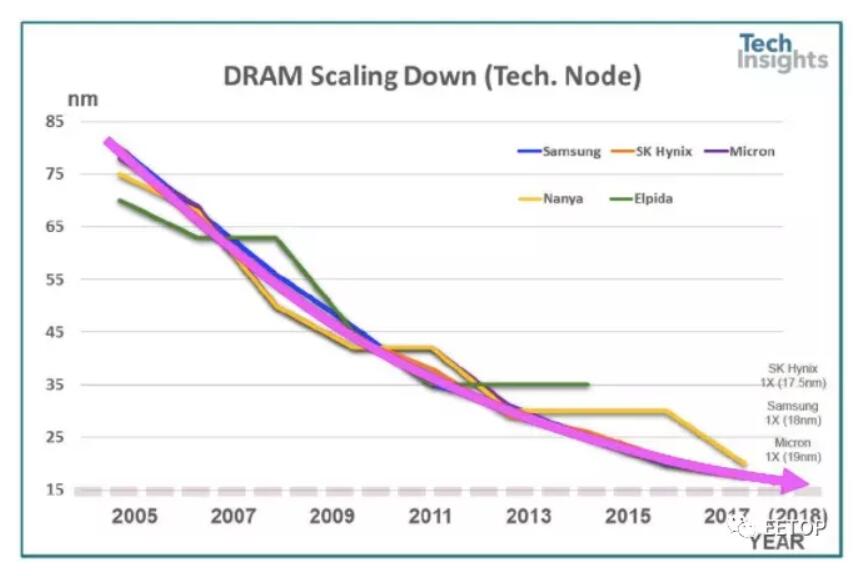

DRAM的缩小速度明显慢于许多其他芯片。虽然微处理器的工艺已经到了5nm节点,但DRAM仍然停留在20nm和10nm节点之间,并且从2016年左右开始就一直如此。理论上,10nm是DRAM的极限。

正因为如此,制造商们创造了一种新的工艺节点命名方案,它指的是存储单元阵列中有效区域间距的一半的尺寸。惯例如下。

1x nm:19nm–17nm(Gen1)

1y nm:16nm–14nm(第2代)

目前,厂商只达到了1z的 "节点"。不过现在,美光科技已经成为第一家将下一个最小维度的DRAM--1α推向市场的公司。

电容器纵横比和DRAM缩放

出于多种原因,提高DRAM工艺制程并不如像微处理器那么简单。

单个DRAM单元由传输晶体管和存储电容器组成。

原因之一涉及DRAM的本质。它需要一个存储电容器来保存数值。由于设备的电容大小直接与其物理尺寸有关,因此横向缩小电容器会降低其容量。电容器不仅不再能够容纳可测量的电荷,而且还会更快地泄漏电荷,从而需要更多的动态刷新,这样反而提高了功耗。

一些行业供应商认为,要充分克服这一挑战,必须大力发展新材料。

制造的挑战

使DRAM进一步缩放的另一个限制因素涉及制造方面的挑战。

硅加工通常依靠光刻技术将详细的图案蚀刻到半导体硅片上。DRAM单元的光刻设计要求,特别是电容器的复杂性,使得制造工艺更加困难。

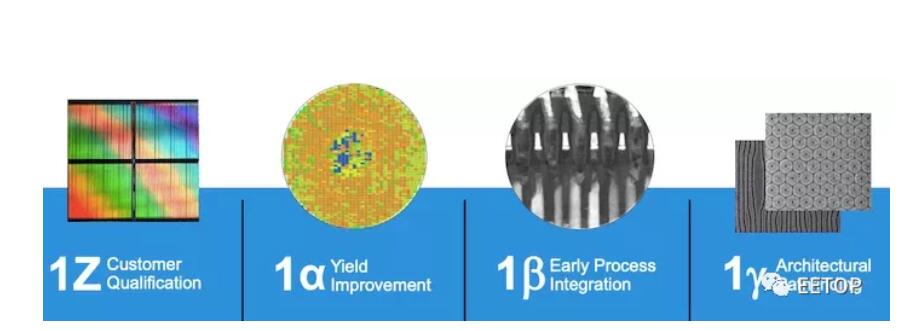

美光DRAM路线图

随着特征的缩小,光刻受到瑞利准则(Rayleigh)的限制。该标准指出,不可能使用光刻来蚀刻小于所用光波长的大约一半的特征。这意味着,当特征被蚀刻得足够小时,使用常规技术几乎不可能创建足够精确的DRAM单元。

一些挑战包括以良好的对齐方式设计电容孔,以及为可预测的行为创造具有精确长宽比的电容。

内存密度提高40%

考虑到美光的新型1αDRAM与先前的1z DRAM节点相比,其存储密度提高了40%,因此这一消息对于存储空间意义重大。美光还声称,与1z移动DRAM相比,这项新技术可节省多达15%的功耗。

据该公司介绍,1α节点将在今年应用在其DRAM产品系列中,以支持目前所有使用DRAM的环境。

不采用EUV,美光推出新的内存处理节点

尽管这些挑战使进度惊人地缓慢,但一些供应商仍在进步。美光公司是第一家近期取得重大进展的公司,成为第一家将1α工艺节点投入量产的公司。

与某些寻求极端紫外线(EUV)光刻技术作为解决方案的公司不同,美光通过“多重图案化”实现了缩小尺寸。该技术背后的思想是通过添加非光刻步骤以从单个较大的特征中创建多个小的特征来提高分辨率。

美光的接下来的三个DRAM节点将继续使用深紫外线(DUV)光刻技术,但该公司现在正在考虑将EUV用于其1