10亿个晶体管/mm² !1nm节点可以这样做

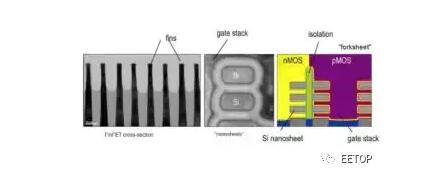

2020-12-29 12:06:56 EETOP编译自semiwiki提议的对纳米片拓扑的扩展采用“forksheet”,如下图所示。

forksheet研发的目标是消除nFET到pFET器件的间距规则(用于公共栅极输入连接),用薄氧化物隔离两组纳米板。晶体管密度获得这种引人注目的增益的代价是——栅极再次在三个侧面上包围了沟道体积–“ FinFET侧面翻转”是forksheet的一个常见的相似之处。

尽管后FinFET节点的大批量制造(HVM)的日期有些不确定,但是可以预料,这些不断发展的纳米片/forksheet拓扑将在2024-25年间出现。

目前正在积极进行工艺开发和设备研究,以寻找无数纳米片的替代品。假设“纳米”设备拓扑将至少用于两个进程节点,如果任何新设备要在2028-30年达到HVM,现在就需要积极地进行研究。

在最近的IEDM会议上,Synopsys展示了他们在此时间范围内针对“ 1nm”节点的领先器件替代产品之一的预测和设计技术协同优化(DTCO)评估结果。本文总结了他们演讲的重点。

1nm 节点

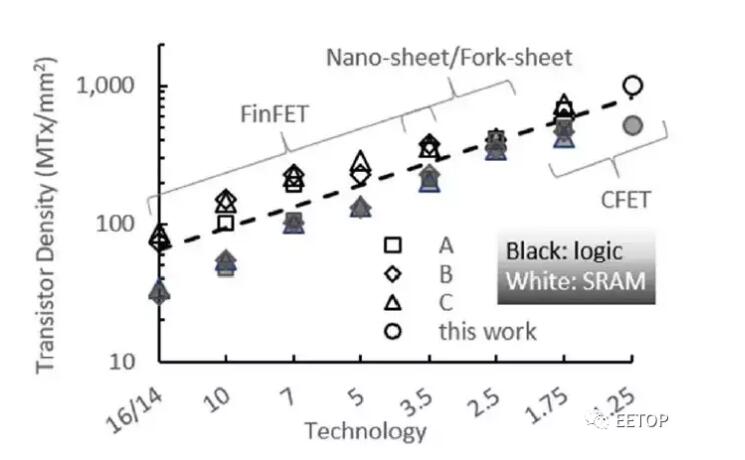

下图描述了最近几个工艺节点的晶体管密度的直线趋势。(此图是Synopsys与IC Knowledge,Inc.合作的一部分。)

关于这张图需要注意的几点:

x轴上的节点名称代表了从14nm节点的简单过渡,每个连续的数据点都由0.7X摩尔定律线性乘数定义(为了便于讨论,如果DTCO工艺发展的目标确实是保持在这条曲线上,那么使用0.7X的命名是合适的。)

每个节点上的密度数据点代表来自多个代工厂的指标

逻辑密度通常与代工技术常用的基础库单元实现有关。例如,一个2输入NAND单元的面积反映了单元中4个器件的使用情况。

cell邻接隔离间隔(“扩散中断”与单元之间的虚设栅极捆绑在一起)

另一个关键的单元维度是一个(可扫描的)数据触发器的面积。上面的晶体管密度计算对每个逻辑数据点使用了NAND和FF单元的逻辑混合。

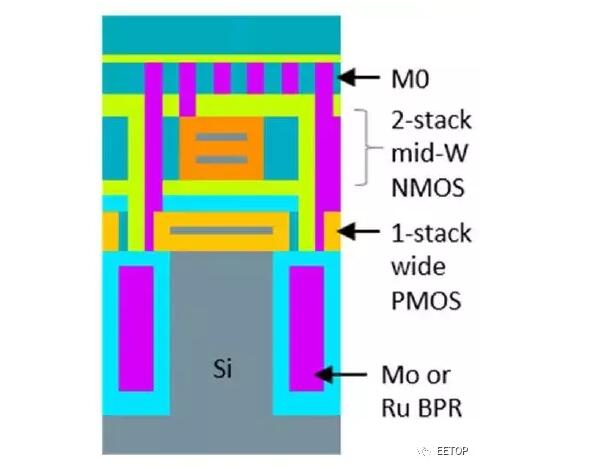

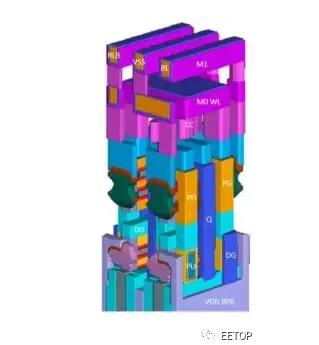

特别值得注意的是,在Synopsys对1nm节点的预测中使用的器件拓扑结构的假设。目前正在积极研究,以便在与该节点一致的时间范围内评估几种非硅场效应器件类型--例如,二维半导体材料(MoS2)和一维碳纳米管。为了保持在晶体管密度曲线上的目标,Synopsys TCAD团队采用了DTCO工艺定义来实现3D“互补FET”。下图展示了CFET的横截面。

CFET技术的一个吸引人的特征是与纳米片拓扑结构的相似性,后者将在1nm节点的时间范围内具有多年的制造经验。CFET方法的新颖之处在于pFET和nFET纳米片的垂直放置。

CFET拓扑利用了典型的CMOS逻辑应用,其中将公共输入信号施加到nFET和pFET器件的栅极。(稍后将讨论具有仅nFET字线传输门的6T SRAM位单元的独特情况。)上图显示了pFET纳米片如何直接位于nFET纳米片下方。在图中,存在两个nFET纳米片,比pFET窄,这主要是由于需要空间来接触pFET源极和漏极节点,因此nFET的宽度减小了。并联的两个nFET将提供与pFET相当的驱动强度。(CFET中的SRAM位单元设计采用了不同的策略。)还显示了有源栅极上的M0接触(COAG)拓扑结构,扩展了这种最新的工艺增强功能。

CFET器件的处理需要特别注意pFET和nFET的形成。用于pFET源/漏节点的SiGe的外延生长用于在沟道中引入压缩应变,以提高空穴迁移率。然后执行pFET栅极氧化物和金属栅极沉积。随后,nFET源极/漏极节点的外延Si生长,随后的栅极氧化物和金属栅极沉积必须遵守现有pFET器件施加的材料化学约束。

埋入式电源轨(Power rails)

请注意,对于1nm节点的假设是,本地VDD和GND分布将由“埋入电轨”(BPR)提供,它们位于基板中的纳米片下方。结果,既需要“浅”(器件)通孔,又需要“深”(BPR)通孔。因此,BPR和过孔的金属成分是关键的工艺优化,以降低寄生接触电阻。(主要)金属必须具有低电阻率,并以极薄的势垒和衬里材料沉积在沟槽中。

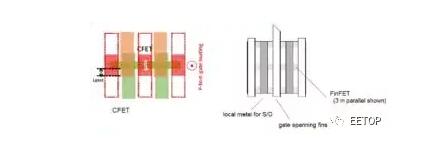

说到寄生,下面的(简化)布局图突出了CFET拓扑的独特优势。CFET器件的三维方向消除了单独的nFET和pFET区域之间的栅极穿越。而且,与FinFET器件布局相比,栅极到源极/漏极局部金属化层的并行运行长度显着减少。(图中显示了经过纳米片的较小的栅极长度扩展。)结果,使用CFET极大地改善了器件的寄生Rgate电阻和Cgs / Cgd电容。

CFET SRAM设计

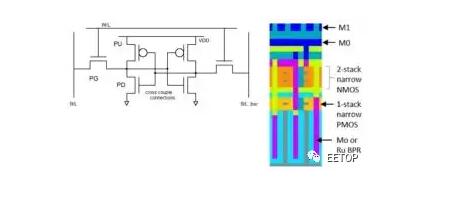

在CFET工艺中实现6T SRAM位单元会引入一些权衡。Synopsys DTCO团队选择了独特的设计特性,如下图所示。

在工艺开发的早期,DTCO分析利用TCAD模拟工具,来表示材料的光刻图版、材料沉积和(选择性)蚀刻轮廓。这项早期的优化工作提供了对所需的工艺窗口、预期的材料尺寸和电学特性的见解,包括优化自由载流子迁移率的沟道应变。

后续的寄生提取,与设备模型合并,为新工艺提供初步的功率/性能度量,并结合设备布局区域进行全面的PPA评估。下图提供了上述SRAM位单元的DTCO的可视化分析。

总结

在IEDM上,Synopsys TCAD团队提供了对 "1nm "节点特性的窥探,该节点基于CFET器件拓扑结构,在两个nFET纳米片下面有一个pFET纳米片。还假设了埋入式电源轨。光刻假设是基于利用(高数值孔径)EUV--例如,39nm CPP(带COAG)和19nmM0金属间距。对于相对的PU:PD:PG驱动强度和内部交叉耦合互连层,都采用了独特的SRAM位单元设计方法。

这种DTCO分析的结果表明,1nm CFET节点可能确实能够保持激进的晶体管密度,接近10亿个晶体管/平方毫米。