自20世纪40年代末至50年代初发明晶体管以来,它一直是电子器件中最主要的元件,它使现代技术得到了极大的提高。摩尔定律和Dennard缩放已经描述了改进现代IC设计中的晶体管的功能尺寸和性能的需要;也就是说,每24个月就需要将某个芯片中的晶体管数量增加一倍。

由于这种改进,早期的晶体管电路(几毫米)与现代的晶体管电路(跨度只有几纳米)相比,在性能、工作点和内在特性上都有明显的差异。

在这篇文章中,我们将讨论理想的MOS晶体管分析模型和由于MOS晶体管的功能尺寸和设计的不断改进而产生的非理想性。另外,我们将讨论在实际实现之前,介绍了在MOS晶体管中引入非理想(SNI)的设计方法,以正确模拟仿真中的VLSI电路。

背景资料:源极和漏极

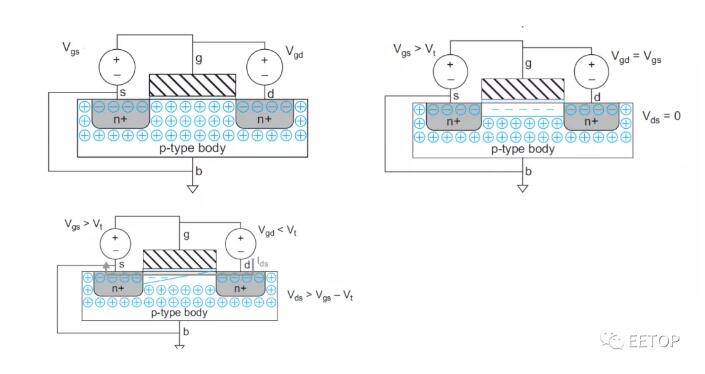

考虑图1中的基本晶体管图。当没有电压施加到栅极(g)上时,称该晶体管处于OFF状态。

如果施加较小的栅极电压(Vgs

在导通状态下,漏极电流(Ids)与漏极电压(Vds)线性增加,直到(Vds = Vgs = Vdsat),之后漏极电流保持恒定。如果漏极电压进一步增加到该值(Vds > Vdsat),此时晶体管可能会产生其最大电流限制,该晶体管将处于饱和状态。举例来说,如果你不停地消耗大量的食物,根据你的体力限制,你能做的工作是有最大限度的,也就是说,你消耗再多的食物都被认为是浪费了。同样,晶体管也受到它的物理限制,如它的特征尺寸(W和L)和它的掺杂水平(它所包含的杂质数量)的限制。

因此,此图示称为长沟道模型,其栅极长度为(L)宽度为(W)的晶体管的漏源电流为 :

动机

IC设计人员试图改变晶体管的W/L,以便在芯片上装入更多的元件。他们尝试将晶体管塞满芯片的次数越多,面对晶体管的物理限制就越多。

所以,多年来,随着晶体管尺寸从微米到纳米技术的发展,上面所说的大多数假设并不能完美地模拟真实晶体管的工作。例如,当说晶体管处于关闭状态时,电流被假定为零,但在实际意义上,晶体管的两端之间存在亚阈值电流泄漏,这些电流在理想状态下可以忽略不计,在纳安培(nA)的数量级,但当乘以器件中数百万-数十亿个晶体管时,这些电流是非常大的。

例如,当你关闭手机后,你想让你的电池保持在关机时的水平,所以泄漏电流是设计师在模拟设计时必须处理的问题。

其次,理想情况下晶体管在饱和模式下保持最大电流恒定,但在实际晶体管中,电流以较慢的速度增长,这就破坏了提供恒定电流的目的。

因此,在本节中,我们将介绍导致这些非理想行为的每个机制,以及设计者如何在设计流程中正确地模拟晶体管。

速度饱和会导致在高VDS时较低的I DS。由于较高的电压导致沿通道的电场强度较高,这会导致载流子更频繁地发生碰撞,从而导致载流子的迁移率下降。

载体也有物理限制,因此它只能维持一定的最大平均速度,这称为速度饱和。(Chen,etal。,1997)和(Chen,Hu,Fang,Lin,&Wollesen,1997)给出了与这种情况相匹配的通用模型,其中迁移率(µ)替换为有效迁移率(µeff)。

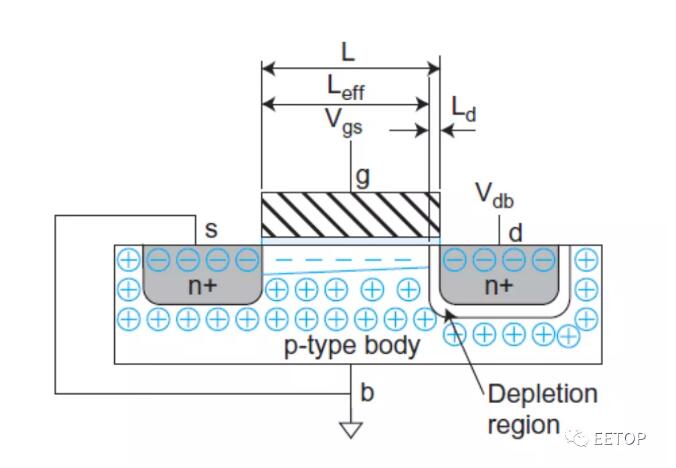

在理想的晶体管中,当晶体管处于饱和模式时IDs独立于 VDs,使晶体管成为恒定电流源。但实际上,Vds(漏极-源极电压)沿沟道壁形成耗尽层(Ld),这使有效沟道长度小于实际沟道长度,从而使有效长度(Leff = L) – Ld)。

因此,随着Vds的增加,Leff变得相对较短,从而导致横向场强度降低。由于电场强度(E)与通道长度成正比。这种降低的场强将I ds的可变性推回到线性区域,这使I ds随着V ds的饱和而增加。

在这种情况下,可以通过将I ds乘以依赖于早期电压VA的因数来更好地建模, 如(Gray,Hurst,Lewis,&Meyer,2001)中所述。

理想情况下,阈值电压(Vt)被认为是恒定的,但实际上,它随体电压(源体电压,Vsb)、漏极电压甚至通道长度而变化。

首先,从图2中的晶体管,当应用Vsb时,它增加了晶体管打开所需的阈值电压(Vt)。记住这一点,Vt可以被重新建模为

更多信息见(Tsividis,1999)。

其次,沿通道产生电场的漏极电压会引起漏极诱导屏障降低(DIBL),从而导致阈值电压以DIBL系数表示的因子降低。

通常情况下,Vt随着通道长度的增加而增加,但当施加Vds时,由于耗尽区的存在,通道长度会减少,因此,会造成所谓的Vsb滚落(减少)。

当晶体管截止时,假定漏-源电流为零。实际上,由于亚阈值导通和结泄漏,它们会泄漏少量电流。

对于亚阈值泄漏,假定当V gs

对于结泄漏,我们观察到该晶体管是扩散和衬底/阱之间的基本PN / NP结二极管。当晶体管处于截止状态时,源极-栅极结二极管被反向偏置。但是,反向偏置的二极管仍会传导经典二极管方程式给出的少量电流:

温度也是一个巨大的非理想性机制,因为它主要影响到迄今为止讨论的其他非理想性。例如,亚阈值泄漏随温度增加。阈值电压(Vt)也会随着温度的升高而降低,这使其易于受到DIBL和亚阈值导通的影响。一般来说,它更适合在低温下工作,因为它能显著降低速度饱和和迁移率降低。

Layout设计人员通常绘制具有一定沟道长度(Ldrawn)和宽度(Wdrawn)的晶体管。但实际的栅极/沟道长度尺寸可能会因制造工艺的不同而有所偏离。这将导致晶体管的尺寸小于/多于预期的尺寸,因此它将影响阈值电压和有效沟道长度和速度饱和效应,这可能会导致一些非理想性,如前文所述。这种非理想性的模型如下所示;LD 和WD取决于制造过程。