互连可能是射频 EMI 信号的主要载体。一个主要的“RF”违规者将是属于全球政府定义的分配无线电频段之一的任何信号。带高频射频信号的导体会产生谐波电场和磁场,可能会导致邻近的互连网接收到该信号的复制品。开关谐波,由开关或通过电源转换器产生,也将产生高辐射和传导的EMI,出现在开关电源转换器的输出端。此外,射频EMI可以从开关谐波或甚至数字信号的切换状态中发出。这种类型的噪声可能在附近的互连和电缆上以电容或电感诱导脉冲的形式出现,而不是以随机噪声的形式出现。最后,来自外部源的RF EMI 可能来自静电放电 (ESD),它可以将宽带脉冲传导到您的系统设计中,甚至通过电源输入作为传导 EMI 注入。

电磁屏蔽将通过使用由导电或磁性材料构成的各种屏障来阻挡电磁场,从而减少电磁场进入射频设计。屏蔽通常应用于外壳,以将电气/电子设备与其嘈杂的环境隔离开来。此外,屏蔽层应用于电缆,以将电线与电缆穿过的环境隔离开来。屏蔽射频电磁辐射的电磁屏蔽称为 射频屏蔽。屏蔽也可以减少无线电波、电磁场和静电场耦合到设计人员的电路中。用于阻挡静电场的导电外壳称为法拉第笼。EMI减少量很大程度上取决于所使用的材料、其厚度、屏蔽体积的大小以及感兴趣场的频率。其他因素包括屏蔽中任何孔对入射电磁场的大小、形状和方向。静电屏蔽与低速、低功率密度的电路相比,高速、高功率密度的电子电路对静电(称为静电放电或ESD)的敏感性/敏感性要高得多。对你的设计来说,外部的静电可能会导致你的电路设计出现灾难性的故障。为帮助防止任何高电平外部电场损坏您的设计,静电屏蔽的使用将创建一个屏障以有效隔离您的电路。静电屏蔽可能包括静电屏蔽中允许的小孔,因为空腔内的电场对这种开口来说相对较小。这种类型的屏蔽通风性能也会更好一些。这种开孔有时也用于电缆或电线的束缚,以及作为内部电路的接入点。

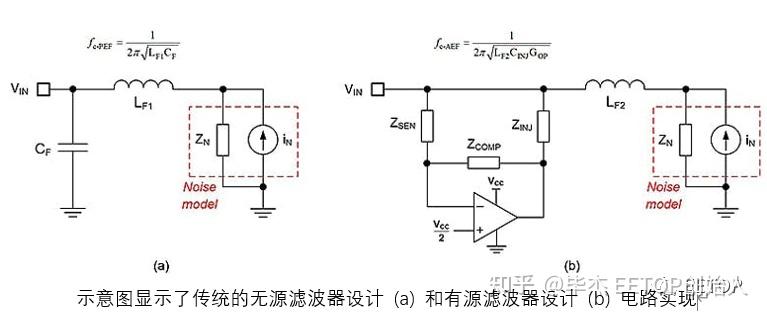

无源滤波是一种通过使用电感器和电容器在EMI 电流路径中产生阻抗失配来减少电子电路传导发射的方法。有源滤波还可用于感测输入总线上的电压并产生相反相位的电流,该电流将直接抵消开关级产生的EMI 电流。该图展示了一个简化的无源和有源滤波器电路,其中i N是电流源,Z N是来自 DC-DC 稳压器的差模噪声的诺顿等效电路阻抗。

图中所示的滤波器设计可用于汽车应用。有源滤波器使用电压感应和电流注入,这将实现低EMI 特征,从而减少占位面积和体积,并提高解决方案成本。使用同步降压控制器的有源EMI 滤波器 (AEF) 电路的集成有助于解决 DC-DC 稳压器应用中低 EMI 和高功率密度之间的权衡。

射频屏蔽是阻止可能导致射频干扰(RFI) 的射频电磁信号 EMI 的做法。RFI 会严重降低电子电路的性能,甚至会使适当的电路功能完全失效。射频屏蔽是一种保护电路设计者的设备和设备免受射频干扰带来的有害影响的手段。它可以通过在电磁场的潜在来源以及受干扰者周围安装屏障来实现。对射频干扰的滤波是通过电路在电子系统内实现的,它只允许想要的信号通过,而拒绝不想要的射频干扰信号。