据Sam Zeloof介绍,为了打造自己的芯片工厂,自 2016 年 10 月以来,就一直在积累相关设备。2017年家庭芯片工厂初步建成。

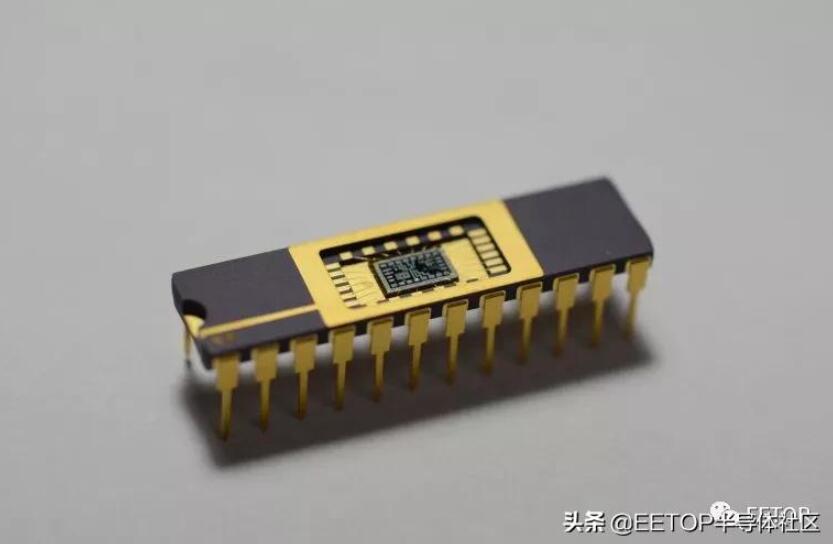

随后Sam Zeloof开始了集成电路的设计与制造研究,先从FET器件做起,然后在2018年高三器件做出了第一个第一个自制集成电路—Z1放大器。Z1 有 6 个晶体管,是开发所有工艺和设备的绝佳测试芯片。

一些更多的认识与改进。在此基础上,Sam 做出了Z2芯片,该芯片 有 100 个晶体管,采用 10µm多晶硅栅极工艺——与英特尔的第一款处理器技术相同。Sam介绍,该芯片是一个简单的 10×10 晶体管阵列,用于测试、表征和调整过程,但这是向更先进的 DIY 计算机芯片迈出的一大步。Intel 4004 有 2,200 个晶体管,Sam表示已经在同一块硅片上制造出 1,200 个晶体管。

在作者的博客上(http://sam.zeloof.xyz)详细介绍了家庭芯片工厂诸多细节,以及各款芯片的设计制造过程。

今天,我们为大家分享一下作者在2018年高三期间设计和制作第一款集成电路的详细过程及方法。

前言

我很高兴地宣布第一个自制集成电路的细节,并分享这个项目在过去一年里带给我的旅程。我希望我的成功能激励他人并帮助开启家用芯片制造的革命。当我开始这个项目时,我不知道自己进入了什么领域,但最终我在物理、化学、光学、电子学和许多其他领域学到的东西比我想象的要多。

我展示了第一个自制的(光刻制造的)集成电路——“Z1”PMOS 双差分放大器芯片。我说“光刻制造”是因为 JeriEllsworth 制造了第一个晶体管和逻辑门(用导电环氧树脂精心手工接线)并向世界展示了这是可能的。受到她工作的启发,我展示了由可扩展的行业标准光刻工艺制成的 IC。不用说,这是我之前复制 Jeri 的 FET 制造工作的逻辑升级。

我介绍的第一个自制(光刻制造的)集成电路是"Z1"PMOS双差分放大器芯片。在此之前Jeri Ellsworth自制过晶体管和逻辑门,门(用导电环氧树脂精心手工布线),并向世界展示了这是可能的。受她工作的启发,我展示了由可扩展的、符合工业标准的光刻工艺制造的集成电路。

设计

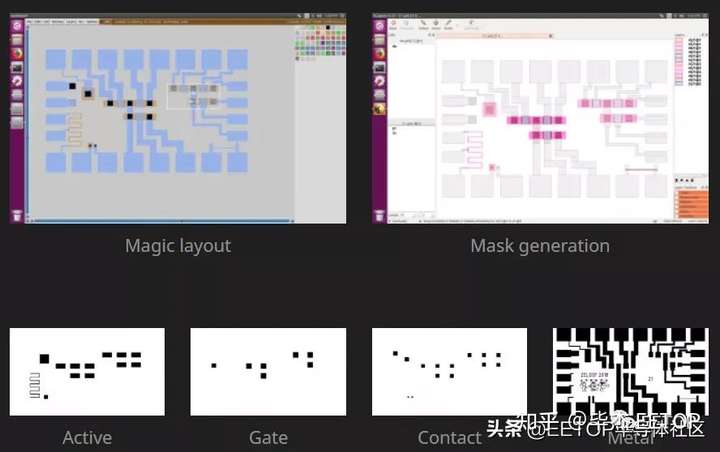

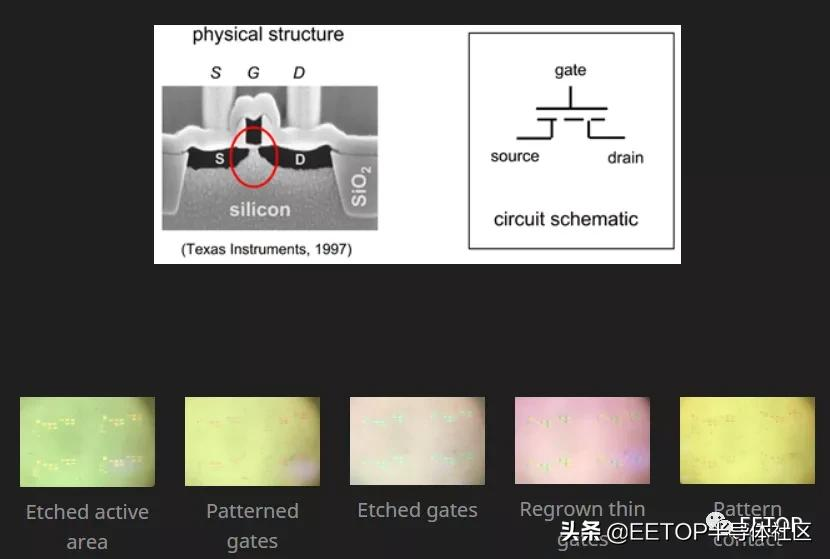

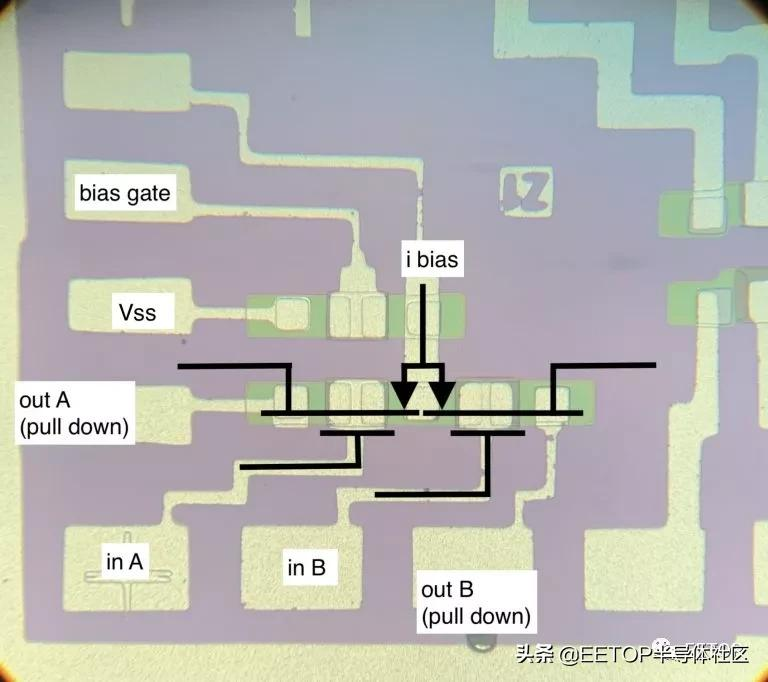

我设计Z1放大器是为了寻找一个简单的芯片来测试和调整我的工艺。在MagicVLSI中完成了4个掩模的PMOS工艺(有源/掺杂区、栅极氧化物、接触窗口和顶部金属)的布局。就避免离子污染而言,PMOS 比 NMOS 更具优势,这使其能够在车库中制造。掩模被设计成16:9的长宽比,便于投影光刻。

最初的芯片栅极尺寸约为 175μm(目前FET 栅极长度(特征尺寸)已减小到 <5μm,(1975 技术水平),从而提高了器件性能。),每个放大器部分(中间和右侧)包含 3 个晶体管(2 个用于长尾差分对,一个用作电流源/负载电阻器),这意味着 IC 上总共有 6 个 FET。IC 的左侧部分包含电阻器、电容器、二极管和其他用于表征制造过程的测试功能。差分对的每个节点都连接到引线框架上的一个单独引脚,因此可以对其进行分析,并可以根据需要添加外部偏置。

功能图

制造

制造这种芯片需要66个独立的制造步骤,整个过程大约需要12个小时。制程良率可高达80%。

家用芯片制造化学工作台如下图所示,基本上包括制造 IC 所需的一切,除了真空室和光刻设备。

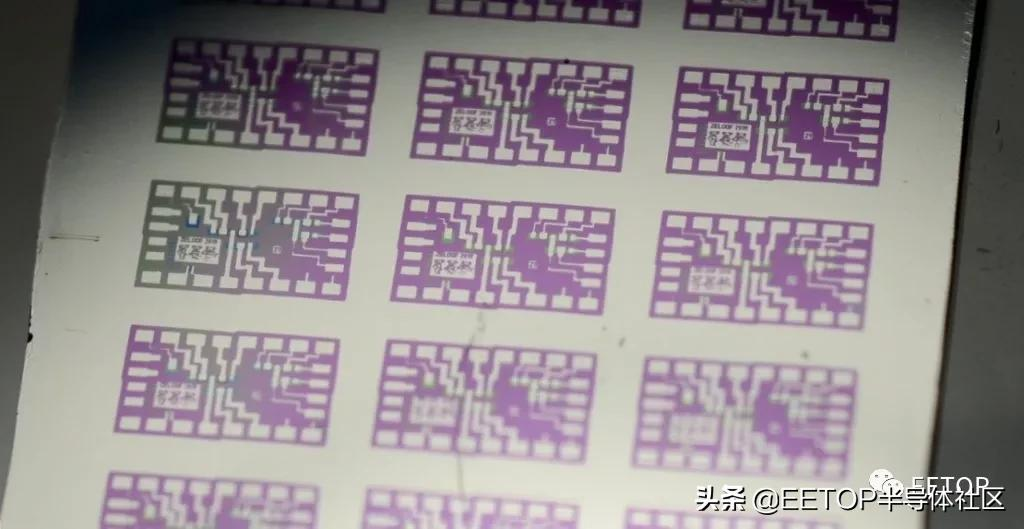

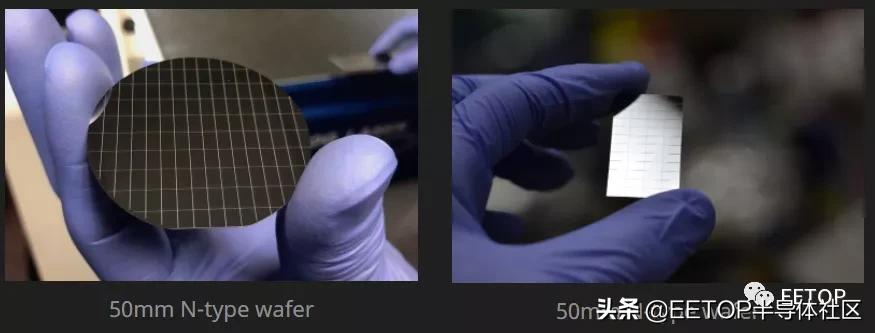

用Epilog光纤激光器将体电阻率为1到10Ω-cm(厚度为325µm时为30.8到308Ω/sq)的硅片划成5.08x 3.175mm的裸片(约16mm^2的面积)。在激光刻划之前,可以在晶片上旋涂溶于水或光刻胶中的聚乙烯醇,以“捕捉”激光烧蚀碎片,然后在加工前将薄膜在溶剂中去除。选择此芯片尺寸以适合京瓷 24 针 DIP 载体。

原生氧化物被快速稀释的HF浸泡剥离,然后在Piranha溶液(H2SO4:H2O2)、RCA1(H2O:NH3:H2O2)、RCA2(H2O:HCL:H2O2)中广泛清洗,然后再进行一次稀释的HF浸泡。这些清洗浸渍大多为10分钟,可以通过提高到~40ºC来促进。

在水蒸气环境中(湿式氧化),现场的氧化物被热增长到5000-8000Å的厚度。人们可以考虑在此步骤中把去离子水与百分之几的盐酸混合。氯化物原子有助于获取和固定离子污染物,据说还能使生长率提高5-7%。再加上我正在制造PMOS器件而不是NMOS,这些都给污染控制带来了巨大的优势,并允许在车库里制造出性能良好的器件。

氧化后的晶圆已准备好用于有源/掺杂(P 型)区域的图案化。正性光刻胶(用于 SiO2 图案化的AZ MiR 701和 用于铝层的AZ 4210)以大约 3000rpm 的速度旋转,产生约1.5μm 的 AZ MiR 701 或 3.5μm 的 AZ 4210 薄膜,该薄膜在热板上在 90C 下软烘烤.

光刻工艺细节

有源区掩模用我的Mark IV 无掩模光刻步进机在 365nm UV 下曝光, 图案在 TMAH 或 KOH 溶液中显影,具体取决于抗蚀剂。

在接下来的HF蚀刻步骤中,将蚀刻图案转移到氧化层,并为掺杂打开裸硅表面的窗口,然后将抗蚀图案烤硬,并使用一些其他技巧来确保良好的抗蚀附着力和化学稳定性。这些区域后来成为fet的源/漏。

然后通过固体或液体源进行掺杂。固体源是氮化硼圆盘,放置在管式炉中距离晶片附近 (<2mm)。或者,旋涂液体源可以由磷酸或硼酸在水或溶剂中制备,并在标准的预沉积/HF 浸渍/推进/脱釉工艺中进行掺杂。我在亚马逊上获得了纯磷酸,从蟑螂和蚂蚁药那里获得了硼酸。由于这里 PMOS 的起始晶片是 N 型,我正在为源极/漏极区进行硼的P 扩散,并针对 100 到 250 Ω/sq 的扩散区中的薄层电阻。

然后对栅氧化层和接触层重复上述构图步骤两次。栅极氧化物必须比场氧化物薄得多(<~750Å),因此源极/漏极之间的区域被蚀刻掉,并且在那里生长更薄的氧化物。然后,由于整个晶片在掺杂步骤中已被氧化,因此必须蚀刻金属层的接触窗以与源/漏掺杂区连接。

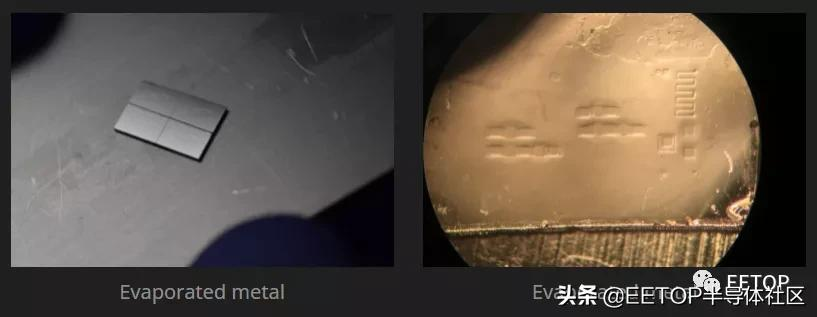

现在,所有晶体管都已形成并准备好互连并断开到引线框架。一层铝(400-500nm)被溅射或热蒸发到晶片上。另一种方法是使用剥离工艺,其中首先图案化光刻胶,然后沉积金属。为了支持引线键合,该金属层做得更厚(对于 Au 线楔键合大约为 2.5µm。)对于热蒸发膜,这些膜的测量体电阻率约为 5.4e-6 Ω-cm,是理想值 2.7e- 的两倍在 20ºC 时,Al为 6 Ω-cm。在真空沉积过程中将氧气和其他气体掺入铝膜可能是造成这种差异的原因。

然后用光刻法对金属层进行图案化,并在热磷酸 (50ºC) 中蚀刻,以产生完整的 IC。测试前的最后一步是目视检查和对铝进行高温退火以创建欧姆连接。

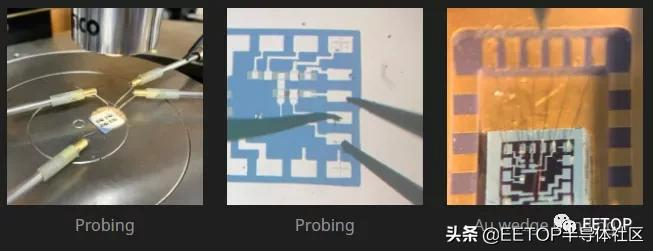

2018年时我还没有焊线机,所以当时我的测试仅限于用锋利的镊子手动探测晶圆或使用倒装芯片板(难以对齐)将其连接到曲线跟踪器。还对差分放大器进行了经验在线测试以验证操作。

二极管IV曲线

PMOS Id / Vds 曲线

正如您在上面的 PMOS FET Id 与 Vds 曲线中所见,芯片之间存在大量差异,同一天制造的器件可能具有截然不同的特性。以-1V Vgs 增量进行 5 条迹线需要大约 -8V 的体/衬底偏置来克服固定电荷(栅极下捕获的正杂质离子)和栅极区域中的晶格缺陷,并产生预期的图形。

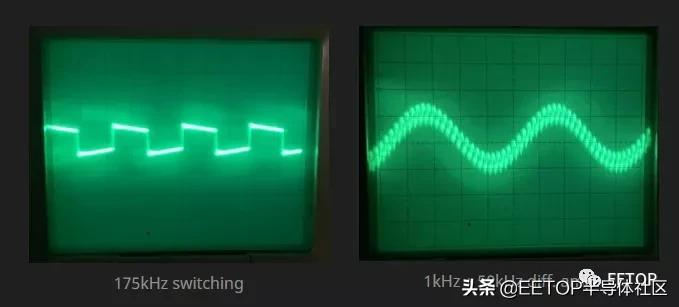

该芯片还可以连接为 3 级环形振荡器,这是对新 IC 制造工艺的经典测试:

显示 3 个阶段的自然频率约为 5kHz,主要受到光刻对准限制导致的栅极到源极电容过多的限制。

铝/硅结的电气特性也得到了表征,并显示了预期的结果。我们可以在铝和硅之间建立三个这样的基本接触。铝相对于硅来说是P型的,所以只要铝与轻度掺杂的N硅接触就会形成肖特基二极管。有时我的器件显示出隧道特性,而不是预期的二极管,因此我推断,如果同一器件在高温(>1000ºC)下处理较长时间,由于N型掺杂物在SiO2中的溶解度增加,硅表面的氧化程度增加,导致晶圆表面的磷"堆积"。这在表面形成了一个"N+"区域,较高的掺杂物浓度产生了一个不断减少的耗竭层,这与一个小的势能障碍有关(电子可以很容易地穿过它),解释了对称的IV曲线。

此外,可以破坏性地测试栅极氧化物介电击穿电压。对于高质量的SiO2,这应该略高于 1V/nm,并且很容易通过从 0V 扫描 Vgs 并注意大电流流过时进行测试(在正常操作中,栅极是绝缘的,应该没有电流流过)。

该图显示了 25nm 厚的栅极器件在 21.7V 时发生的栅极介电击穿,表明良好的热生长氧化物质量可以通过在具有较高氮含量的气氛中生长来改善。

还可以演示开关和差分放大器特性。右侧的轨迹显示了配置为全差分放大器的芯片输出,将 1kHz 和 50kHz 正弦波混合(相加/相减)在一起。

要测试的最后一个特性是低泄漏、完全绝缘的栅极,这是真正MOSFET 操作的主要要求之一。如您所见,我能够为器件的栅极充电并通过我的指尖通过高阻抗连接将其打开,并且FET 的 1, 0 状态由于电荷留在栅极上而“锁定” FET 并且没有消散路径。

很久以前,一些放大器受到"爆米花 "或爆裂噪声的困扰,人们认为这是由半导体内部缺陷的随机事件引起的。这表现为输出中巨大的阶跃脉冲变化,由于材料纯度和加工清洁度的提高,在现代集成电路中几乎已经消除了。然而,我做的一些器件表现出大量的爆米花噪声,如下图视频所示(差分对中的噪声在范围上被放大,零输入产生数百毫伏的输出)。关于这种类型的噪声,我最喜欢的一句话是一位工程师在提到MAX9776时说的:"你可以用青蛙腿和秒表来测量它。"我的显然属于这种类型...