近年来,每当我们引入一个新的先进工艺节点,大家都把绝大多数注意力集中在光刻更新上。引用的常用指标是每平方毫米的晶体管或(高密度)SRAM位单元的面积。

或者,可以使用透射电子显微镜(TEM)对薄片样品进行详细的分解分析,以测量鳍片节距(fin pitch),栅极节距(gate pitch)和(第一级)金属节距(metal pitch)。

随着关键尺寸层从193i到近紫外线(EUV)的转变,对光刻的关注是可以理解的。然而,制程开发和认证涵盖了材料工程的许多方面,才得以实现可靠的可制造性,进而实现产品目标的充分补充。具体而言,制程开发工程师面临越来越严格的可靠性目标,同时要实现性能和功耗的改善。

在最近的IEDM会议上,TSMC进行了技术演讲,重点介绍了使N5工艺节点能够达到(风险生产)资格的开发重点。本文总结了该演示文稿的重点。

在SemiWiki较早的文章中,我们介绍了N5的光刻和功耗/性能功能。N5的重大材料差异之一是引入了“高迁移率”设备沟道或HMC。

如文所述,通过在器件沟道区域引入额外的应变,可以提高N5中的载流子迁移率。(尽管TSMC没有提供技术细节,但通过向硅沟道区或Si(1-x)Ge(x)中引入适量的锗,pFET空穴迁移率也可能得到改善。)

此外,优化的N5工艺节点在栅极和沟道之间结合了优化的高K金属栅极(HKMG)电介质堆栈,从而产生了更强的电场。

该“带隙工程”对于载流子迁移率和栅极氧化物堆叠材料选择的一个非常重要的方面是确保满足可靠性目标。N5可靠性鉴定的一些结果如下所示。

请注意,N5节点的目标是满足高性能和移动(低功耗)产品的要求。因此,性能下降和保持主动的SRAM VDDmin都是重要的长期可靠性标准。

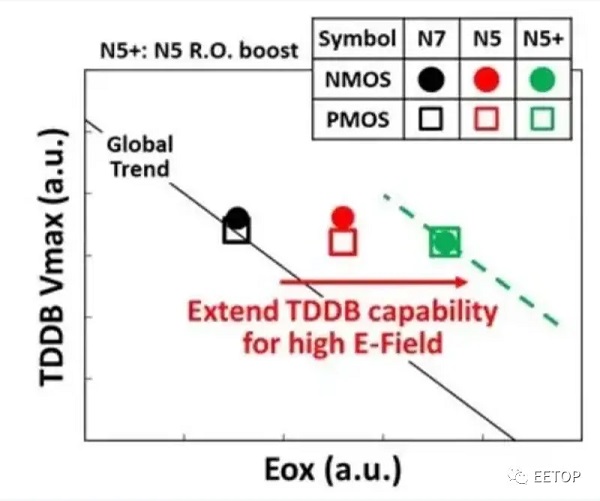

上图显示,即使栅极电场增加,TDDB的寿命也与节点N7相当

FinFET器件几何结构的引入大大改变了从沟道功耗到环境(ambient)的热阻路径(thermal resistance paths)。采用新的“自热”分析流程来更准确地计算局部结点温度,通常以“热图”形式显示。正如从N7到N5的尺寸激进缩放所预期的那样,N5的自热温度升高更大,如下所示。

HPC产品的设计人员需要与他们的EDA合作伙伴(用die热分析工具)及其产品工程团队合作,以进行准确的(die和系统)热阻建模。对于die模型,有源和非有源结构都会强烈影响散热。

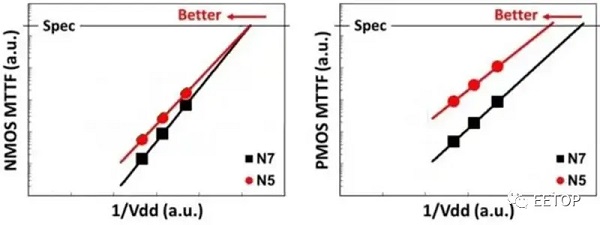

N7和N5的nFET和pFET的热载流子注入性能下降如下所示。

请注意,HCl与温度密切相关,因此必须进行准确的自热分析。

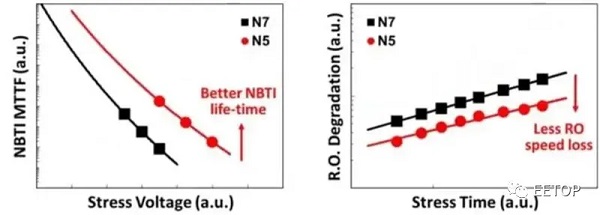

下面说明了pMOS NBTI可靠性分析结果以及相关的环形振荡器性能影响。

在这两种情况下,可靠性分析均表明N5相对于N7具有改善的BTI特性。

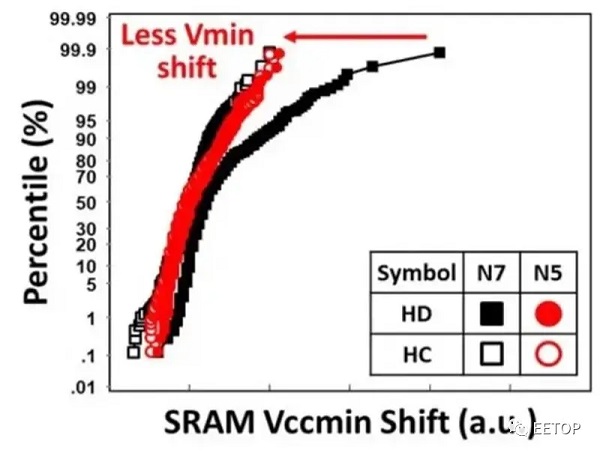

SRAM的最低工作电压(VDDmin)是低功耗设计的关键参数,尤其是对本地存储器存储的需求不断增长时。影响最低SRAM工作电压(具有足够的读写裕度)的两个因素是:

BTI设备转移,如上所示

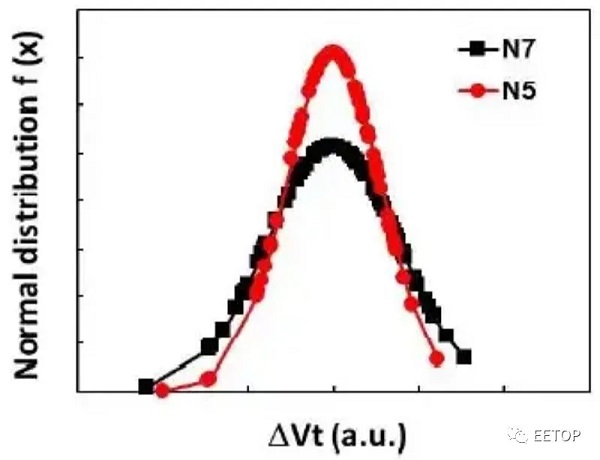

设备Vt的统计过程变化,如下所示(在N7和N5中标准化为Vt_mean)

根据这两个单独的结果,HTOL应力后的SRAM可靠性数据显示N5相对于N7改善了VDDmin影响。

台积电还简要介绍了N5工艺工程对(Mx,低级金属)互连可靠性优化的重视。通过改进的镶嵌沟槽衬里(damascene trench liner)和“ Cu reflow”步骤,Mx间距的缩放比例(使用EUV在N5中增加了约30%)不会对电迁移失败产生不利影响,也不会对线间电介质造成破坏。

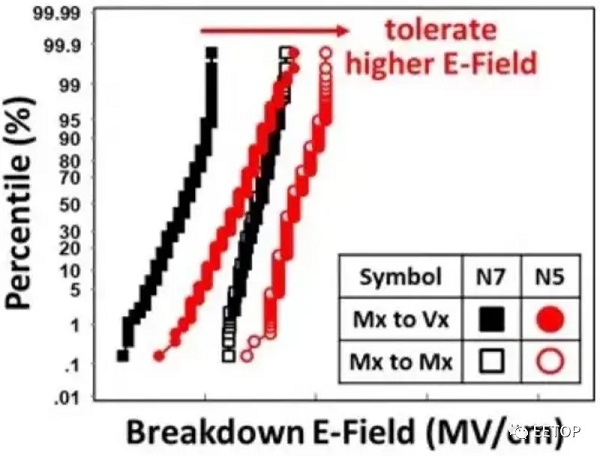

下图显示了N5的线到线(和过孔)累积击穿可靠性故障数据,而N7 – N5可以按比例缩放Mx间距来承受较高的电场。