异构,多芯片2.5D封装技术的最新进展导致了一种新型的接口,即超短距离(USR)接口,其电气特性与传统的印刷电路板走线有很大不同。长而有损的连接需要使用SerDes IP的串行通信通道,而短距离接口则支持并行总线体系结构。

SerDes信号需要(50欧姆)端接,以最大限度地减少反射和降低远端串扰,从而增加功率耗散。2.5D封装内的电短接口不需要端接。这些并行接口不需要 "恢复 "嵌入在串行数据流内的时钟,以及相关的时钟-数据恢复(CDR)所需的电路面积和功耗,而是可以使用更简单的“时钟转发”电路设计-提供传输的时钟信号带有一组N个数据信号。

该接口的另一个优点是,大大降低了芯片之间静电放电保护(ESD)的电路设计要求。内部封装连接将具有较低的ESD电压约束,从而节省了大量的I/O电路面积(并显着减少了I / O寄生效应)。

2.5D封装中裸片之间独特的接口设计要求导致使用“小芯片”一词,因为不需要SerDes链接的全芯片设计开销。然而,到目前为止,这些USR接口所采用的电路和物理实现方法相当多样。

在最近的VLSI 2020研讨会的受邀演讲中,台积电提出了他们关于并行总线,时钟转发架构的提案“ LIPINCON”,该架构是“低压,封装内互连”的缩写。

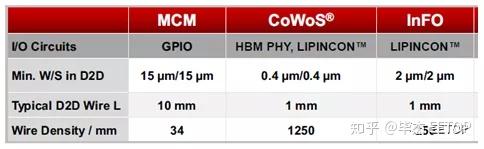

短距离接口设计的关键参数是:

架构师正在寻求最大程度地提高总数据带宽(总线宽度*数据速率),同时实现非常低的每位功耗。无论小芯片接口是在多个处理器(或SoC)之间,处理器到内存还是处理器到I / O控制器功能之间,都将应用这些关键设计措施。

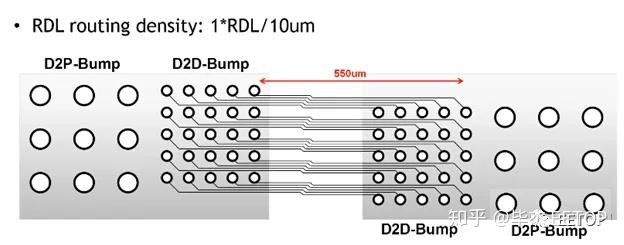

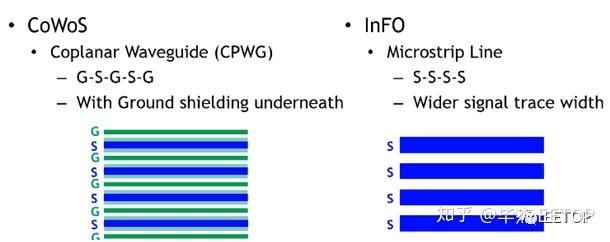

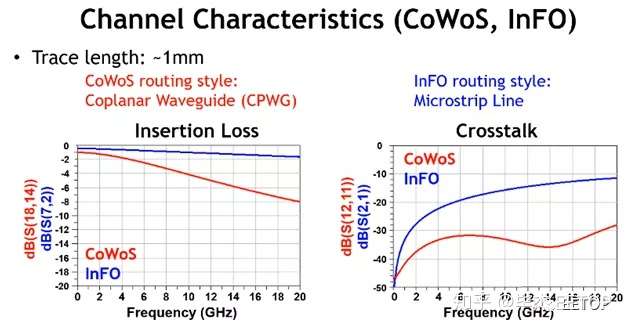

物理信号的实现方式会有所不同,具体取决于封装技术。具有硅中介层的2.5D封装的信号重新分配层(RDL)将利用可用的更精细的金属间距(例如,TSMC的CoWoS)。对于利用重组芯片衬底嵌入芯片的多芯片封装,RDL层要厚得多,间距要大(例如,TSMC的InFO)。下图说明了与CoWoS和InFO设计相关的典型信号走线屏蔽(和无屏蔽),以及相应的信号插入和远端串扰损耗。

下图示意性地说明了台积电LIPINCON IP定义的关键特性。

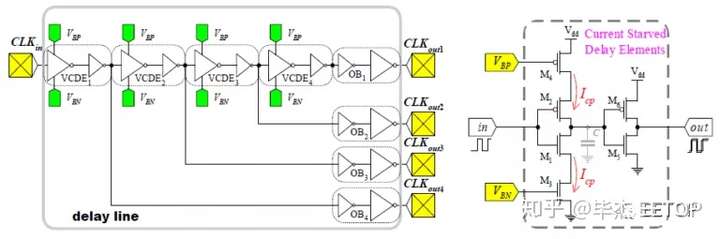

简而言之,DLL是一个独特的电路,它由相同延迟单元的(偶数个)链组成。下图显示了延迟链的示例。[2]通过调制输入到各级输入反相器(即“电流不足”的反相器)中的串联nFET和pFET器件的电压,可以动态调节各级的开关延迟。(其他延迟链实现会动态修改每一级输出上相同的电容负载,而不是调节每一级的内部晶体管驱动强度。)

DLL中的“环路”由相位检测器(带低通滤波器的XOR型逻辑)形成,该检测器将输入时钟与链的最终输出进行比较。输入时钟相对于链输出的超前或滞后特性可调节逆变器控制电压-因此,链的整体延迟“锁定”于输入时钟。DLL链中每一级的(相等)延迟提供与输入时钟信号的特定相位相对应的输出。使用适当的相位输出在接收器触发器中捕获并行数据,这是一种补偿接口上任何数据到时钟偏移的方法。

台积电IP团队针对SoC到内存接口的特定情况开发了一种创新方法。存储器小芯片可能不一定嵌入DLL来捕获信号输入。对于非常宽的接口(例如,将512个地址,256个数据位分成多个子通道),成本敏感型存储芯片中DLL电路的开销会很高。如下图所示,在SoC中出现了DLL相位输出,它用作存储器写周期的输入选通脉冲。(图中还显示了存储器读取路径,该路径说明了如何将来自存储器的数据选通脉冲连接到read_DLL电路输入。)

对于并行LIPINCON接口,与信号串扰相关的同时开关噪声(SSN)是一个问题。对于上面说明的屏蔽(CoWoS)和非屏蔽(InFO)RDL信号连接,TSMC给出的结果说明了这种低摆幅信令的串扰非常易于管理。

可以肯定的是,设计人员可以选择在小芯片之间开发逻辑接口,这些小接口使用数据编码来最大程度地减少连续周期中的信号转换活动。最简单的方法是添加数据总线反转(DBI)编码-可以将下一个周期中的数据与当前数据进行比较,并使用真实值或反转值进行传输以最大程度地减少开关活动。小芯片之间的附加DBI信号将这个决定传递给接收器,以解码这些值。

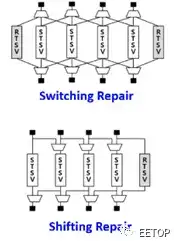

异种2.5D封装的开发依赖于已知良好芯片/小芯片(KGD)的集成。尽管如此,通过增加冗余通道可以提高最终包装的组装后产量,该冗余通道可以在包装测试后选择(理想的是内置自检)。台积电的演示文稿包括可以集成到小芯片设计中的冗余通道拓扑的示例。下图说明了用于将冗余的硅通孔(TSV)插入互连的两种架构。当设计小芯片之间的接口时,这将是封装良率与电路开销的折衷。

在基于SerDes的设计中,完整的电路和PCB互连提取以及仿真用于分析信号损耗。针对接收器传感放大器的电压差分析了信号抖动和幅度的变化。还进行了基于硬件实验室的探测,以确保在接收器处捕获数据时适当的“眼图张开度”。台积电强调,这种接口验证不适用于2.5D封装技术。如下图所示,他们的IP团队开发了一种新颖的方法,将变体引入LIPINCON发送驱动器和接收捕获电路中,以创建用于硬件验证的等效眼图。

台积电的演讲提到,他们的一些客户已经为USR接口设计开发了自己的IP实现。一个示例显示了一个非常低的摆幅(0.2V)电学定义,它是“以地面为参考”的(例如,信号摆幅高于和低于地面)。但是,对于寻求利用高级封装而又没有设计资源来“自行开发”芯片接口电路的无晶圆厂客户而言,TSMC LIPINCON IP定义是一种极具吸引力的选择。而且,坦率地说,考虑到台积电能够提供的动力,该定义可能会有助于加速寻求捕获IP和小芯片设计市场机会的开发商中的“标准”电气定义。