凭借多年的行业经验,我们总结了7大妨碍PCB可制造性的主要DFM问题。虽然以下列出的部分内容是设计方面的最佳实践,但还有一些是由制作/制造厂提出的问题。通过在项目的设计阶段解决这些问题,我们将能够在产品到达工厂之前纠正任何可能出现的DFM错误。

所以,在将设计发送给制造商之前,我们要注意下列DFM问题,因为它们可能隐藏在我们的设计之中。

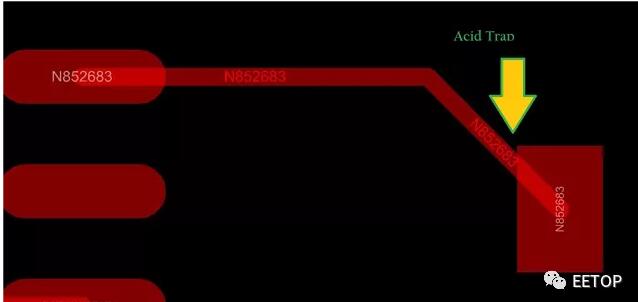

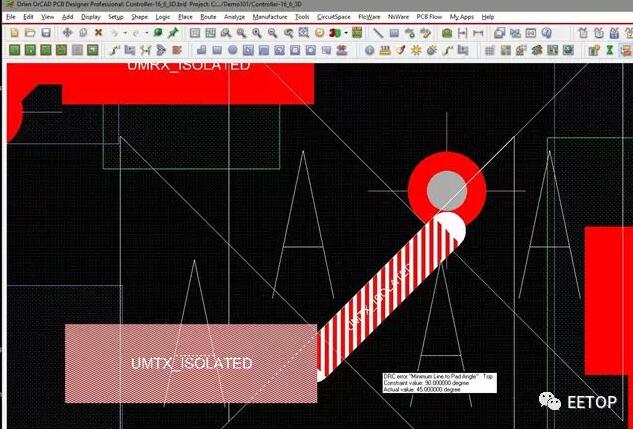

1.锐角

锐角是指印刷电路板中铜元件上的锐角或奇怪的角度,这些角会在PCB创建过程中导致酸的聚集。这个问题发生在洗涤过程之前,锐角导致残留的酸陷入这些区域,而无法清除。最终,电路板上所含Gerber文件需要的铜元件开始腐蚀,导致铜线“断开”或消失。

对于当今设计中的4密耳或5密耳走线,避免锐角尤为重要。因为它们很薄,所以很容易断开(由于吸附的酸,使有用的铜内部产生开口)。一些软件内置了针对此类情况的检查,但是,如果我们的软件没有此功能,则必须手动评估电路板中可能导致这种情况的任何可能。

如何防止锐角:避免将走线以锐角或奇怪的角度放入焊盘,将角度保持在焊盘附近45度或90度。

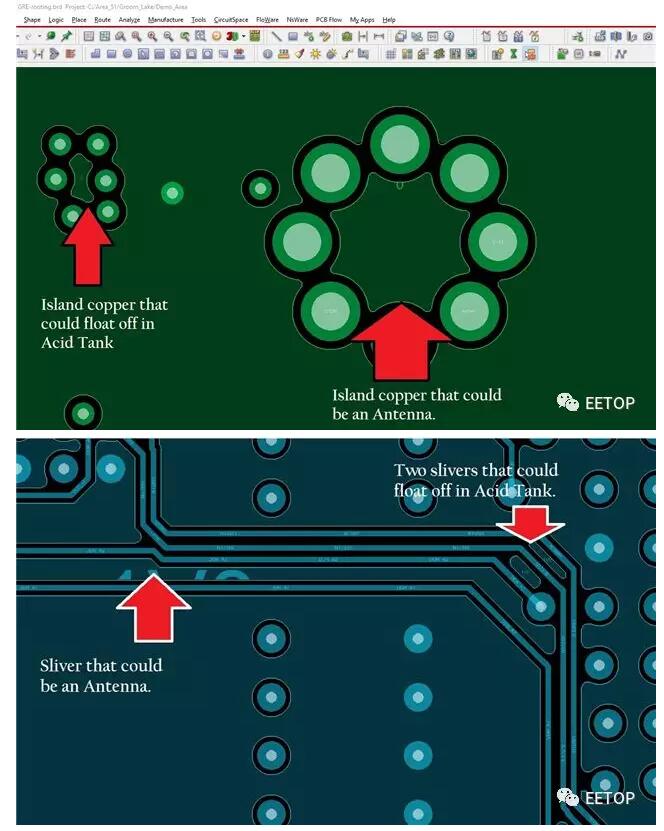

2.铜条和孤岛

由于蚀刻痕迹的划线非常精细且引脚间距非常紧密,因此阻焊层对于PCB设计非常重要。没有阻焊层会导致组装过程中出现大块焊料(尤其是引脚之间),进而导致短路。此外,它还会降低对外层其他铜的腐蚀防护性能。为防止这些问题,请务必检查焊盘到蚀刻线和外形之间的对准度、阻焊层间(边带)的间距。此外,确保阻焊层没有覆盖引脚——我们的电路板工厂可以告知其允许的最小边带空间和对准度。

4.散热器

散热器通过与金属基底或热界面材料接触来吸收和散发电子器件的热量。如果散热器中的助焊层开口太大,一旦焊膏熔化,可能会导致器件从焊盘上浮起。为了防止这种情况,减少放在散热片上的焊膏的量——不要采用一个很大的助焊层开口,相反,试着将其分成若干更小的助焊层开口。这将有助于确保器件在烘烤过程中不会漂浮和碰撞到其他部件,避免短路。

助焊层开口是DFM检查的重要部分。发送给制造厂之前要回答一个问题:PCB上的所有元件引线的助焊层开口(和尺寸)是否都适合板?

注意:我们的制造工程师应该告诉我们助焊层开口的合适尺寸。

5.冷焊点或无焊接线

检查焊盘内的过孔至关重要——如果过孔放置不当,可能会导致焊膏流入过孔。这将导致冷焊点或没有真正的焊料连接。我们需要确定:在要求堵住过孔之前,焊盘中允许的过孔百分比。注意:造成问题的是过孔中的孔,而不是过孔中的焊盘。

大多数软件应该都能够检查这些问题,但如果我们使用的软件不能,则必须手动检查设计,以确保其符合装配厂标准。

6.不包括测试点

在最终产品离开装配线后立即对其进行测试十分重要——通过在初始设计中纳入测试点,我们便提供了这样一种方法,能够在电路板完成后立即对其成败进行仔细检查。DFM检查必须包括测试点与器件之间的间隙、焊盘尺寸、器件背面,以及夹具制造完成后立即确定这些位置的方法。

然后,使用测试点数据创建一个夹具,称为针床式测试仪。针床式测试仪是一个软件系统,它可以在设计中锁定测试点的位置。凭借针床式测试仪,我们能够将设计变更重新加入该测试夹具中,从而节省资金。

如果等到原型完成后才纳入测试点,则可能会导致电路板上电子器件的更改(这可能会产生串扰、噪声和大量其他问题),因此无法真正测试电路板的真正功能。我们将需从本质上改变设计和电路板的运作方式。通过在设计阶段将测试点合并到电路板中,能为我们提供锁定现有测试点并仅修改更改(如有)的能力。

设计中添加测试点时的注意事项:它们容易接近吗?DM检查器是否确保我们的测试点没有被隐藏?引脚间距如何(确保它们不要靠得太近)?

注意:当我们将测试点放在电路板上时,它们成为DFM检查的一部分。

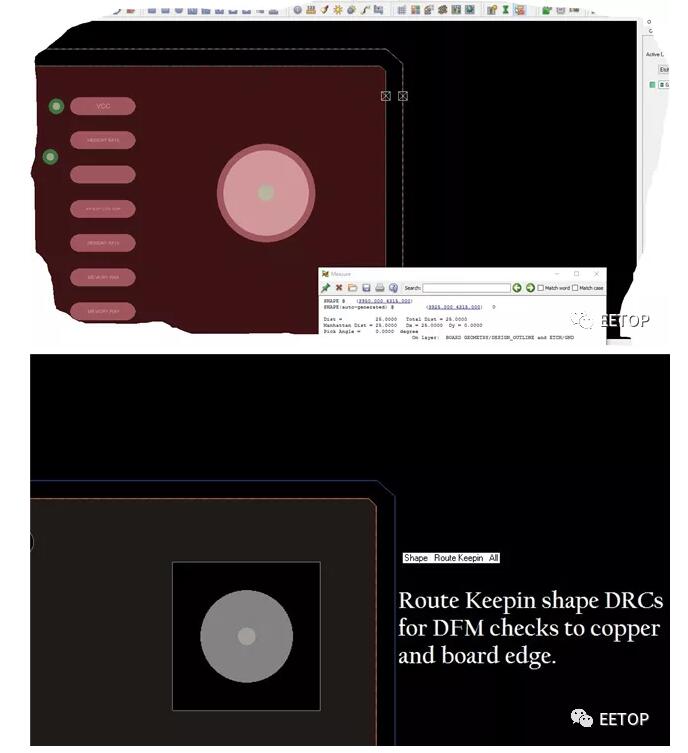

7.铜与板边之间

PCB的制作过程包括将电路板自动运输到酸浴和洗浴中。铜与板边之间指的是PCB面板侧把手上的空间,用于在整个制造过程中运输电路板。如果铜与板边之间的间距设置不当,就会产生真正的制造问题。如果铜离电路板的边缘太近,那么在蚀刻过程中,当电路板上通电时便会产生短路。

注意:用于制造电路板的设备将控制夹持面板所需的间距——我们的电路板制造商应该为此提供设计规格。

制造失败的后果不仅令人沮丧,而且代价高昂。通过可制造性设计进行前瞻性考虑只是避免遇到任何DFM问题的众多方法之一。上文列出的许多问题可以通过软件自动识别(如Allegro® PCB DesignTrue DFM Technology软件)。但是,如果您的软件没有DFM检查功能,则必须自己手动识别并解决它们。

所有工程师都最不希望收到制造商的“电话”,告知他们的电路板未通过DFM检查,因此在最终检查中寻找上述问题非常重要——无论是通过自动检查还是手动检查。

课程推荐:

《高速电路设计分析与仿真课程介绍》

课程介绍

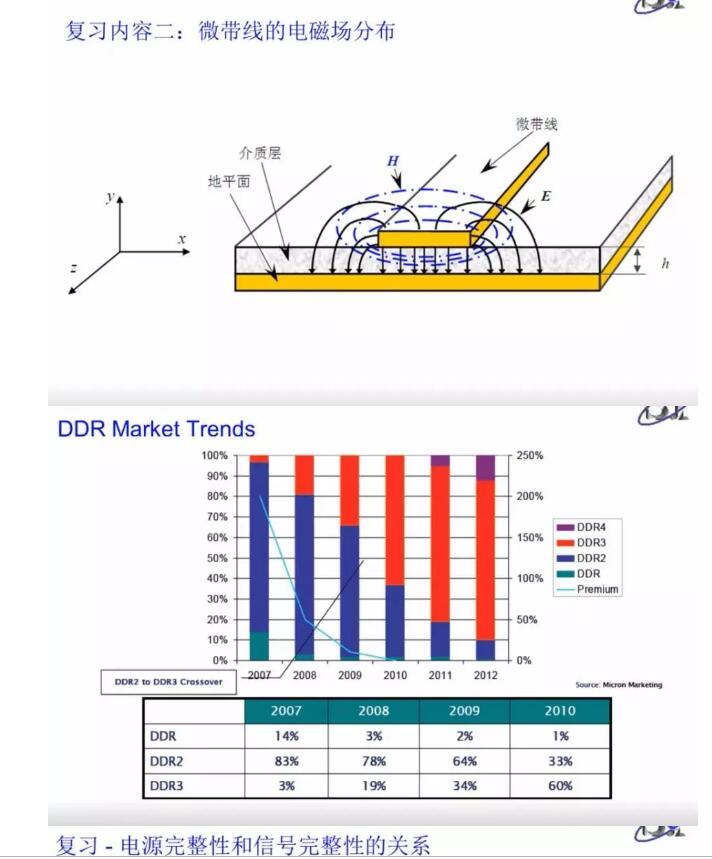

本课程基于讲师多年的实战经验,详细介绍了信号完整性(SI)、电源完整性(PI)较完整的知识体系,以及各种不同的信号完整性问题在实际项目中的体现,特别是最近DDRx技术领域,以及xGH高速信号领域的一些研究成果。通过理论和实践相结合的培养方式,帮助电子行业工程技术人员在理解高速信号传输本质的基础上,掌握分析SI问题的工具和技巧,提高PCB产品设计和不限房吗的专业技能,为企业培养优秀的SI工程师和项目管理人员,提高产品性能质量和可靠性,增强产品的市场竞争力。

培训效果

本课程是使得电子系统设计工程师们在正确理解信号完整性和电源完整性的理论基础上,能够更好的掌握高速电路系统设计的方法和技巧,跟上行业发展要求。

课程片段摘选

长按二维码参与学习

(可以免费试看)

讲师介绍

邵鹏,毕业于北京大学计算机系。历任IBM、Intel中国研究院系统架构师,研究员。从事高性能服务器基础架构研究,并负责从芯片到板级、系统全流程高速链路设计与仿真工作。