随着芯片系统的日益复杂,测试已经成为集成电路设计和制造过程中非常重要的因素,它已经不再单纯作为芯片产品的检验、验证手段,而是与集成电路设计有着密切联系的专门技术,与设计和制造成为了一个有机整体。可测性设计(DFT)给整个测试领域开拓了一条切实可行的途径,目前国际上大中型IC设计公司基本上都采用了可测性设计的设计流程,DFT已经成为芯片设计的关键环节。

“测试”和“验证”的区别

提到测试,人们常常会混淆两个基本概率:“验证”(Verification)和“测试”(Testing)。

一般来说,验证(Verification)的目的是检查设计中的错误,确保设计符合其设计规范和所期望的功能;而测试(Testing)则是检查芯片的加工制造过程中所产生的缺陷和故障。

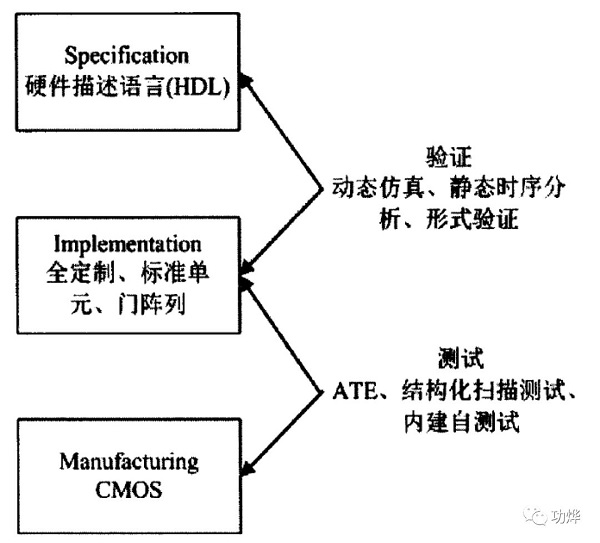

验证是检验电路的逻辑、功能、时序是否满足要求,其内容一般是功能性的,如上图所示,验证是把Implementation后的结果与Specification时的定义相比较,如果验证不匹配,则需要更改Implementation 。验证如同芯片设计过程中的一道关卡,如果验证没有通过,将不能进行后面的所有工作。验证一般采用仿真的技术来进行,通过计算机建立仿真环境,给被测电路添加激励,分析响应或者探查电路内部的信息。按照验证的不同阶段,仿真可分为功能级仿真、门级仿真、版图后仿真。

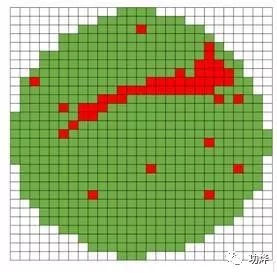

然而一个正确无误的设计并不能保证制造出来的芯片一定没有问题,因为芯片在制造过程中,总会收到种种不确定因素的影响,比如环境干扰、硅片质量不一致、机台设置偏差、工程师失误操作等因素的影响,制造出来的芯片并不完全都能正常工作,那么如何检验出有制造缺陷的芯片,这就是属于测试的范畴,现在最先进的7nm制造工艺中,线宽非常精细,工序数量多,非常容易受到干扰的影响,制造故障变得尤为明显,所以加大测试的力度,保证芯片合格尤为重要。

芯片在生产过程中的测试相关内容,这里不展开讨论,有兴趣可移步:集成电路芯片测试小结,集成电路封装与测试介绍。

DFT技术简单说就是在芯片设计中添加DFT逻辑,然后等芯片制造完成后,通过事先加入的DFT逻辑对芯片进行测试,挑选出没有问题的芯片。

DFT技术更专业一点说法是为了改善电路的可测性而形成的一门学科,它通过增加一些硬件电路,使得电路内部节点的可控性和可观察性变强,使测试时间变短、故障覆盖率更高。

可控性和可观察性

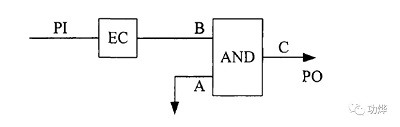

可控性:指的是是否可以从电路的初级输入控制内部引线逻辑状态。一条链路可以通过电路的初级输入端(PI)控制其状态,则这条链路称是可控制的,否则就是不可控制,见下图,二输入与门有两个输入端A和B,如果A直接接地,B是网络EC的输出信号。在这个电路中,无论初级输入端PI的值是什么,与门的输出端C始终为0,不可能为1,则C是1不可控的。

可观察性:指的是是否可以从电路的初级输出端或其他特殊的测试点观察电路内部引线逻辑状态。内部引线A的值可以通过某种方式传播到PO,在上图中,由于C的值始终为0,并且是由于A的值为0所致。因此在C位置就不能判断B点的逻辑值究竟是什么。假如C是电路唯一的PO,则内部引线B就是不可观察的。

这篇暂时介绍到这里,后面继续写更详细的内容。