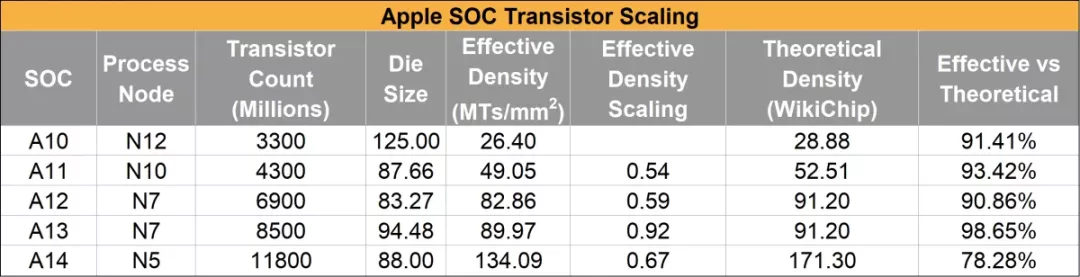

晶体管密度因不同的芯片结构而异。逻辑结构可以在每个新节点上很好地扩展,但是如今SRAM,I / O和模拟部件很难扩展,因此代工厂发布的峰值是高度理论性的,而实际数字是取决于设计。

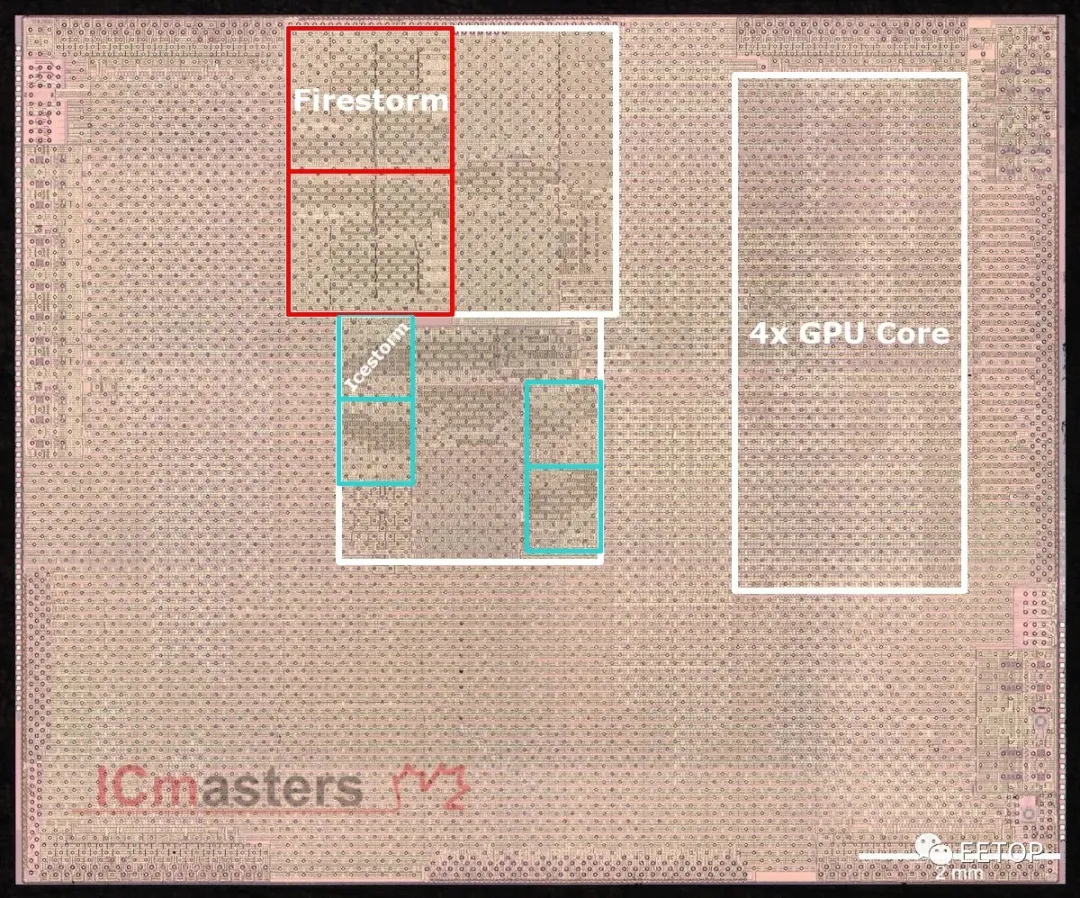

同样,芯片的某些部分必须以更高的时钟频率运行(例如,通用内核)。通过使用通常更大的高性能电池,这些零件可能会牺牲性能密度。实际上,考虑到苹果公司对最终性能的关注,其SoC通常具有大容量缓存以及可能进行其他性能优化。

台积电的N5节点与之前的微缩有所不同,显示出SRAM扩张放缓的迹象。尽管是一个完整的缩小与逻辑,SRAM是一个1.35倍缩小,这个数字被夸大了。因此台积电的指引是N5可使晶片面积减少35%-40%。半分析预计,这将是一个趋势,并将持续与新的节点。台积电和三星已经在展示3D堆叠SRAM,这将有助于缓解密度问题。

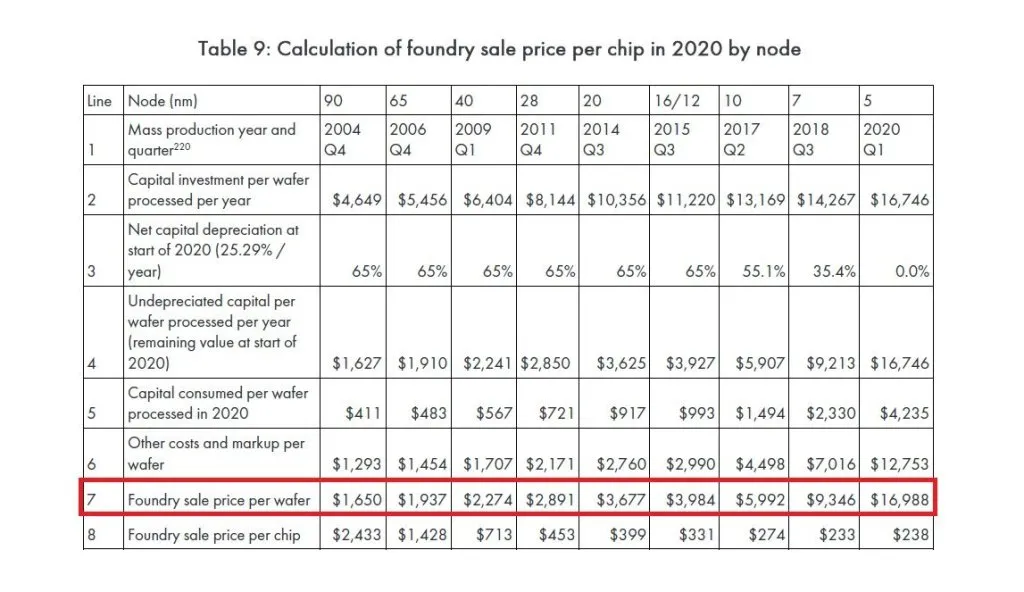

3D堆积并非万能的,成本缩减已经开始大幅放缓。台积电N5晶圆定价在1.7万美元左右,显然每个晶体管的成本并没有下降。即使SRAM的缩放速度跟上,每晶体管的成本从N7到N5也将保持不变。