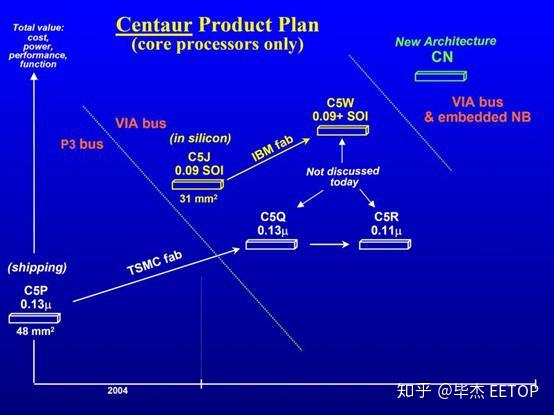

先不论Centaur 要怎样支撑威盛那「开辟新战场,延续高成长」的战略大计,光从2000 年到2004 年,那让人摸不着头绪的纷乱产品时程表,就够笔者和潜在客户伤透脑筋了。

回顾上篇:

笔者不敢斩钉截铁的确信,当初威盛花大钱,一口气购入Cyrix和Centaur,有没有打算建构「高低档搭配」产品线(高端Cyrix,中低端Centaur)的野心,或者觉得这两间的文化是互补的。但情势的演变,让Centaur 不得不面对「追求高效能」的挑战──即使初代超标量流水线的C5X,死在Centaur 自己的手里。

砸了超过两亿美元进军x86 处理器市场的威盛,透过收购Cyrix 而得到的Intel P6 总线授权,期限只到2006 年5 月,2001 年3 月25 日让VIA C3 取代CyrixIII,更等于直接把Cyrix 品牌丢到水里。到头来,手上还有专利可和Intel 讨价还价的Centaur,乍看之下,是仅剩的有价值资产。

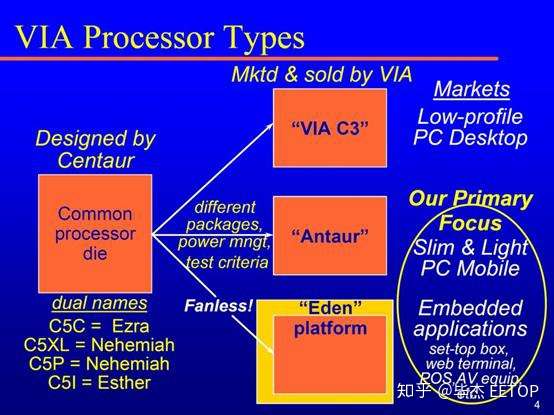

来自威盛高层的期望,都充分反映在「产品代号充满圣经味」的产品路线图,「双重产品代号(威盛的圣经人名和Centaur 的CxX)」也是威盛x86处理器的一大特色。更糟的是,这两者还不是「一对一」的,让产品代号与行销名称之间的对应关系,更显得混乱不堪。

眼见为凭,就请各位看倌慢慢欣赏。

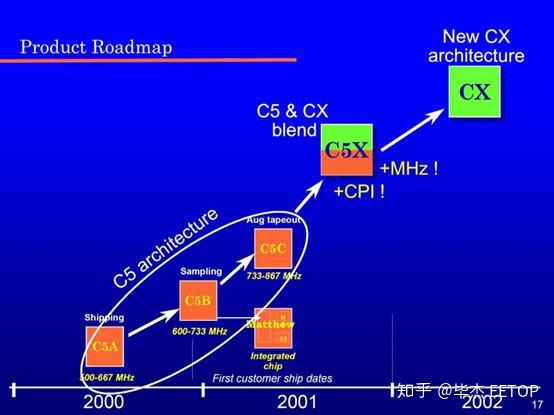

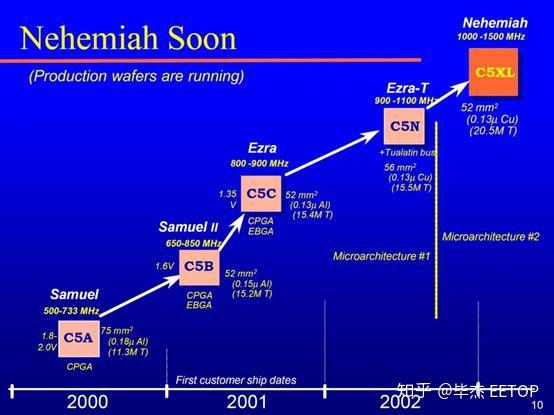

2000年:Centaur的首要之务是持续改进并缩小C5家族,并追逐1GHz主频。此时简报挂出来的品牌还叫做VIA Cyrix。

此外,威盛在2000 年4 月11 日以3.23 亿美元的代价,将S3 绘图芯片部门转移至新成立的VIA-S3 合资公司,冒出个打包威盛北桥芯片组和S3 绘图核心的Matthew,实乃理所当然之事。最起码,在当时威盛高层应认定这是市场渴望的「马太福音」。

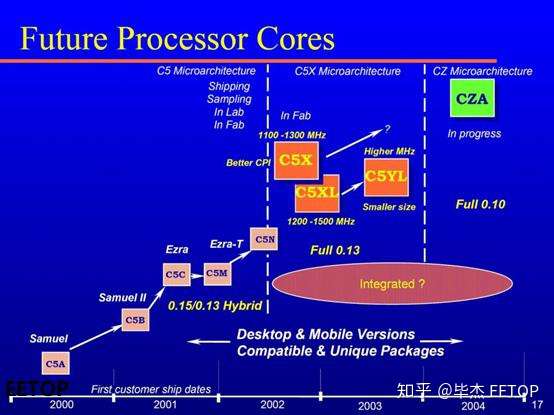

但Centaur 有个更艰巨的任务:在越来越炽烈的效能军备竞赛,不能再像过去一样「装死」。各位可回想一下,2000 年刚好是Intel 和AMD 爆发1GHz 主频争夺战,并点燃后来长达20 年x86 双雄战役的关键时刻。产品时程表出现了Centaur 史上第一个超标量流水线的x86 处理器核心C5X,与全新的CX,也就是我们所熟知的Nano。

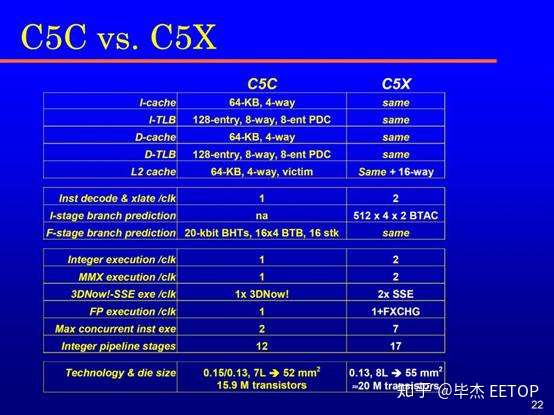

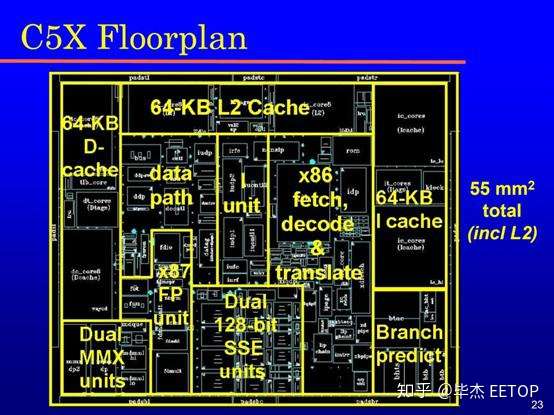

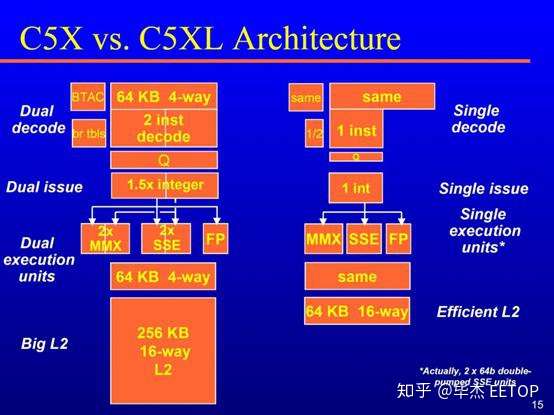

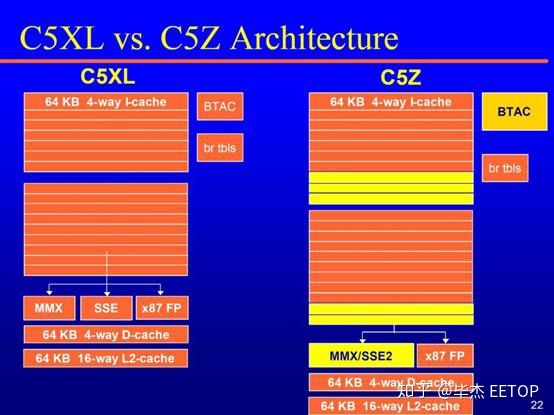

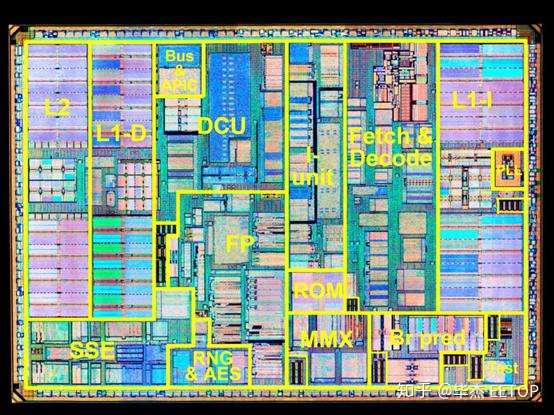

C5X 不仅是货真价实的超标量x86 处理器核心,支持SSE 指令集,更有着强大的动态分支预测、更深的指令流水线与倍增的内部执行单元。当初Centaur 没写在简报内的是,为了确保可每个时钟周期撷取两个指令,C5X 导入预先指令解码(Pre-Decode)的指令Cache,提前标定Cache的指令边界(x86 指令集的长度并不固定),这让实际所需容量爆增40%。

这很显然违背Glenn Henry 的「信念」,也因此,预计2001 年第三季出货的C5X,真的能顺利诞生吗?预估的55 mm² 看似不大,但你怎么猜得到威盛高层或Glenn Henry 会吝啬到什么程度?更何况当「预算」超支的时候?

2001年:浮出调降电压、压低耗电量的C5C「Ezra」。Cyrix品牌也默默的消失。

Ezra-T 的那个T 代表的是末代IntelPentium III「Tualatin」使用的改良版P6 汇流排(Tualatin Bus,或称为P3 Bus),AGTL 电压准位从1.5V 调降到1.25V,在还造成某些Intel 晶片组的相容性问题,某些骨灰级电脑玩家应该依稀还有点印象。

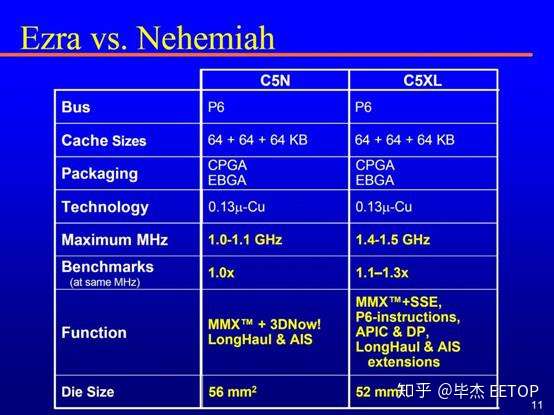

C5M 仅用来进行样品测试,真正投入量产的是C5N。

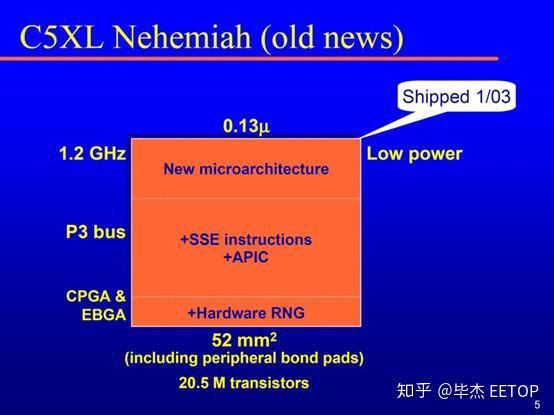

C5X 则延后到2002 年,还跑出来衍生款C5XL 和C5YL,这并不是什么好兆头。

全新未来架构从CX 改名成CZA,意义不明。

C5XL(Nehemiah)是C5X 的精简版本,也是Glenn Henry 最爱的「超标量」处理器,符合「简单、迅速、便宜」的大原则。这时公布的C5X也与一年前略有出入,至少指令流水线深度被缩短了,芯片面积也增大到78 mm²,隐隐约约让人感受到这踩到了某个人心中的红线。

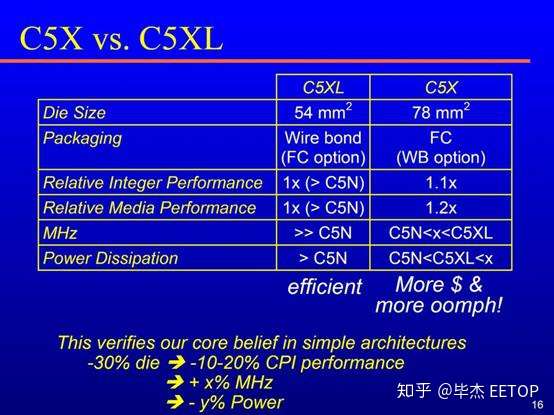

「证实Centaur 对简单微架构的执着是正确的」的C5XL,牺牲10% 整数与20% 多媒体效能,但减少了30% 晶粒面积,利于提高时钟频率,降低能耗,而且C5X「更贵更热」。

2002年:既然有了便宜的C5XL,做为「先导研究案」的C5X就没存在的必要了,Centaur首款超纯量管线x86处理器,就此胎死腹中。

但C5XL 并非一团糟,相较于C5N,在相同制程,C5XL 的面积更小,时脉更高,支援SSE 指令集。让人眼睛一亮的是,C5XL 具备了多处理器环境必备的先进可程式化中断控制器(APIC),这让C5XL 可实作双处理器组态,但这张支票到了C5XL 的下一版C5P 才兑现。

C5XL 有一点值得大书特书:浮点运算不再只跑一半主频,真是可喜可贺。

不过,以C5XL 做为全新起点的演进图,却更让人感到一头雾水。一个C5X 被腰斩的前车之鉴摆在眼前,谁敢保证产品roadmap上的代号,有几个可以苟活?更何况,给客户看因「比晶体管更厉害的谋略」而随时大风吹的产品时程表,对经营事业与开发客户,真的妥当吗?

千万不要改改roadmap 没什么大不了,对Intel 和AMD 来说,一旦爆发这种大事,一堆人都要准备去「找头路」了。

偏偏这又是不少台商甚少意识到的坏习惯,自己关起门来「精雕细琢,近乎苛求」是一回事,改来改去(搞不好还改上瘾了)的「 Roadmap」往往是客户规划产品时的大灾难。「先当个简报王,等有客户被骗上钩再开案」确实是常见的业务开发技俩,但这招玩久了,只会让自己彻底信用破产。此类英勇事迹,在业界可谓班班可考。

全新未来微架构又从CZA 改名成CN,意义依旧不明。

再跑出来多出SSE2 指令集、强化动态分支预测的C5Z。第一时间先问:它活得下去吗?

那个看起来很像「试水温」的C5Y(疑似系统总线换成VIA V4 Bus)和C5XP(C5XL的低耗电版),似乎也很危险。那颗不存在的C5XL/Z 的系统单芯片,就假装没看到好了。

2003年:威盛开始以市场区隔细分品牌:VIA C3入门桌机、Antaur笔电、Eden嵌入式应用,继续大混乱中。

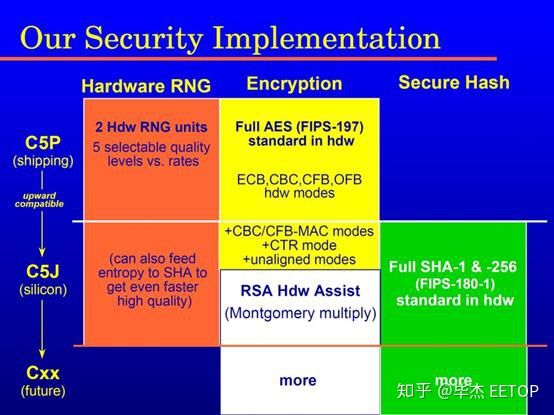

这提到了之前没讲到的C5XL 的硬件随机数发生器(RNG,RandomNumber Generator),看来威盛想从资讯安全应用发掘一些独特的利基点。

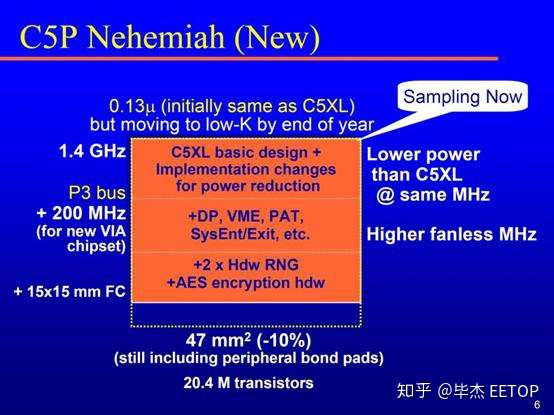

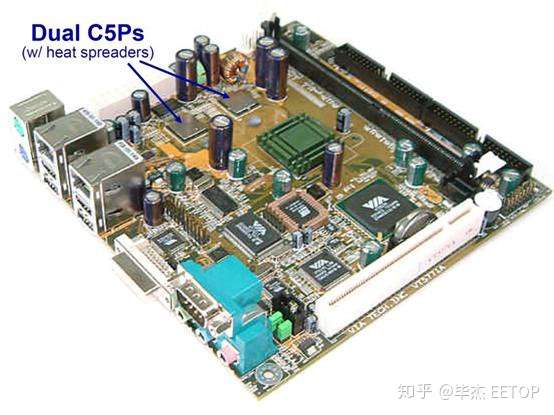

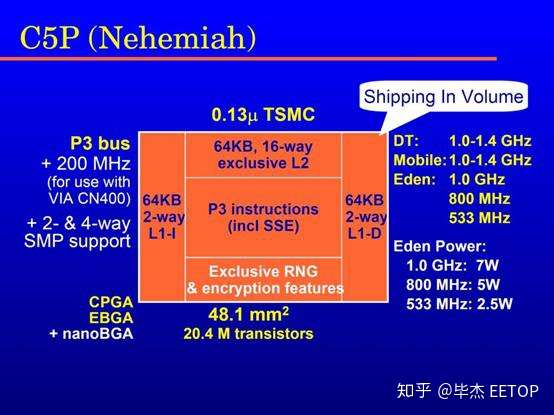

又跑出来C5XL 的微幅改良版C5P,在「例行公事」降低能耗、缩减面积、提升系统总线之外,扩增本来该在C5XL 就给的双处理器组态(DP)、虚拟化( VME)、分页位址属性表(PAT)、硬件随机数产生器(RNG)、和硬件AES 解密等。但对Centaur 和GlennHenry,减少10% 芯片面积才是重中之重,就为了「简单、迅速、便宜」。

双C5P 处理器看起来很威,但是威盛有信心两颗打得过人家Intel AMD 的一颗吗?

0.18µm 制程、支持SSE2 的C5Z 跑到哪里去了?这个硬件SHA-1 密码杂凑演算法的C5I 又是从哪边跑出来的?

但这时候威盛x86 处理器的时程表,总算有了一贯的逻辑(尽管维持双重核心代号):从Pentium III 「Tualatin」总线移转到相容Intel Socket 479 脚位,但电器信号改用自家规格以避免侵权,并在通讯协定层面稍做改进(如资料写入效率)的VIA V4 Bus。

细心的读者一定会留意到:C5P 的规格又被偷偷的小改了。

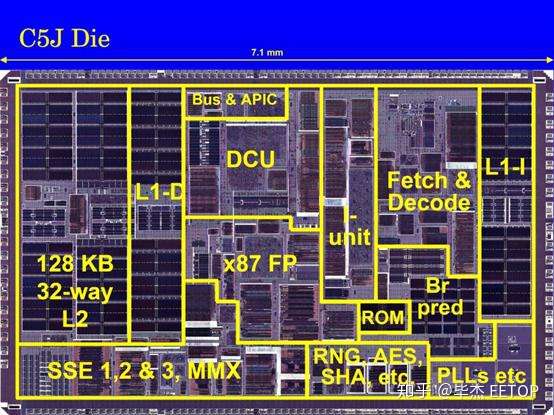

2004 年5 月18 日公开C5J 产品代号、2004 年9 月17 日公布VIA C7 品牌、到2005年5 月27 日产品上市,C5J 算是历经4 年的集大成之作,从制程、时钟频率、快取、指令集、总线、资安硬体功能到多处理器,在每个环节都有重大的跃进。

靠着IBM 的0.09µm 制程,C5J 芯片竟然缩小到31.7 mm²,仅为WinChip 2(95 mm²)的三分之一,Glenn Henry 这个人与其领导的Centaur 团队,对于压低成本的执念之深,让人感到恐怖。也许把产品「cost down」到看起来很玲珑精巧,就是他们工作成就感的来源。

「几乎Tape Out」的C5I(被C5J 取代),和C5Q(台积电0.13µm)、C5R(台积电0.11µm)与C5W(IBM 0.09µm 改良版),也就默默消逝在简报的尽头。

走过风风雨雨的4 年,这么多的Centaur 产品代号,扣除早期的C5A/B/C,仅C5N、C5XL、C5P 和C5J 撑到量产上市的那一天。

很巧的是,这段期间,也正是Intel 以威盛未得其同意,擅自销售Pentium 4 处理器相关芯片组为由,对其发动官司诉讼大战,并纠缠了近3 年。这场法律战的影响,与是否就是产品开发计划东改西改的主因,外人就不得而知了。

但唯一可以肯定的是:威盛和Centaur 对「降低成本」的坚定信仰,如同信奉宗教般的虔诚。天真的相信,只要东西做得够便宜,就一样会有人愿意买单,又偏偏是不少台湾企业(或许可加上某些美国人)的通病。

俗语说的好:出来混的,总是要还。多年来死守「成本至上」信条、坚决抗拒高效能处理器主流技术趋势的Centaur,终究得面对效能竞争力远远不如对手的残酷现实(到了2005 年,还没有超标量流水线,距离Intel Pentium已12 年),64 位元的普及速度超乎众多x86处理器小厂的预期(Transmeta 对此应该很有感),更是需要尽快提供解决方案的重点项目。

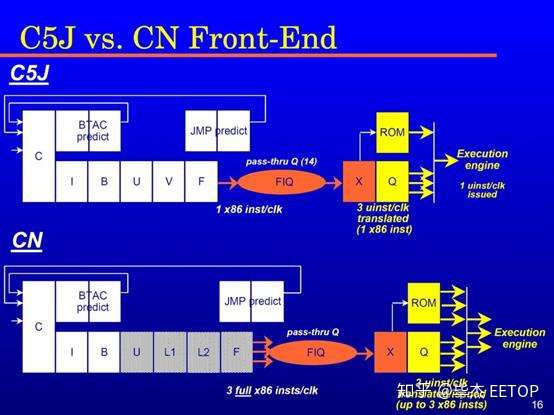

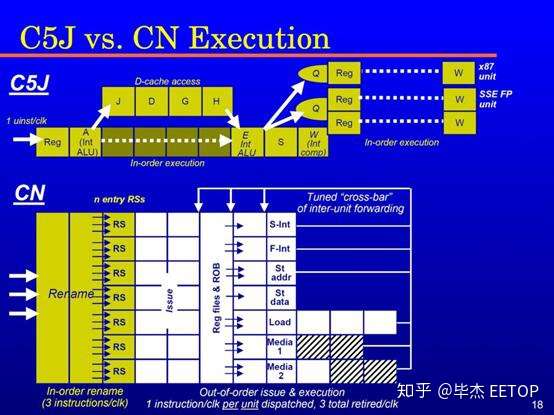

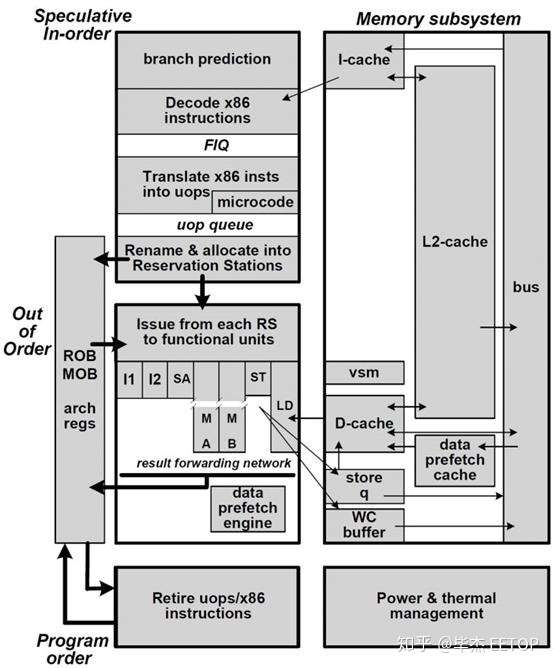

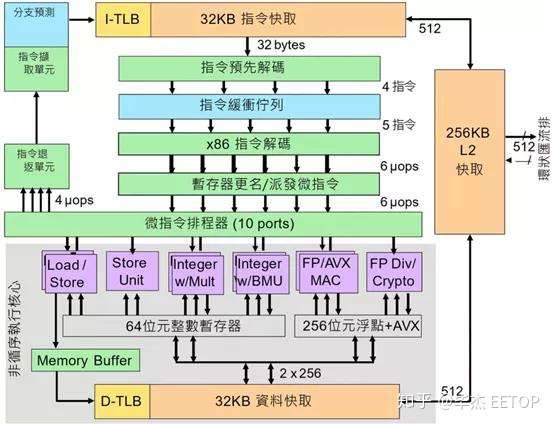

在2004 年10 月5 日,跟随着C5J(VIA C7)一同曝光的「全新下一代微架构」CN,很明确的昭告天下:Centaur 还是得拥抱超标量流水线、「魔鬼的工作」非循序指令执行、预测执行(结合动态分支预测和非循序指令执行),以及64 位元和更高效率的多媒体应用效能。当然,在任何可以想到的环节,也势必要有足够的进化,才有可能跟得上x86 双雄的脚步──最起码拉近那巨大的差距。

令人感到好奇的是:「面面俱到」的CN,其产品开发时程,还能够像过去的Centaur 产品,一样的神速吗?还有办法在两年之内,也就是在2006 年就推出产品吗?

笔者只知道:从公司创立以来,微处理器报导(MicroprocessorReport)举办的活动,几乎无役不与的Centuar 与其看板人物Glenn Henry,从2005 年到2007年,就再也没站上这些活动的演讲台了。

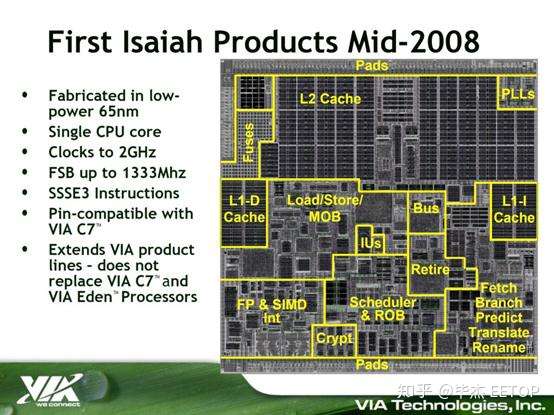

等待了整整3 年,2008 年1 月23 日,威盛公开代号Isaiah 的新一代x86 处理器微架构,3 月开始大量提供样品给客户,5 月29日正式命名为Nano(凌珑)处理器系列。其脚位与C7 相容,因此厂商与客户可用较低的成本升级产品,也同步推出超低电压的低功耗版本。

再来就是一连串事件发生时间与我们越来越近的故事。

2009 年11 月3 日,从富士通65nm 制程转进至台积电40nm 制程的Nano 3000 系列,开始支援SSE4.1 指令集,并修正「残废」的第二个整数运算单元,使其可执行大多数整数运算指令。

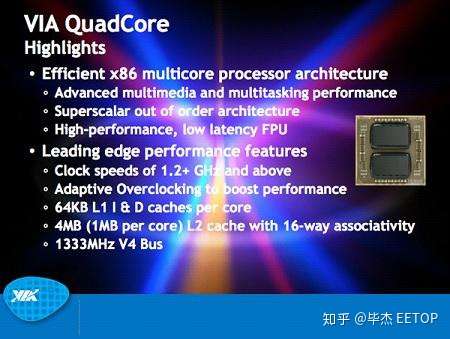

2011 年5 月5 日,台积电40nm 制程Nano X2 迈进原生双核心。

2011 年第三季末,四核心(两颗双核心封装成单一晶片)正式出货。

2014 年夏季,台积电28nm 制程、时钟频率2GHz 的「Isaiah II」样品与测试数据曝光,支持SSE4.2、AVX 与AVX2 指令集。

但却也被人发现:在某些SPEC CPU 的效能测试项目,编译程序时启动AVX / AVX2 时,效能不增反减,推测跟实作AVX / AVX2 的手段有关,很可能只是透过修正微码实现相容性,但处理器微架构层面却毫无任何配套措施(Intel 和AMD 都为此下足功夫),无愧Centaur 那套「简单、迅速、便宜」的最高指导原则。

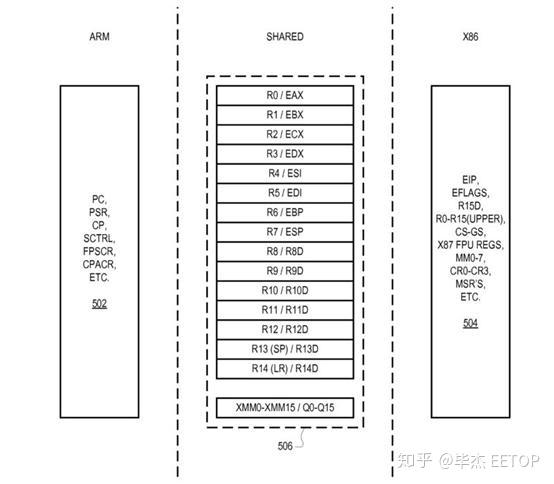

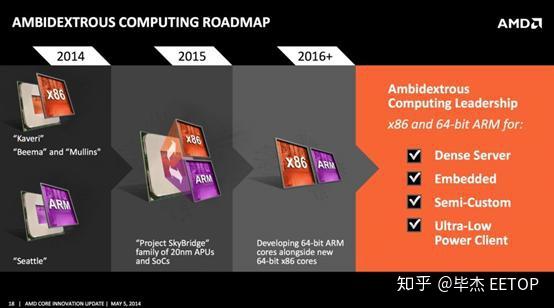

有趣的是,那时有人注意到,威盛有份「疑似打造x86 /ARM 混合架构处理器」的专利,也刚好是AMD 刚宣布将融合x86与ARM 的系统架构,并研发K12 处理器的「简报王」时期,让人不联想到威盛想趁机跑去凑热闹的念头。最后,无论是AMD和威盛,这伟大的创举,从来就没有成真。

总之,各位可以回忆一下,在任何威盛推出新品的时间点,Intel和AMD 摆在市场上的是哪些产品,又是怎样的制程和规格,又是何等规模的性能与出货。然后威盛与x86 双雄的差距,就这样越拉越远。基本上,说威盛早就看不到那两家的车尾灯,恐怕也不会有太多人会「胆敢」反对。

至于威盛这间公司为何从叱咤风云的台湾股王,走向极盛而衰,到近几年面临下市危机的惨况,在过去早已是无数财经媒体的封面故事,就不在本文的探讨范围,也没有特别为此大书特书的必要了。笔者只记得十几年前,威盛某高层曾豪情万丈的公开喊话:在嵌入式应用的市场,没有AMD 的份。

难道威盛和Centaur 的x86 处理器,除了低价位的嵌入式应用整合方案外(其实威盛握有的武器是很完备的),就没有其他的出路吗?2019 年11 月18 日的新闻稿,倒是提醒了世人,他们并未坐以待毙,寄望从人工智能的推理应用,找出一条生路,甚至还有机会从5G 时代的边缘运算平台(MEC ),切入服务器市场。

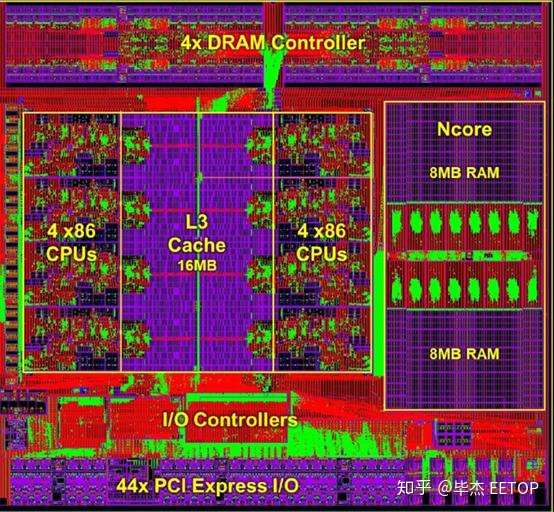

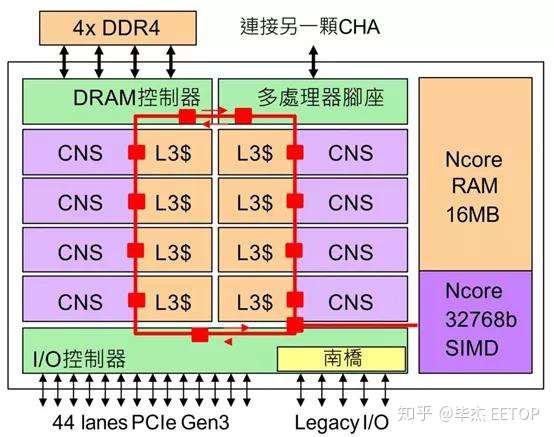

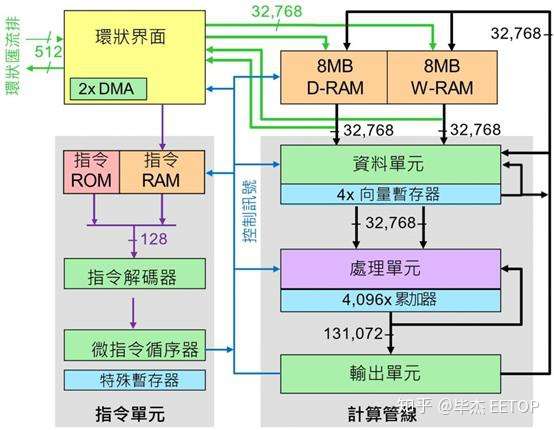

在2019 年11 月18 日亮相的CHA 系统单芯片,整合了8 个CNS 处理器核心、16MB 第三级Cache、4 通道DDR4 存储器控制器、44 Lane PCIe Gen3、Ncore 人工智能协处理器,并可双处理器组态,2020 年下半年量产,这是自从Nano 之后,睽违超过十年的全新设计。CNS 采用台积电16nm 制程,芯片面积是「破天荒」的195 mm²,标准设计功耗不高于85W。而此时此刻,Glenn Henry 则已经是半退休状态了。

Centaur 宣称CNS 是「IntelHaswell」等级的微架构,从环状架构(Ring)处理器内部总线也看得出Sandy Bridge 到Broadwell 的影子(之后的Skylake 就转向更有效率的Mesh 汇流排),但22nm 制程的Haswell却早在2013 年6 月4 日就已出现,技术整整落后超过6 年的CNS,论处理器核心的效能,根本一点拼面都没有。若无让人眼睛一亮的新兵器,连能否打得过Intel「瞄准5G 基站商机」的24 核Atom 处理器,都是天大的问号。

所以除了连AMD Zen2 都尚未支持的AVX-512 指令集(虽然内部拆成两个256 位元运算微指令,实际效能有所疑虑),就是从5 年前开始热门的「人工智能处理器」下手了。

CHA 的产品定位,很明显的锁定5G 时代的边缘伺服器,如ETSI NFV 架构的多接取边缘运算(Multi-access EdgeComputing,MEC),或工业物联网的网关(Gateway)。较「古老」的16nm 制程,大概可提高CHA 对恶劣运作环境的防御力。而根据「人工智能即将无所不在」的教条,这些应用或多或少用得到推理功能(像人脸辨识之类的)。威盛想踏入高获利的服务器市场,意图不言可喻,但CHA 值多少价格,那又是另一回事了。

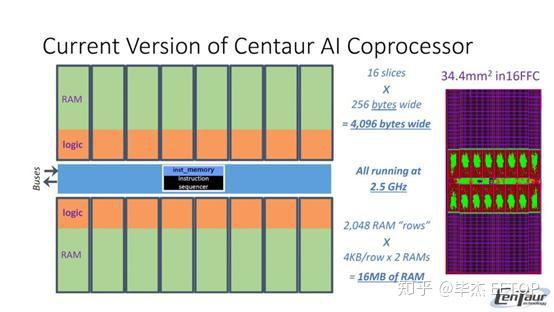

由Glenn Henry 亲自操刀的Ncore 人工智能协处理器,芯片面积34.4mm²(恰巧是他非常熟悉的尺寸),采用超宽的32768 位元SIMD架构,藉由理论值20TB/s 的16MB SRAM 挹注充沛的存储器频宽,当执行推理常用的INT8 短整数时,拥有每秒20 兆(20T/s)的最高运算能量。Ncore亦可支援在深度学习开始普及的Bfloat16 浮点数,但峰值效能会只剩下INT8 三分之一。

这看起来好像很了不起,但这性能究竟如何,可以参考一下Google的第一代TPU(2016 年):INT8 最高效能约92T/s。换句话说,Ncore 连其四分之一都不到,大致上跟Pascal 架构(2016 年)的nVidia Tesla P4 相去无几(22T/s)。同场加映Turing 架构(2018 年)的nVidia Quadro RTX8000 是261T/s,推理专用的T4 则是130T/s。

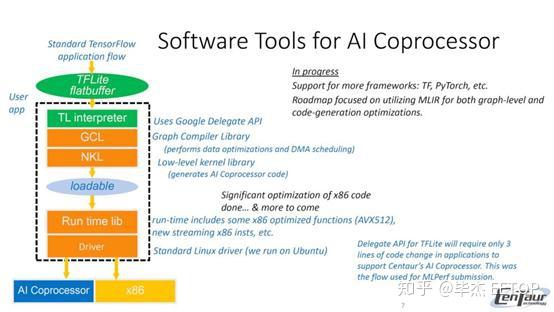

当然,你也可以认定这个Ncore 是「免费附赠」的,效能单位成本与「效能/ 功耗比」,可能远优于现有市场上的其他方案,无需外挂运算加速卡也是显而易见的优势。但对于人工智能应用,因为「硬件制造商和软件开发者」之间的鸿沟实在太深(像Google 这样自产自用TPU,反而就没这样的困扰),意思就是这票技术先驱者做出来的硬件,不是不好用就是不合用,导致5 年前吸引众多有志之士一窝蜂涌入的人工智能芯片热潮,正在急速退烧中。

威盛和Centaur 是否能够提供满足软件开发者的完整解决方案,避免重蹈覆辙,犯下无数「先贤先烈」的过往错误,将决定压宝人工智慧这个决定的成败,否则,CHA 将沦为「即不简单,更不迅速,只能便宜」的低价产品。

「唯偏执狂得以幸存」(Only the ParanoidSurvive),是Intel创办人之一的安迪‧葛洛夫(AndyGrove)的传世名言,一语道尽他战战兢兢、戒慎恐惧经营Intel 的心路历程。但我们也很清楚,Intel 之所以会如此成功,也不是只靠偏执而已。Centaur 偏执于「简单、迅速、便宜」的理想之路,却是另一个极端的反例。

他们的确靠着死守着最低成本的坚持,成为Intel AMD之外,唯二还念得出名号的x86 处理器厂商(另一间是俄罗斯的Elbrus),但这些产品是否带来商业上的成功,相信各位心中自有定见。也许威盛并未供给Centaur 足够的经费和人员,也施加极度严苛的成本要求,在Time ToMarket 的前提下,难以完成更先进产品的开发。

这些年来,Centaur 也很可能存活得很艰辛,朝不保夕,箇中甘苦,不足外人道也。但不幸的是,市场和消费者并不会理会这些「借口」,他们只会在意产品能不能让他们感到满意。

不计代价的把东西做到价格最低廉,就绝对会有人乐意接受?这世界的运作,从来就不是这么的简单,没有永恒不变、放诸四海而阶皆准的准则。或许,这就是坚守「简单、迅速、便宜」的Centaur 和威盛x86 处理器发展史,带给我们的教训。