东京工业大学计算机学院的一个团队中开发了一种可移植且具有Linux功能的RISC-V片上系统(SoC),仅用5,000行Verilog代码即可实现。

“ RISC-V是一种开放的,免版税的指令集架构,已在加利福尼亚大学伯克利分校开发。使用RISC-V的处理器可以自由设计和发布,”该团队在背景技术中解释道。“因此,到目前为止,已经发布了各种处理器内核和片上系统(SoC)。但是,有一些便携式的RISC-V公共计算机系统可以运行Linux操作系统。

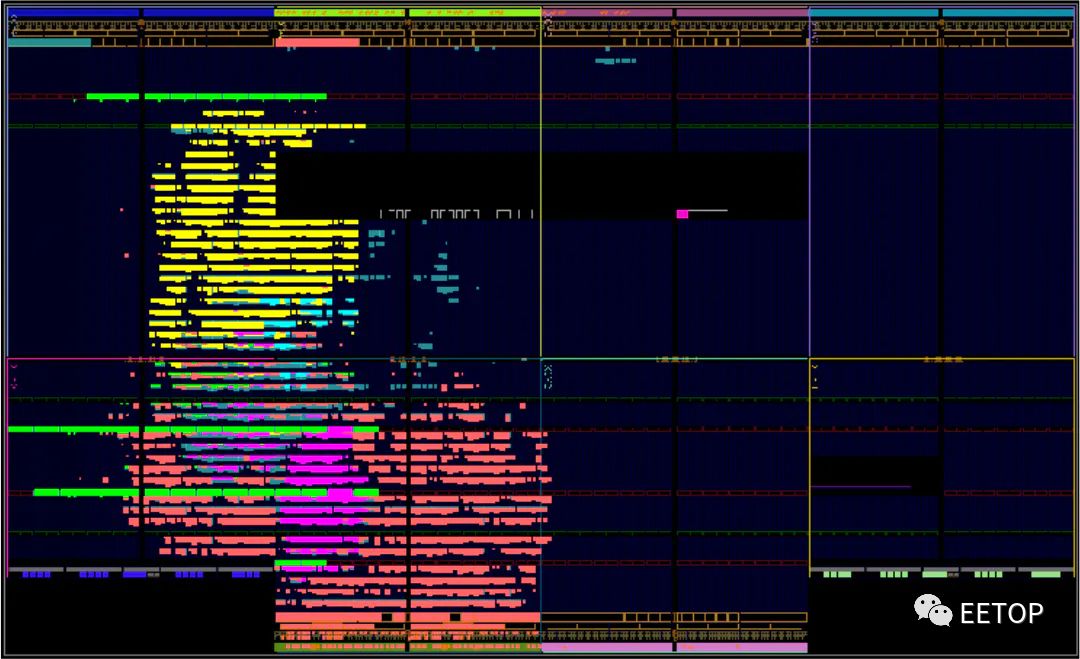

“在本文中,我们以Verilog HDL设计了针对FPGA的可移植的支持Linux的RISC-V片上系统(SoC)。该系统可以在具有较少硬件资源的FPGA上实现,并可以在低成本FPGA上实现。”

RVSoC占用了非常少的FPGA资源

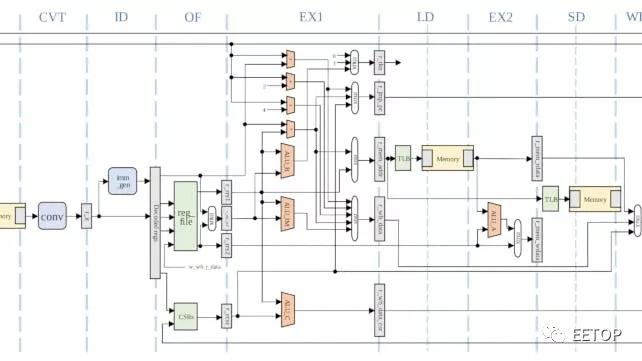

最终的设计被称为RVSoC,它实现了32位RV32IMAC指令集体系结构,并提供了带有内存管理单元(MMU)的12级流水线-对于引导Linux并非严格要求,因为内核在事件中支持手动内存映射没有可用的硬件MMU,但除了最基本的可能用途之外,它绝对是所有其他产品的必备品。尽管如此,该设计仅以5,000行Verilog HDL出现。

团队承诺:“我们计划发布设计的RVSoC的RTL代码,作为一种开放且免版税的RTL设计。” “由于RVSoC是一种支持Linux并使用少量硬件资源的系统,因此可以应用于各种用途。RISC-V的一个特点是它为计算机系统开发人员提供了扩展指令的空间。扩展性可能是特定于应用程序的加速器的基本要求,并且可以实现更专业的指令集。

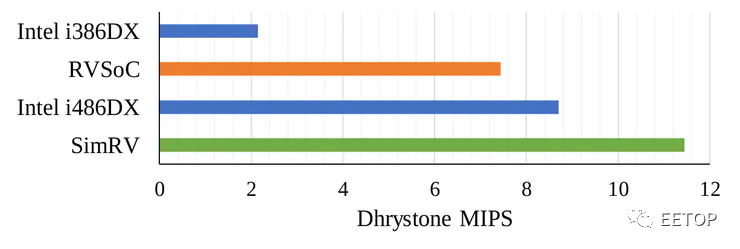

RVSoC的性能介于386和486处理器之间

RVSoC的性能介于386和486处理器之间

“通过添加独特的指令以及相关软件的开发,节省资源的RVSoC可以适用于各种加速器和特殊处理器内核的实现。RVSoC的Verilog HDL代码中的行数约为5,000,并且相对而言易于理解具有Linux功能的计算机系统的整个实现。因此,它适合用作计算机科学教育的示例计算机系统。”

该论文将在IEICE信息与系统交易杂志上发表。

论文下载

首先请在朋友圈或微信群分享此文,然后点击阅读原文进入EETOP公众号,后台发送消息:risc-v pdf,可获取下载链接。(注:前几天已分享过改论文)