EETOP也做了相关报道:一片晶圆仅做一颗芯片!史上最大芯片诞生!1.2万亿个晶体管。

业内网友依据自己的经验发表了不同的看法,现截取部分留言:

EETOP特约供稿人 Mike Liu 也发表了一篇分析文章:《史上最大芯片:Cerebras WSE,卫星还是创新》,(首发与Mike Liu的公众号:MikesICroom)

正文如下:

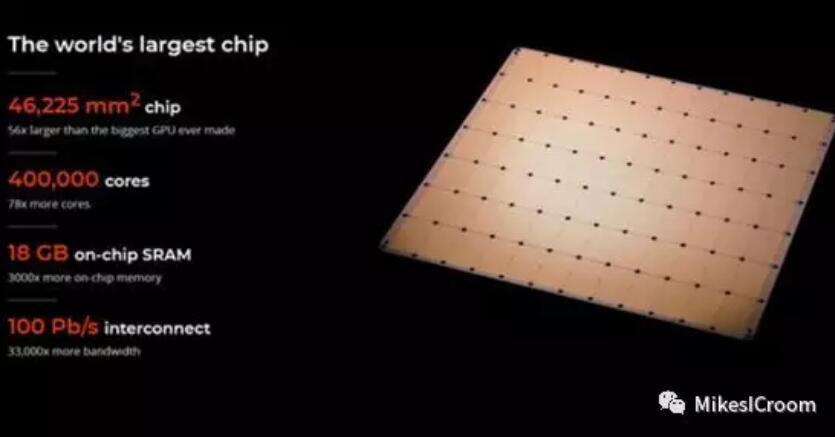

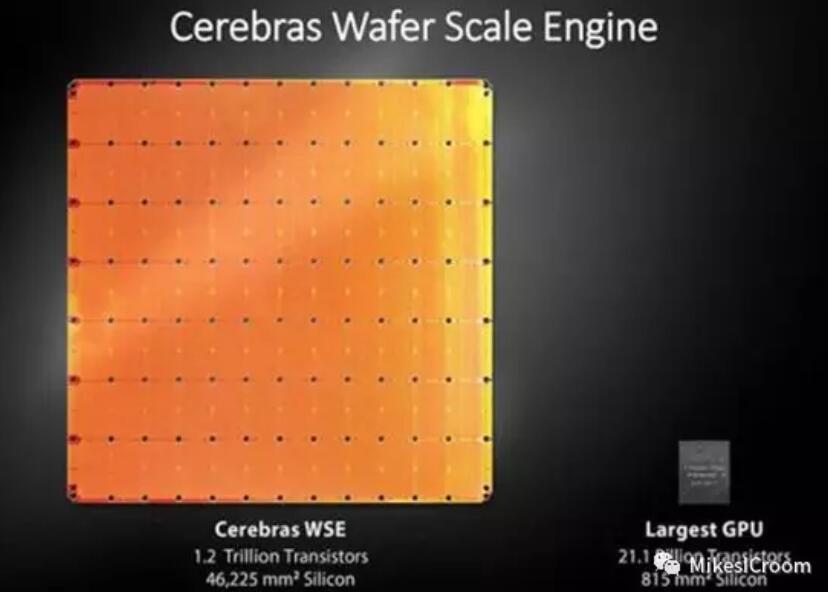

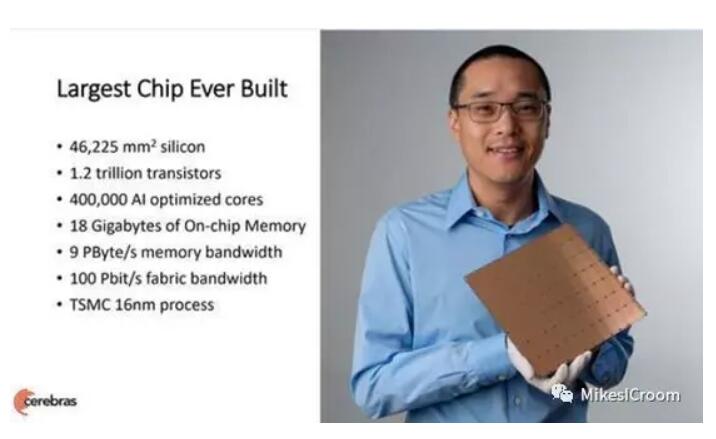

看下尺寸,1.2万亿晶体管,核心面积64225mm2,18GB 片上SRAM!真是亮瞎了我的钛合金眼。可能有的人对这个数字不是很敏感,对比一下就更明显了。NVIDIA的GPU大核心GV100的面积是815mm2,这是服务器端最大的单芯片,对比WSE是它的56倍之多!

WSE还有一些别的特性,主要面向AI领域,单芯片集成了40万个运算核心(PE),片上18GB的SRAM,注意是SRAM,类似我们通常所说的Cache,目前主流高端处理器的Cache也不过512KB,这个片上SRAM比大多数芯片的片外存储(DDR)都大。带宽100Pb/s (1Pb=1000TB)。这基本上比现有的芯片的相关参数高了一个单位(3个数量级)。

WSI(Wafer-Scale Integration)并不是一个很新颖的技术,上世纪80年代,就有人做过类似的尝试。结果显而易见了,至今为止没有任何一款商用,甚至学术型的产品问世。今天Cerebras的WSE(Wafer Scale Engine)算是开创性的产品。

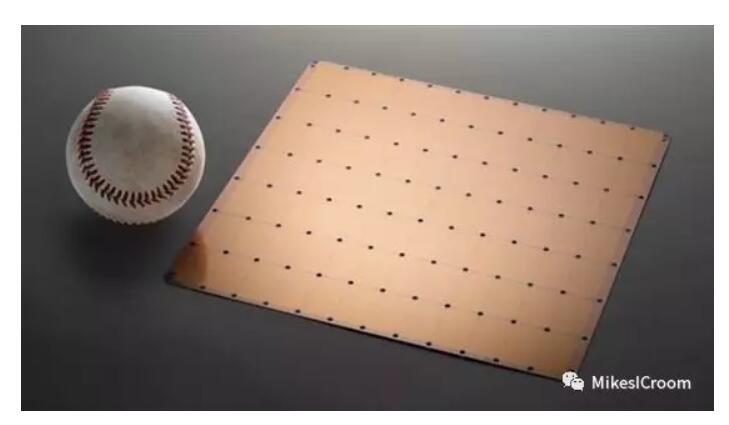

WSI的优点是显而易见的,可以避免多芯片之间通信带宽的限制,直接使用芯片上的高速大位宽的直连线,获得数千倍的带宽提升,同时更多的片上存储可以极大的减少对内存的依赖。这么大的优点,为什么至今没有商业成功的案例呢?主要问题有3点。第一是良率。芯片制造的缺陷随着芯片面积的增长而大幅增加,即便有足够的容错设计,这么大的芯片最终能够运行的部分能占总面积的百分比可能也不会十分理想,这方面Cerebras并没有给出具体的数字。第二是功耗,在后摩尔时代,大芯片设计一直都被散热问题所困扰,大多数的系统都不能完全工作在最高频率,常常采用全部核心低速运行,或者单个核心高速运行,其他进入低功耗的方式,称为“Dark silicon”。一块大核心GPU的功耗达300W,其核心面积仅815mm2,可我们买到的GPU卡有多大大家都知道,那么大的板卡,很大部分都花在散热,供电等方面。Cerebras的芯片是GPU的56倍,功耗高达15KW,比一般家庭全屋的电器功率都大,这么高的能量在仅有ipad大小的芯片上散发出来是非常恐怖的。有文章说采用水冷,我表示怀疑,不知道液氮冷却能不能供给的上。最后是量产,裸片产出到量产化之间还有很长的距离要走,如何在这么小的面积上给芯片供电,保证电压的稳定,以及大尺寸封装和系统集成的方式,ipad大小的WSE芯片说不定系统有一个房子那么大,对于这些问题Cerebras都没有明确的答案。

一个带有科学家神秘笑容的图片总是能给人以科学的神圣感。我丝毫不怀疑Cerebras的芯片可以跑起来,不但是简单的点亮,而且是跑复杂的AI程序。但我对它能够实现宣称的数万倍的性能提升,1/10的成本以及芯片大规模量产的能力抱怀疑态度。通过大幅度的降频是可以让芯片的功耗控制在可承受的范围之内,然而性能的降低也会是明显的。芯片制造的缺陷带来部分芯片功能的失效在WSE上可能是非常显著而难以简单容错规避的。整个散热,供电,封装的重新设计使得系统成本高昂,会抵消掉集中式芯片所节省的成本。同时单芯片数十千瓦的运行热量会极大的降低芯片的寿命,而一个非常小的部分的损坏就会造成整个芯片的失效,这也是系统成本之一。

通常来说我对新兴事物的接受度还是比较高的,而Cerebras的WSE并没能给我很有说服力的证据。换个例子就能明白为什么会持怀疑态度。现在大家都在建造100层的摩天大楼,一直没有太高的突破。突然有人说我建造了一个1000层的大楼,称为小区式高楼。强调这么高的大楼,非常节省土地面积;数个电梯就能完全连接所有层,不需要传统小区地面道路的连接;1000个单层模块直接堆叠,模块化构建;高层获得非常好的风景,等等。而一直不提如何解决超高层对于地震和火灾的防护,如何解决电梯有效运行的问题,1000层甚至可以感受到地球自转的影响,如何克服;达到设计寿命后如何拆除等问题, 这栋楼,我是不敢住的。对比Cerebras一直强调的超级计算能力,40万个优化AI内核,18GB的片上缓存,超高带宽的独特通信结构,不知道读者是否有所感受。很希望我的疑虑是错的,Cerebras能在接下来的时间里证明自己的设计,这就是真的开创了集成电路设计的新时代。