日志

ARM平台嵌入式Linux下SPI设备连接

|

在嵌入式ARM平台设备上,经常有在一个SPI

bus上面挂接一个或者多个SPI设备的需求,由于挂载一个设备的情况比较简单,本文主要就在嵌入式Linux环境下挂载多个SPI设备进行说明。

本文所采用的硬件为Toradex 公司Colibri VF61计算机模块和开发载板,核心为Cortex-A5和M4异构双核,这里A5运行Toradex官方发布的Embedded Linux BSP V2.5,M4核心这里不做使用。

本文涉及Toradex发布Embedded Linux源码下载,Device Tree 定制编译,相关操作请参考下面文章,本文不做赘述。

http://developer.toradex.com/knowledge-base/build-u-boot-and-linux-kernel-from-source-code

http://developer.toradex.com/device-tree-customization

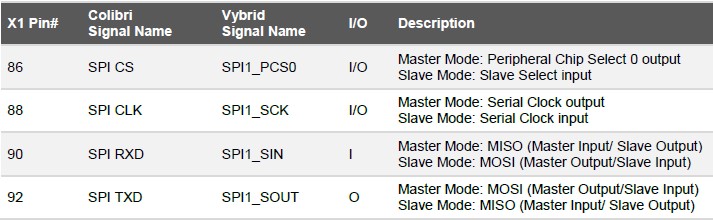

Colibri VF61最多可以提供4路SPI bus,不过只有SPI1为系列兼容,因此这里就只使用SPI1,根据手册,其硬件管脚定义如下:

1). 在连接一个SPI 设备情况下,则只需要硬件对应连接上面管脚即可,Device Tree默认也已经设置好无需修改,然后按照下面文档说明操作即可

http://git.toradex.com/cgit/linux-toradex.git/tree/Documentation/spi/spidev_test.c?h=toradex_vf_4.1

2). 在连接多个SPI设备情况下,则主要问题是需要多个Chip Selection片选信号,这里有两种解决方案,一种是硬件CS管脚,VF61 SPI1通道除了默认的CS0,还提供额外的4个CS管脚,不过默认为其他功能;另外一种方式为直接使用GPIO作为CS管脚,下面对这两种方式分别说明:

a). 采用硬件CS管脚

除了默认的SPI1_CS0,VF61还提供了额外4个CS管脚SPI1_PCS1, SPI1_PCS2,

SPI1_PCS3;不过由于不是默认功能,需要在Device Tree中修改,下面以除了默认的CS0,再添加一个设备采用SPI1_PCS1作为CS信号为例说明。

./ 根据VF61手册,有连个管脚可以提供SPI1_PCS1功能,我们选择默认功能为GPIO的SODIMM Pin79来设置为SPI1_PCS1。

//修改&iomuxc -> vf610-colibri, 从’pinctrl_additionalgpio’里面删除对应GPIO管脚

pinctrl_additionalgpio: additionalgpios {

fsl,pins = <

VF610_PAD_PTC4__GPIO_49 0x22ed

……

>;

};

//在’pinctrl_dspi1‘中添加对应的管脚

pinctrl_dspi1: dspi1grp {

fsl,pins = <

VF610_PAD_PTD4__DSPI1_CS1 0x33e2

>;

};

//最后再为新的slave device添加slave node

&dspi1 {

spidev1: dspi@0 {

compatible =

"spidev";

reg = <0>;

spi-max-frequency =

<50000000>;

};

Spidev2: dspi@1 {

compatible =

"spidev";

reg = <1>;

spi-max-frequency =

<50000000>;

};

};

b). 采用GPIO作为CS管脚

参考文档请见这里,下面是一个简单举例

./ 修改Device Tree SPI master

node 参数

//增加cs-gpio 属性,定义GPIO CS管脚或者GPIO和硬件CS混合,如下面所示SPI1_PCS0和另外三个GPIO混合组成新定义的CS组合

&dspi1 {

cs-gpios = <0> <&gpio1 14 0> <&gpio1 15 0>

<&gpio1 16 0>;

};

这样重新定义的CS片选组合为4个,顺序如下:

CS0: SPI1_PCS0

CS1: &gpio1 14

CS2: &gpio1 15

CS3: &gpio1 16

./ 修改&iomuxc -> vf610-colibri,将所需的CS GPIO从GPIOs

Pinctrl删除,并加入SPI1 Pinctrl。

//从’pinctrl_additionalgpio’里面删除上面三个GPIO管脚

pinctrl_additionalgpio: additionalgpios {

fsl,pins = <

VF610_PAD_PTC1__GPIO_46 0x22ed

VF610_PAD_PTC2__GPIO_47 0x22ed

VF610_PAD_PTC3__GPIO_48 0x22ed

……

>;

};

//然后再添加到’pinctrl_dspi1‘

pinctrl_dspi1: dspi1grp {

fsl,pins = <

VF610_PAD_PTC1__GPIO_46 0x33e2

VF610_PAD_PTC2__GPIO_47 0x33e2

VF610_PAD_PTC3__GPIO_48 0x33e2

>;

};

//最后再为每个slave device添加slave node

&dspi1 {

spidev1: dspi@0 {

compatible =

"spidev";

reg = <0>;

spi-max-frequency =

<50000000>;

};

Spidev2: dspi@1 {

compatible =

"spidev";

reg = <1>;

spi-max-frequency =

<50000000>;

};

……

};

3). 将上述修改好的Device Tree 文件重新编译后部署到VF61设备里面,就完成了多个SPI设备挂载,可以在应用中使用了。

a). 编译部署除了本文一开始提到的文章,也可以参考这里

b). Embedded Linux 下 SPI设备调用请参考这里

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网