12月3日,武汉新芯集成电路制造有限公司(下称“武汉新芯”)对外宣布称,基于其三维集成技术平台的三片晶圆堆叠技术研发成功。

武汉新芯的晶圆级集成技术可将三片不同功能的晶圆(如逻辑、存储和传感器等)垂直键合,在不同晶圆金属层之间实现电性互连。与传统的2.5D芯片堆叠相比,晶圆级的三维集成技术能同时增加带宽,降低延时,带来更高的性能与更低的功耗。

武汉新芯技术副总裁孙鹏表示,三维集成技术是武汉新芯继NOR Flash、MCU之外的第三大技术平台。武汉新芯的三维集成技术居于国际先进、国内领先水平,已积累了6年的大规模量产经验,能为客户提供工艺先进、设计灵活的晶圆级集成代工方案。”

武汉新芯自2012年开始布局三维集成技术,并于2013年成功将三维集成技术应用于背照式影像传感器,良品率高达99%,随后陆续推出硅通孔(TSV)堆叠技术、混合键合(Hybrid Bonding)技术和多片晶圆堆叠技术。

晶圆级的三维集成技术为后摩尔时代芯片的设计和制造提供了新的解决方案,在对带宽、性能、多功能集成等方面有重要需求的人工智能和物联网领域拥有颇为广泛的应用前景。

关于武汉新芯

武汉新芯成立于2006年,由省市区三级政府集体决策投资107亿,建设中部地区第一条12英寸集成电路生产线,2008年建成投产。2016年,在武汉新芯基础上,紫光集团、国家集成电路产业投资基金、湖北集成电路产业投资基金、湖北省科技投资集团共同出资组建长江存储科技有限责任公司,武汉新芯整体并入长江存储,成为长江存储全资子公司。

附:晶圆级三维集成关键技术简析 (整理自:IC春秋)

近几十年来,随着微电子技术的发展,高性能、小外形、低成本的电子产品已成为市场的基本需求。集成电路上可容纳元器件的数目是符合摩尔定律预测的。但是近年来传统的集成电路增长趋势开始和摩尔定律的理想模型出现了差别。随着手机和各种电子产品的快速发展,芯片的功能也越来越复杂,芯片上集成晶体管的数目也随着越来越多,同时也引起了集成电路体积的增大和功耗增高。当晶体管的栅极长度和氧化层厚度都接近物理极限时,二维集成最终将走到道路的尽头。

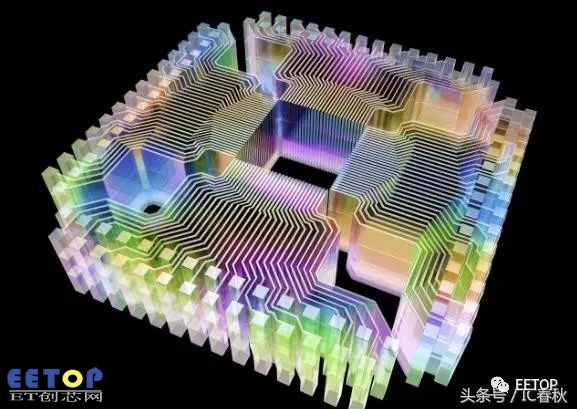

遵循摩尔定律的三维集成技术可以作为解决上述问题的方案。三维集成方法的概念是基于集成电路的新位置:Z 轴。这意味着晶片位置不再局限于 X-Y 二维平面上了。因此,我们可以实现更大密度的集成电路堆叠,以缩短互连,也减少了可见表面,从而缩小晶片的尺寸和提高晶片的效率,进而提高了应用范围。此外,三维集成方案可以结合不同的集成电路本身的最佳工艺,避免了效率低和产量低的问题。

虽然三维集成有许多优点,但它的材料选择,热驱动的物理设计和测试方法更是当前要解决的问题。

晶圆级三维集成是一个新的概念,利用许多高级技术实现电路密度的增加和体积的缩小。其中,对准和键合技术、晶片减薄技术和硅基板穿孔技术(TSV)是三项最为关键的技术。

一、对准和键合技术

对准不精确导致电路故障或可靠性差。因此,对准精度的高低主导了晶片接触面积和三维集成电路堆叠的成品率。对准精度与对准器和对准标记有关。也受操作员个人经验的影响。

铜被广泛用于标准 CMOS 制造中。因此,铜是三维集成中连接两个设备层或晶圆的最好的选择。铜晶圆键合的原理是让两个晶片接触然后热压缩。在键合过程中,两个晶片的铜层可以相互扩散以完成键合过程。集成的质量与晶圆表面的清洁度和键合时间有关。

一般来说,温度至少300~400℃才能完成铜键合。可以根据其界面的形态来确定键合质量。为了获得好的铜晶片键合的结果,条件是400℃加热30分钟,接着400℃氮气环境退火30或60分钟。虽然高温和高压可能会提高键合质量,但相应的成本和设备的损耗也成为需要关注的主要问题。因此,在较低的温度和压力下的键合方法是三维集成的主要目的。

二、晶片减薄技术

三维集成技术极大的增大集成电路密度的同时也带来了散热困难的问题。由于硅基板和金属材料之间存在电阻,当通过电流时,会有发热效应。而热量不断的产生会使芯片的背面产生一种内应力,而内应力较大时会使芯片直接破裂,加快了芯片的损坏速度。通过使用芯片减薄工艺,不仅可以有效的降低集成电路的内阻,优化各芯片的散热性能,还提高了电路的稳定性和缩小了芯片体积,更符合集成电路整体小型化的趋势。

三、硅基板穿孔技术(TSV)

硅通孔的概念是由诺贝尔奖得主 William Shockley最早提出来的,硅基板穿孔(TSV)在晶片与晶片之间、晶圆与晶圆之间制作垂直导通,实现晶片之间互联的技术。该技术能够使晶片在三维方向上堆叠的密度达到最大,因此不同基板的晶片通过硅基板穿孔技术进行立体堆栈整合后,不仅可缩短金属导线和联机电阻,更能减小晶片的体积。

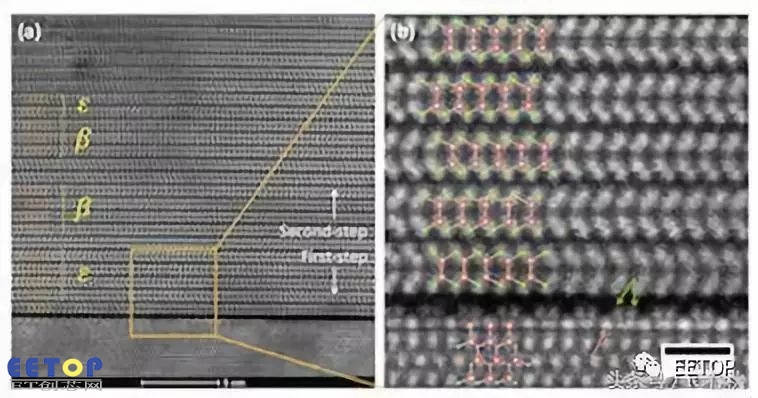

(1)先通孔工艺。先通孔工艺是在 CMOS 器件制作之前,在空白硅片上完成通孔制作和导电材料的填充。在这个方案中,填充材料不能是金属,比如铜。此外,由于在这个阶段还没有金属互连,先通孔工艺的纵宽比是小于后通孔工艺的。

(2)后通孔工艺。后通孔工艺是在 BEOL 完成后,在 CMOS 即将制作完成和但还未进行减薄工艺处理的硅片上预留的空白区进行钻蚀通孔。该技术包括钻孔和填充过程,为了不破坏设备和电路,应在低于热预算的温度环境下制作。

(3)TSV 工艺流程。整个硅基板穿孔过程可大致分为两个部分:第一部分是通孔的蚀刻,第二部分填充通孔。硅基板穿孔的蚀刻难度取决于减薄后的晶圆的厚度。当目标蚀刻深度太深,通孔的开口尺寸通过需要相应地扩大,这也导致晶片尺寸的增加。

填充材料也是需要考虑的问题。铜、钨和多晶硅是典型的硅基板穿孔填充材料的选择。在这些材料中,铜和钨的只能用在后通孔方案中,而多晶硅可用于先通孔和后通孔方案中。铜是一种工艺兼容材料,残余应力少,电子性能好,但难以填充高纵宽比的通孔。相反,钨很容易填充到高宽比的通孔,但其残余应力高是一个很大的问题。多晶硅可用于硅基板穿孔的先通孔方案中,但它的电阻比金属高。考虑到每种材料的优点和缺点,硅基板穿孔填充材料的选择对三维集成具有重要意义,特别是对于晶圆级三维集成。

TSV 制备具体工艺步骤为:

(1)通过研磨和蚀刻工艺将晶片减薄。

(2)通过激光熔化法或反映离子刻蚀法在晶片上制备通孔。

(3)使用等离子体化学气相沉积法(PECVD)在通孔侧壁制造绝缘层。

(3)去除通孔底部的衬底氧化层,使金属层暴露出来。

(4)运用电化学反应往通孔中填充铜金属。

(5)通过化学机械研磨和刻蚀工艺去除晶片表面上的铜金属。

四、三维集成中的材料、晶圆堆叠方式

受到传统方法的限制,集成电路不能像以前那样较为容易地集成许多晶体管到一块集成电路芯片之中。三维集成技术提供了一个能够延续摩尔定律的全新版本概念。而三维集成中 TSV 互联技术可以让芯片在垂直方向上直接连接,大幅度提高了集成密度,缩小了集成电路尺寸。然而三维集成也面临着诸多技术性的挑战,如材料选择、散热问题和测试方法等。

下面接着介绍一下关于三维集成中的材料、晶圆堆叠方式等情况。

1、晶圆类型分类

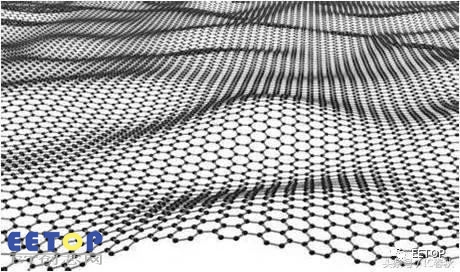

体硅: 体硅是晶圆级三维集成中最常用的晶圆类材料。原因不只在它的成本,还有成熟的制作过程。即使当其他种类的晶片被用作顶部晶片时,底部晶片通常仍然是体硅晶片。

绝缘硅(SOI): SOI 晶片表面具有覆盖的氧化层,可以被均匀地减薄,因为氧化层起到阻碍蚀刻的作用。蚀刻过程可采用机械研磨、湿法刻蚀、干法刻蚀。最重要的是,因为最终的厚度可以均匀地减薄,使用SOI可以实现高密度的三维集成。SOI 结构可有效的避免闩锁现象。然而,堆叠结构的防静电能力可能会降低,并且密集的设备层还有潜在的散热问题。

玻璃: 在三维集成中的玻璃晶圆通常用于放置顶部晶片。因此,用于此目的的玻璃晶圆称为载体晶圆。当玻璃暂时附着顶部晶圆时,可以对顶部晶圆的衬底减薄。在被减薄后的晶圆键合在底部晶圆后,移除玻璃。玻璃晶圆的透明特性也为良好的键合结果提供了帮助。对于各种类型的晶圆堆叠,我们应该注意到,如果任何带电体接触或甚至接近晶圆,晶圆都可能会产生感应电荷。在两个晶圆的堆叠过程中,只要一个晶片充电,静电放电事件都有可能发生。

2、晶圆堆叠方式

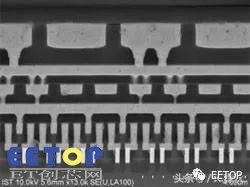

根据两晶片堆叠方向,分为两种不同的堆叠晶片方式:面对面和面对背。晶片堆叠方向的影响是非常巨大的,将会影响到电路的对称性,制造的难度,电容的互连等方面。这两种堆叠方法均已被应用在三维集成应用中。甚至两种堆叠方法的共同使用也是存在的。

面对面堆叠法。对此类型晶片来说,两个晶片的金属层(面部)通过 TSV 相连在电路中。从制造技术的角度来看,这种集成方式易于投入应用,并且不需要额外的处理晶片。但是需要考虑到晶圆到晶圆的对称性问题。这意味着在设计顶部晶片时,需要对电路进行镜像操作。同时,还要考虑到两个晶片的对称性和对准的位置。

面对背堆叠法。面对背型晶圆,一个晶片的金属层(面部)通过 TSV 和另一个晶片的衬底(背部)相连,上面的晶圆(上晶圆或顶部晶圆)应减薄。与面对面型相比,这种方法增加了过程的复杂性。然而,晶圆到晶圆的对称性问题就不存在了。而且需要处理的晶片是显而易见的,并且晶圆也足够薄,校准过程变得容易得多。

晶圆级三维集成的优势和挑战不同于传统的二维封装技术,晶圆级三维集成提供了更多的优势,一是多个不同器件在垂直方向相互连接,缩短互连,也减少了可见表面,从而缩小晶片的尺寸,增大了集成密度;二是各芯片之间连线的缩短,加快了芯片处理速度;三是低阻容带来的低功耗和更高的运行速度;四是整体尺寸小,降低了集成成本。然而,高集成密度带来的散热问题、对齐方式、材料的选择、三维设计 CAD 工具、设计和测试方法等挑战,仍然需要克服。

随着工业界和学术界的努力,有着小外形、高密度、低成本等诸多优势的三维集成技术,在高性能和低功耗的下一代集成电路革命中,必定具有非常广阔的应用前景。