日志

Questions about STA and Report

| ||

(1) What's "time borrowed from endpoint" and "time given to startpoint"?

Link:http://www.xilinx.com/support/answers/56877.html

Time borrowed from endpoint:

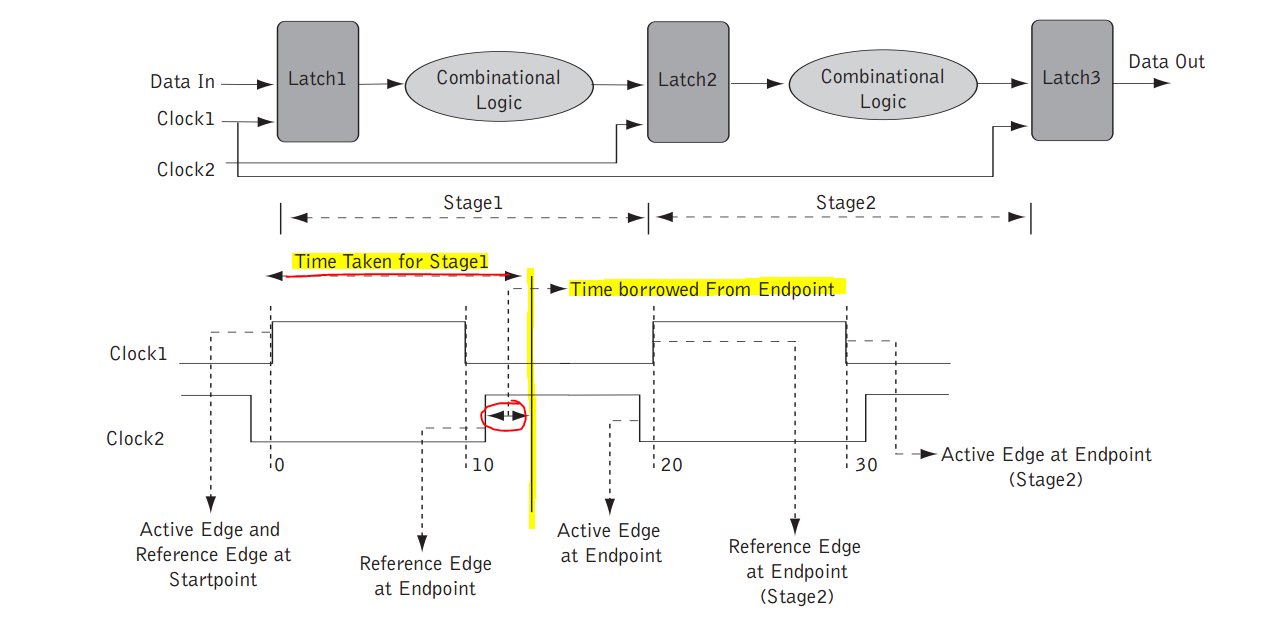

In a path where

the endpoint is a latch device, the borrowing time refers to the time

from the clock cycle of the latch that is expended by the previous

synchronous device. Or in other words, given that a latch is active

during a whole clock pulse, if the path between the previous synchronous

device and the latch produce a variation of the capturing data at the

latch after the latch is enabled, this will produce a borrowing time

from the latch.

For example, in the following two-stage latch base design, the combinational logic block between Latch1 and Latch2 may have more delay than the delay between Latch2 and Latch3. To resolve this discrepancy, the first stage can borrow time from the second clock cycle. In this event, the second clock cycle is left with less time to accommodate the combinational logic block between Latch2 and Latch3

Time given to startpoint:

The above picture shows clearly the meaning of this parameter. It would be the path delay from the synchronous element until the latch

(2) What's "time borrow from startpoint" and "time given to endpoint"?

(3) What's clock latency difference?

The clock rising and falling edge propagate have different delay.

If the (0,468) delay to (10, 488), then the clock latency difference is 10.

a=(10-0=10), b=(488-468=20), clock latency difference=b-a=10.

(4) Why sometimes the "actual clock borrow time" is a negative value?

Because the CK -> Q arc and D -> Q arc have different values, when D -> Q(200ps) and CK -> Q(100ps), when D change at before CK open with 50ps, then the actual borrow time is -50ps(100-200+50)

2. Question about STA

(1) What's "Delay based Design"?

It's different with "Clock based Design" and It's use delay to generate the skew between two FFs or latchs.

(2) How to do Setup/Hold violation check?

1st latch clock sequence {1o1,1c1,1o2,1c2,1o3,1c3}, 2nd latch clock sequence {2o1,2c1,2o2,2c2,2o3,2c3}, and have delay between those two latch.

setup: 1o1 data to 2o1 clock

hold: 2o1 data to 2c1 clock

(3) How to check latch setup and hold violation?

1) Check two latch setup(1st latch and 2nd latch);

2) 1st latch(open edge) launch the data;

3) Find the close edge of the 2nd latch;

4) Move to the forward open edge of the 2nd latch to check setup.

(4) What's CRPR(clock reconveregence pessimism removal)?

If data and clock pass through the same path, the data path use the max delay to calculate, while the clock path use the min delay to calculate. It's impossible use two delay value to one common path.

In the common path, CRPR_value=data_path_delay - clock_path_delay, then in the reports, CRPR_value was added to the clock path.

/2

/2

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网