日志

一个小时搞定VCS安装

| |

当今,业界领先的设计人员在从事最先进的设计工作时为其验证环境选择 Synopsys VCS© 功能验证解决方案。 实际上,绝大多数的 32nm 及以下制程的设计均采用 VCS 进行验证。 全球顶尖的 20 家半导体公司大多采用 VCS 作为其主要验证解决方案,VCS 可提供高性能仿真引擎、约束条件解算器引擎、Native Testbench (NTB) 支持、广泛的 SystemVerilog 支持、验证规划、覆盖率分析和收敛以及完整的调试环境。

VCS 持续地引领众多业内首推的创新技术,现已为应对当前 SoC 的挑战和复杂性做好充足准备。 VCS 可提供约束随机测试平台、SoC 优化编译流程、覆盖率、断言、规划和管理等特性,灵活性和功能性兼具,这些对当前 SoC 设计和验证团队的成功至关重要。

个人安装synopsys常见问题

Notes:

- gcc版本不匹配

- linux系统缺少对应库

- 软件包多而杂,难以找到正确安装包

- 不熟悉linux系统

一、系统环境安装

- 虚拟机安装

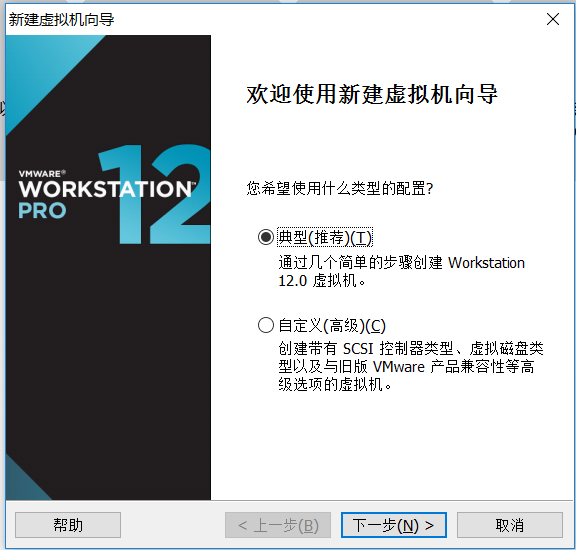

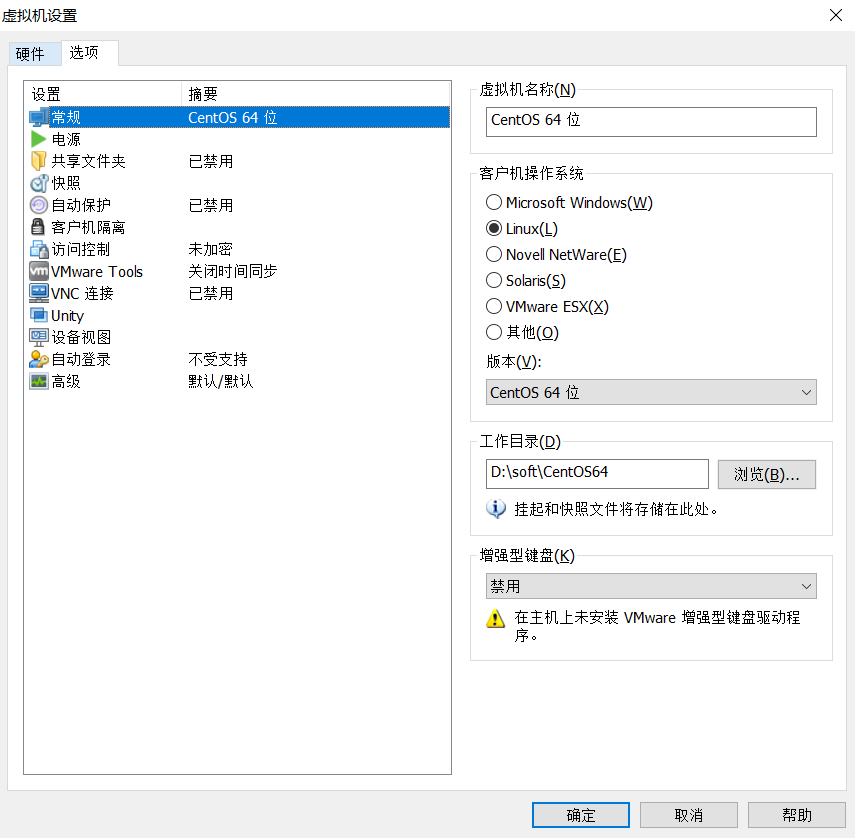

1.1选择任意版本VMware

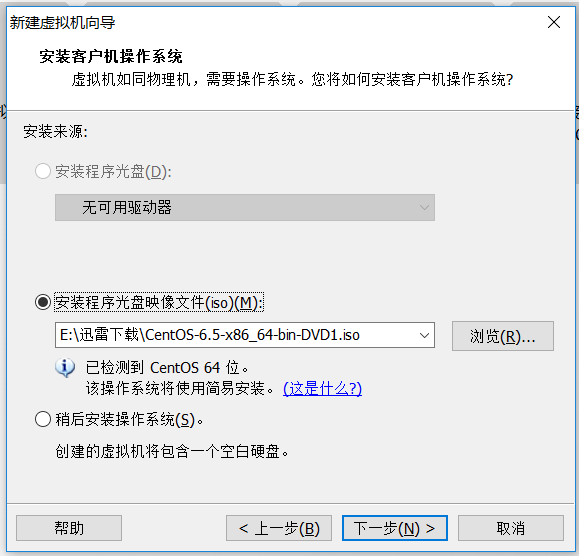

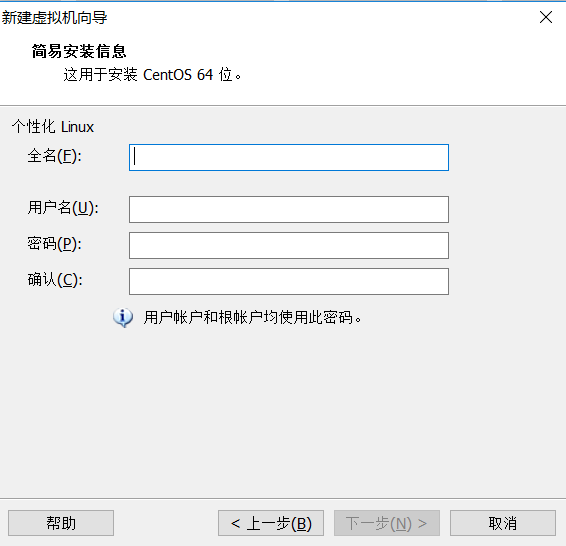

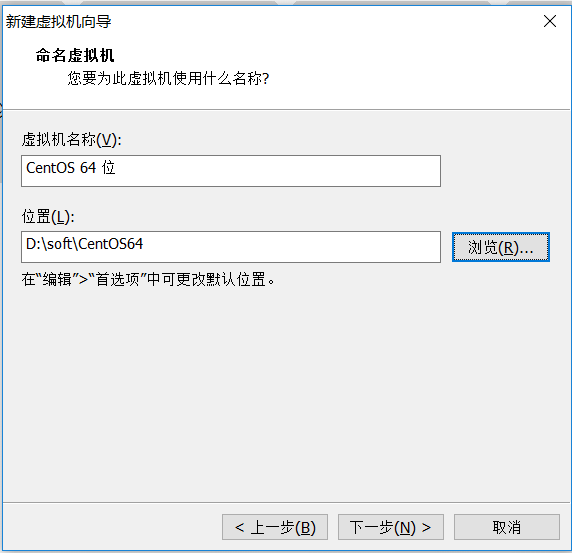

1.2Linux系统安装

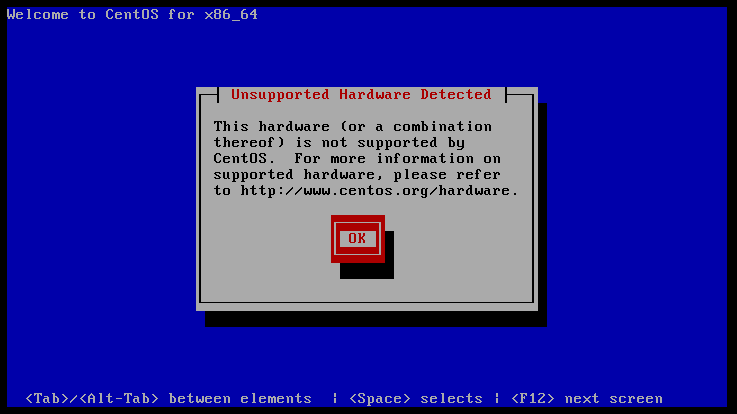

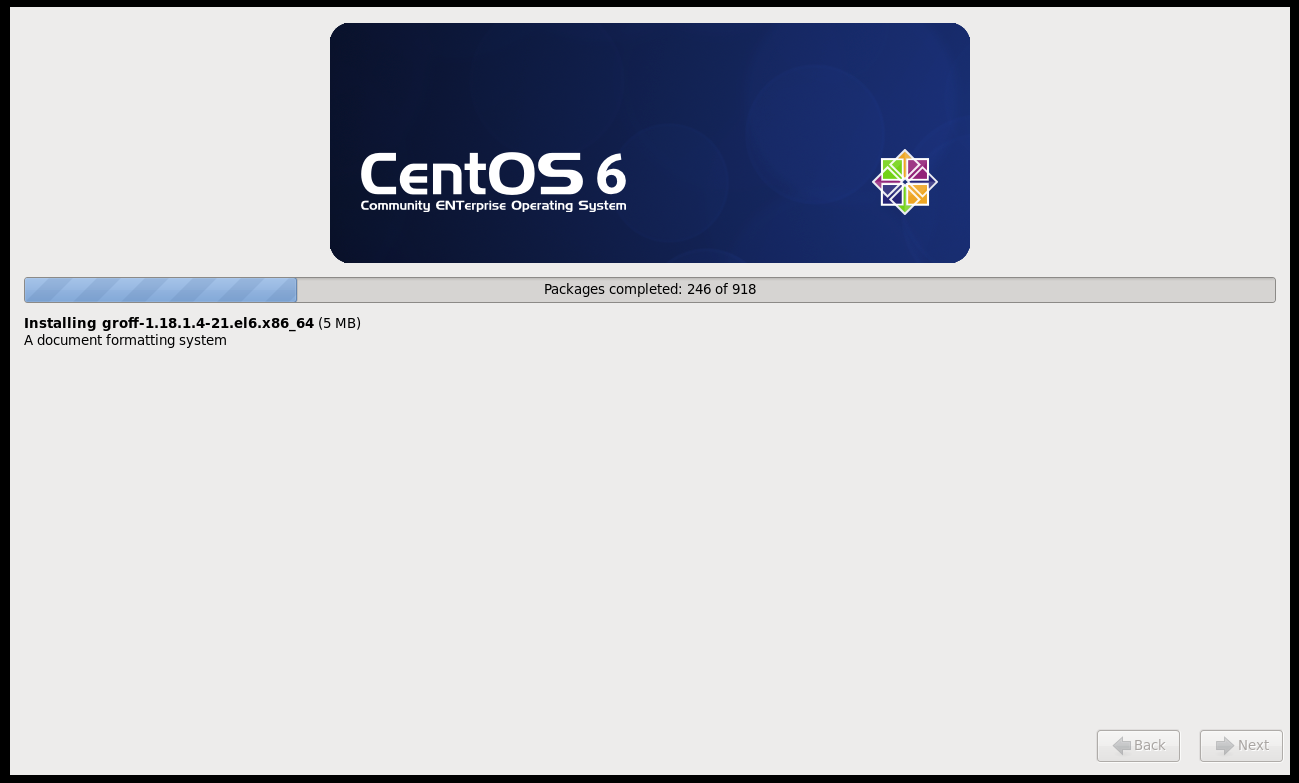

(1)选择CentOS 6.5版本64位系统(现在电脑普遍64位,在此不对32位介绍,区别是Linux库安装差别,此linux版本 gcc版本为4.4.7,在centos下省去gcc降级步骤)

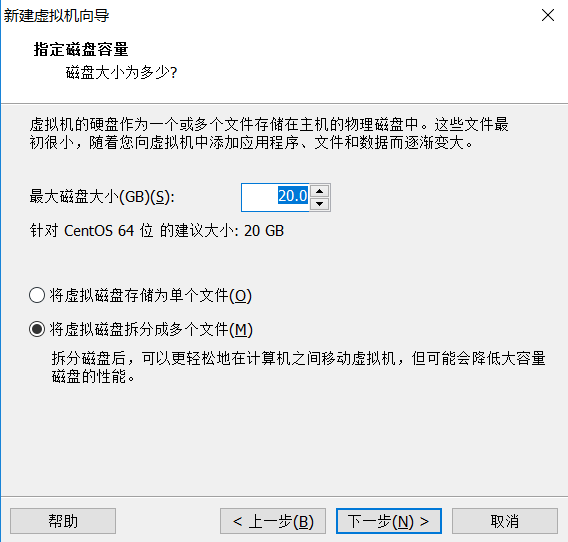

最大磁盘大小建议30G以上,应为synopsys整套软件还是比较大的,即便之前前段需要的也要站10G+的空间,不建议先设成2G,后期再扩容,这样加的的容量会以独立磁盘的形式出现,个人认为不是很方便。

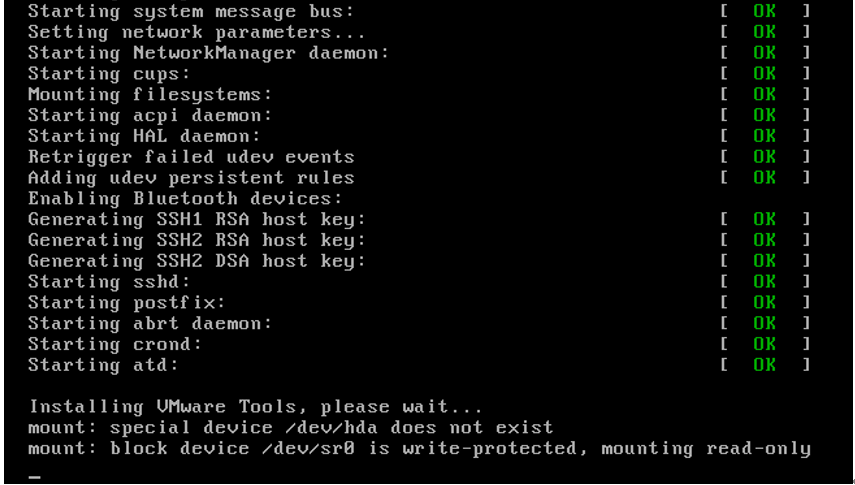

CentOS 6.5版本自带VMware Tools包,在安装系统时已经安装完毕,不需要再单独安装。

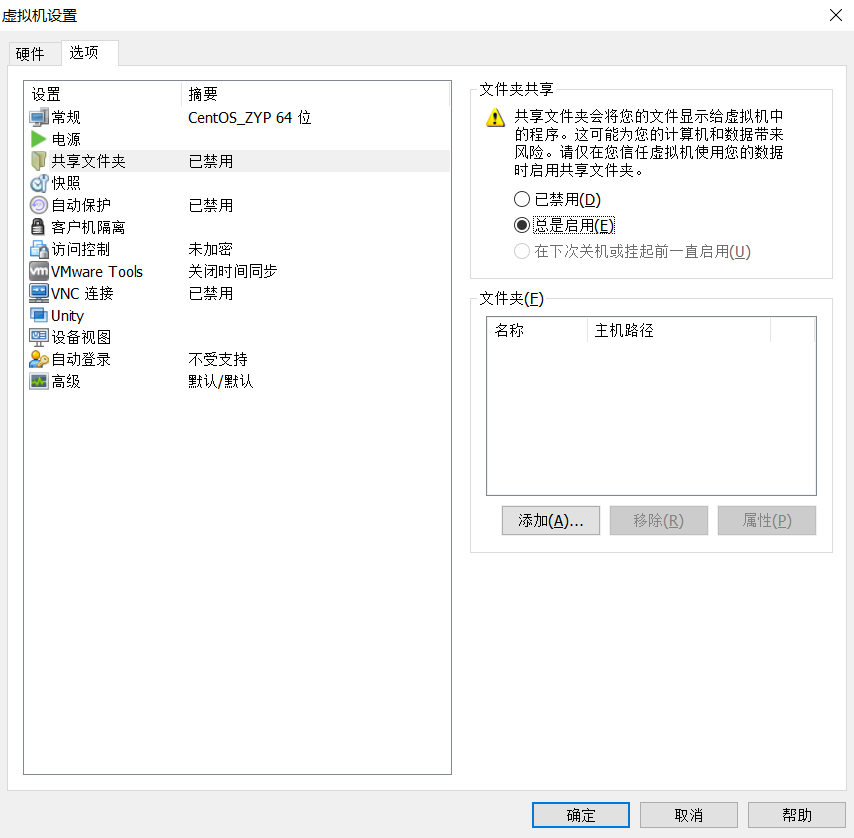

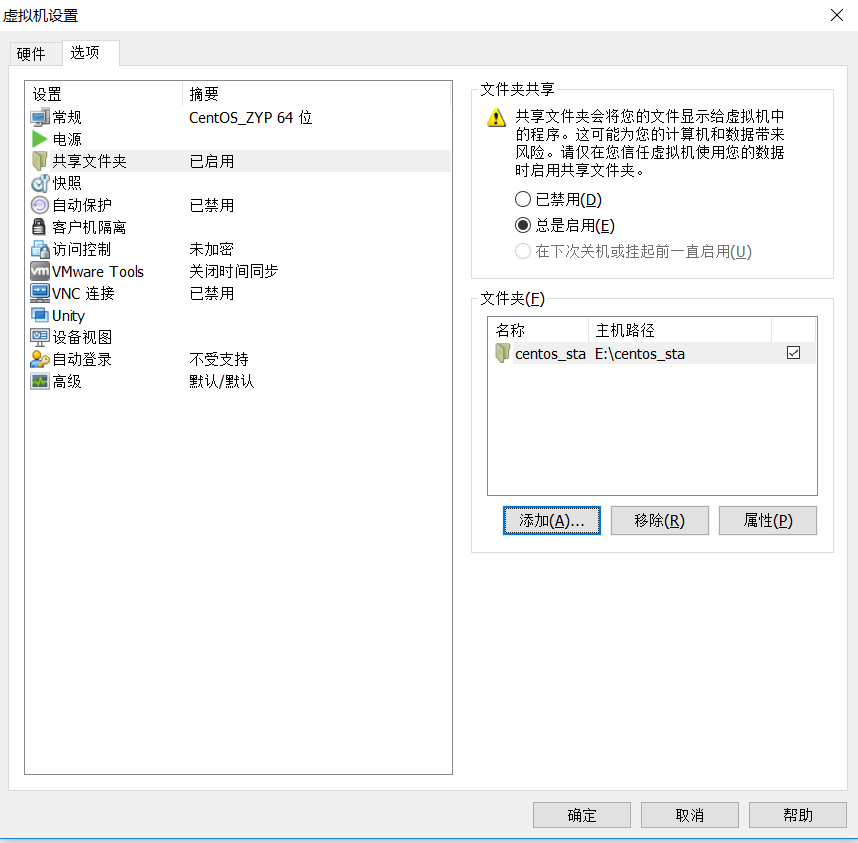

设置共享文件夹

二、系统缺少相应库安装

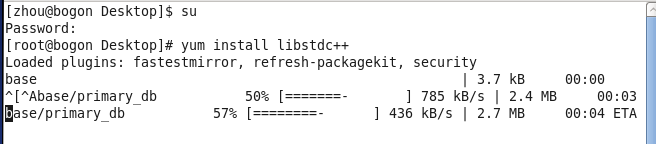

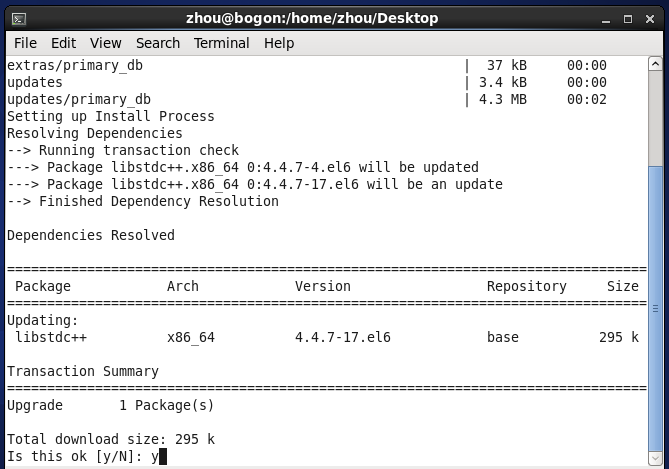

1、yum install libstdc++

2、libmng.so.1问题

yum install libmng

3、缺少so.2

yum install libtermcap.so.2

yum install compat-libtermcap-2.0.8-49.el6.x86_64

glibc-devel.i686 libstdc++-devel.i686

三、安装VCS

- 软件准备

下载;Installer http://pan.baidu.com/s/1i5NZMg1#list/path=%2F

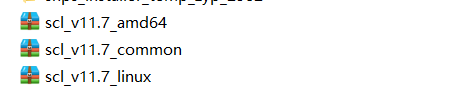

下载:scl http://pan.baidu.com/s/1jIqN158

不用再解压

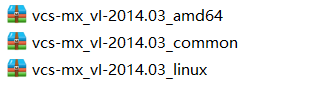

下载:vcs http://pan.baidu.com/s/1nvK33j7 (备注,此链接下载是分散包,一共三套,分开解压)解压完如下图,到此不用再解压

(备注:vcs 和 scl 安装时选到文件夹即可,)

(备注:这些软件暂时存放在共享文件夹里方便操作)

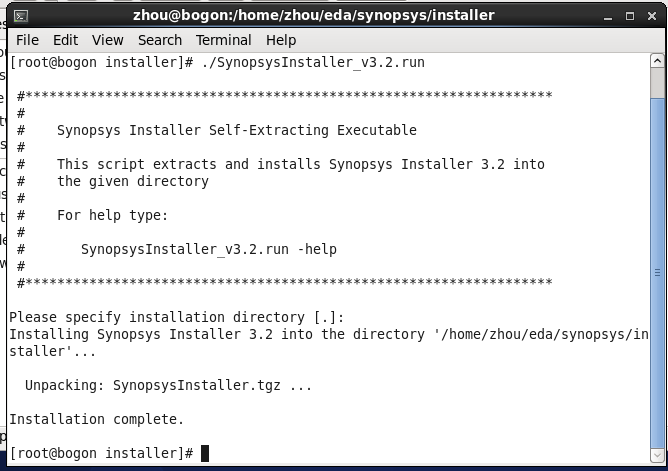

- SynopsysInstaller 安装

在此选的是3.2版本,其他也可以。

下载软件包,放至共享文件夹中,共享文件夹在/mnt/hgfs下

第一步:解压installer

第二步:运行SynopsysInstaller_v3.2.run

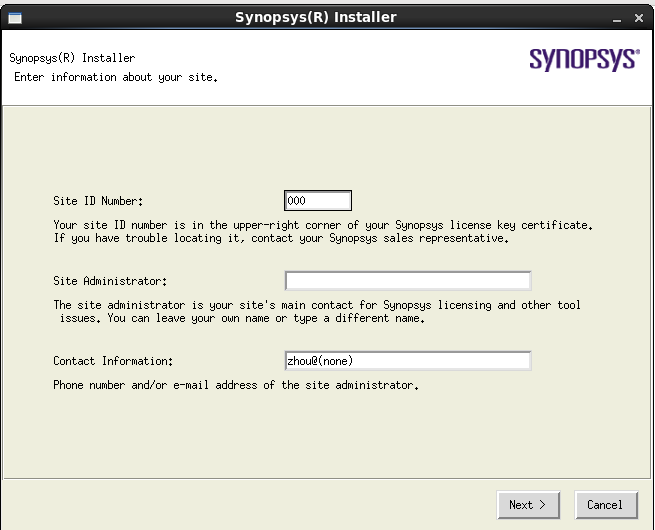

第三步:运行./setup.sh 启动Installer

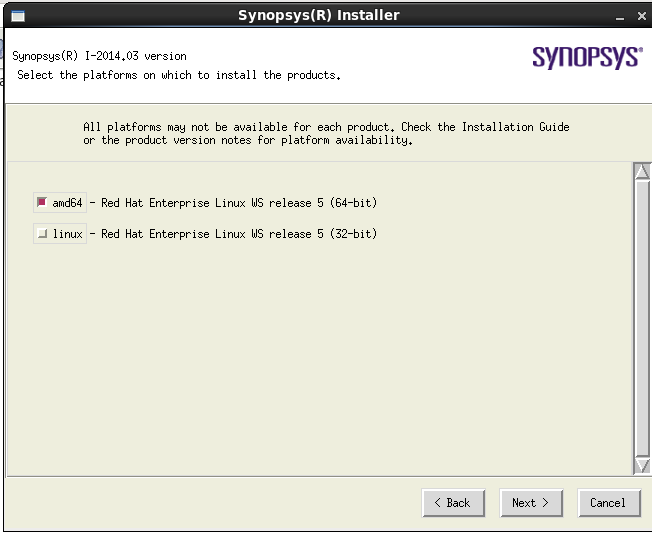

Next至下图,选择amd64

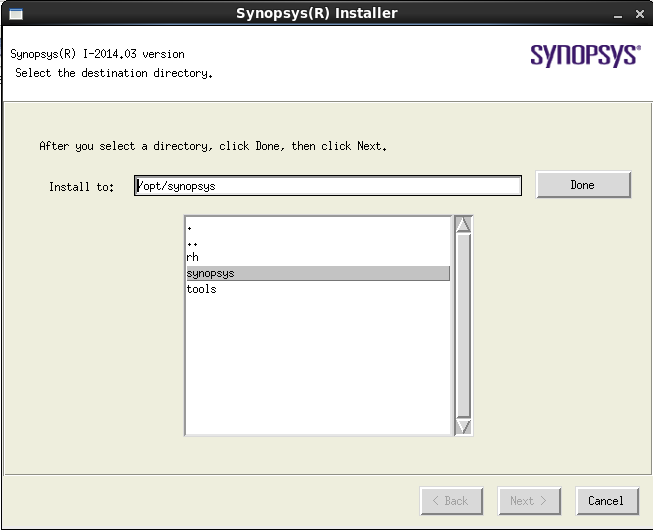

Next至下图,建议选择如下安装路径,因为我自己安装的是这个,可以直接复制.bashrc文件

Next到左后选择Install等待几分钟即可安装完成之后,以同样的方法的方法安装scl

四、license

网上有很多license破解方法,eetop随便搜一下,出来的就能用,涉及知识产权在此不做介绍。(出现问题可建议文章最后微信)

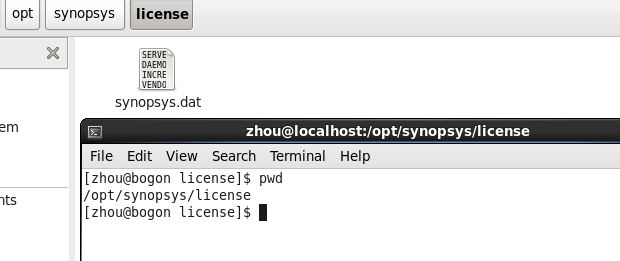

将产生的license文件synopsys.dat存放至

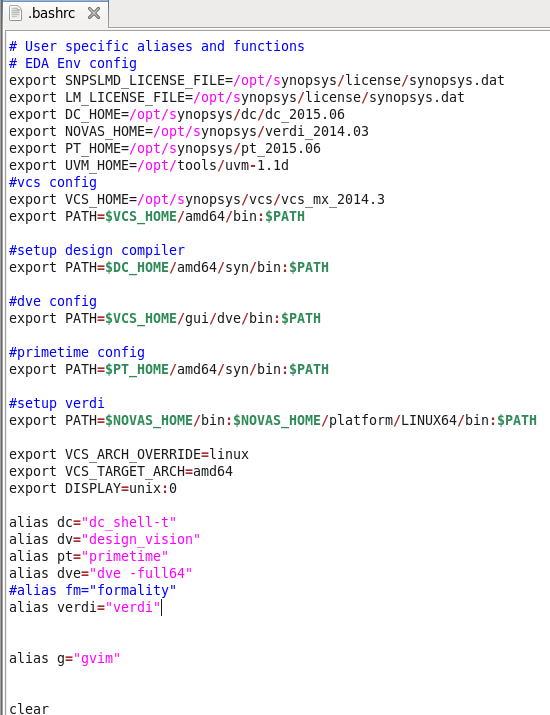

五、环境变量配置

到此为止,你的VCS就能正常启动的

六、测试VCS

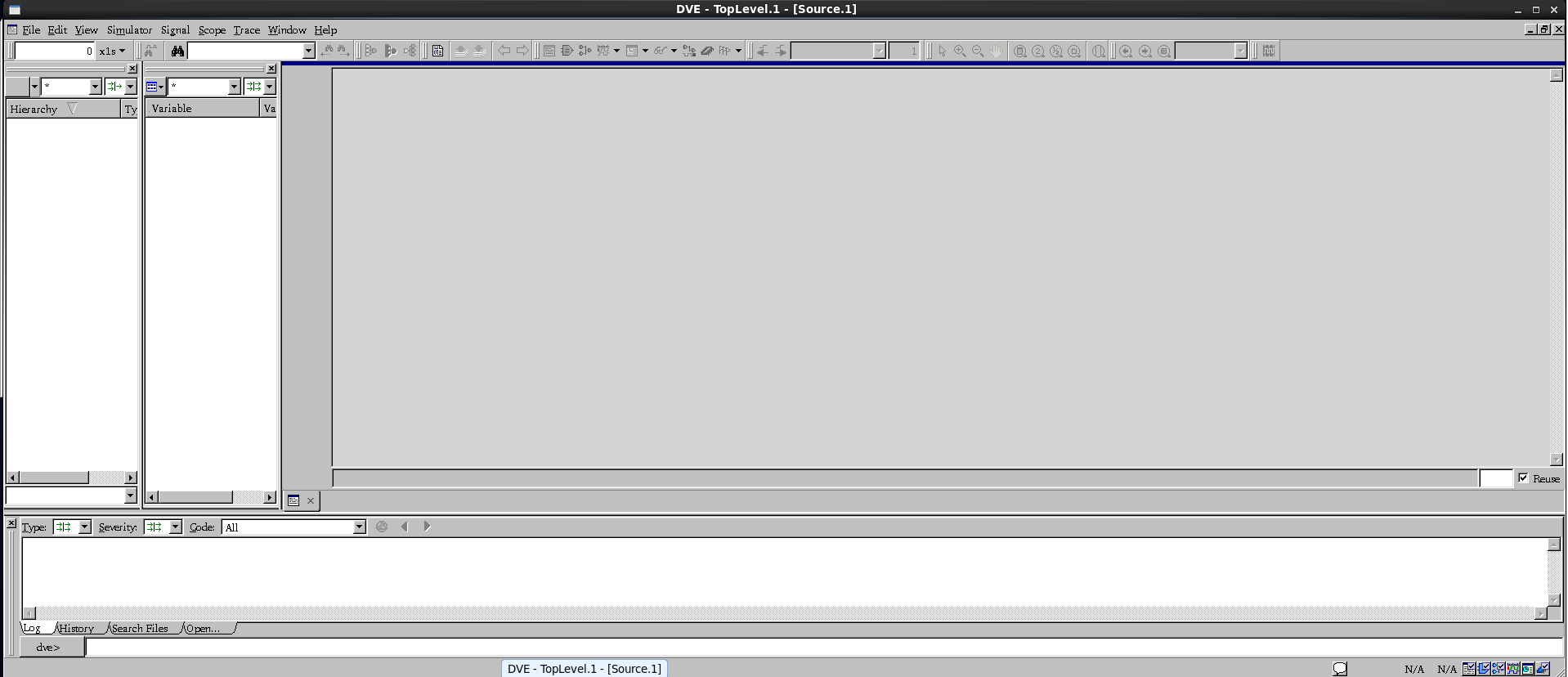

1、先在terminal输入dve,如果能启动图形界面基本上没什么问题

- 命令操作测试

(1)找到一个简单的verilog程序以及对应的testbench,在此贴出网上找的两个程序

timescale 1ns/1ns

module a(cout,sum,ina,inb,cin);

output[3:0] sum;

output cout;

input[3:0] ina,inb;

input cin;

assign {cout,sum}=ina+inb+cin;

endmodule

`timescale 1ns/1ns

module tb_a; //测试模块的名字

reg[3:0] a,b; //测试输入信号定义为reg型

reg cin;

wire[3:0] sum; //测试输出信号定义为 wire型

wire cout;

integer i,j;

a adder(sum,cout,a,b,cin); //调用测试对象

always #5 cin=~cin; //设定 cin的取值

initial

begin

a=0;b=0;cin=0;

for(i=1;i<16;i=i+1)

#10 a=i; //设定 a的取值

end

initial

begin

for(j=1;j<16;j=j+1)

#10 b=j; //设定 b的取值

end

$monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum);

#160 $finish;

end

endmodule

(2)把这两个.v程序copy到任意文件夹在,在该文件夹打开terminal

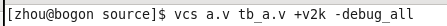

运行 vcs a.v tb_a.v +v2k –debug_all

运行结束之后文件夹中多了几个文件,如下图。

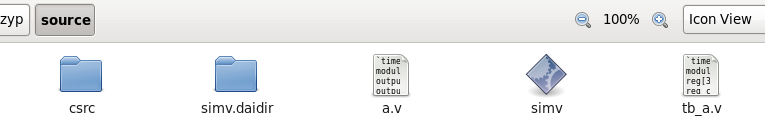

运行./simv -gui

显示如下:

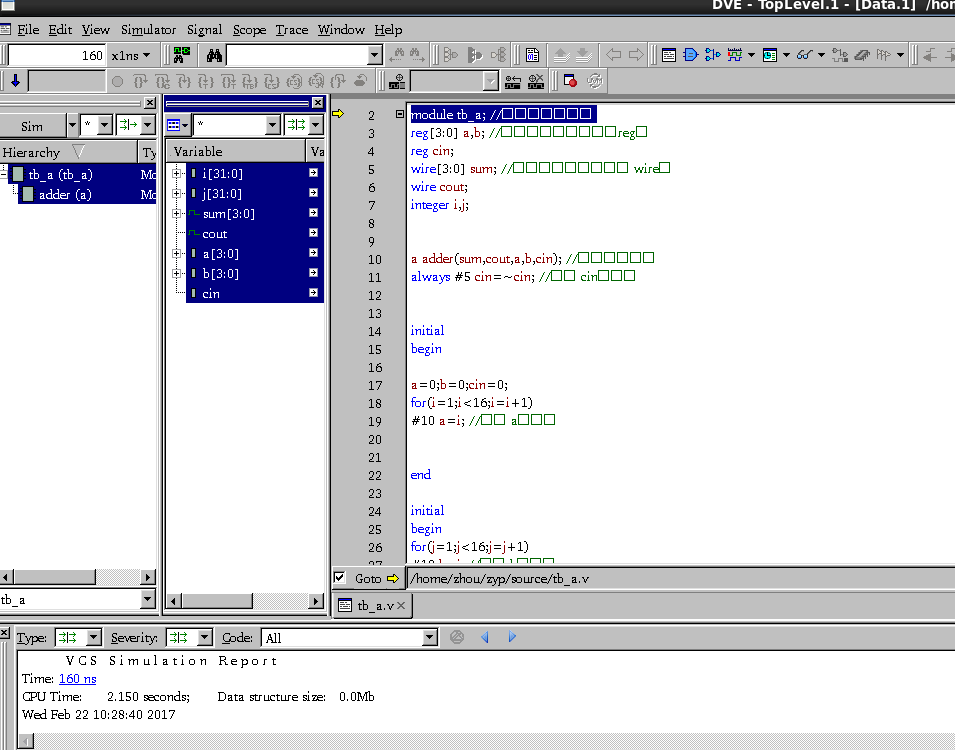

加入波形

到此为止,VCS确认成功安装

转自http://www.eecourse.com/group/7/thread/267

/1

/1

eetop公众号

eetop公众号 创芯大讲堂

创芯大讲堂 创芯人才网

创芯人才网